Intel Sapphire Rapids: Architektur und Aufbau der Next-Gen-Xeon-CPUs

Alder Lake ist das große Ding für Notebook, im Server wird Sapphire Rapids aber noch wichtiger. Intel offenbart weitere Details die zeigen, dass es sich für den Konzern vermutlich wirklich um das wichtigste Projekt handelt. Denn hier steht für die Zukunft viel auf dem Spiel.

Nach Jahren in Arbeit, der Codename Sapphire Rapids geistert schon seit einer halben Dekade herum, nähert sich die nächste Generation Server-Prozessoren endlich der Fertigstellung. Anfang 2022 soll sie in Produktion gehen und den neuen Standard und Grundlage für die kommenden Jahre markieren.

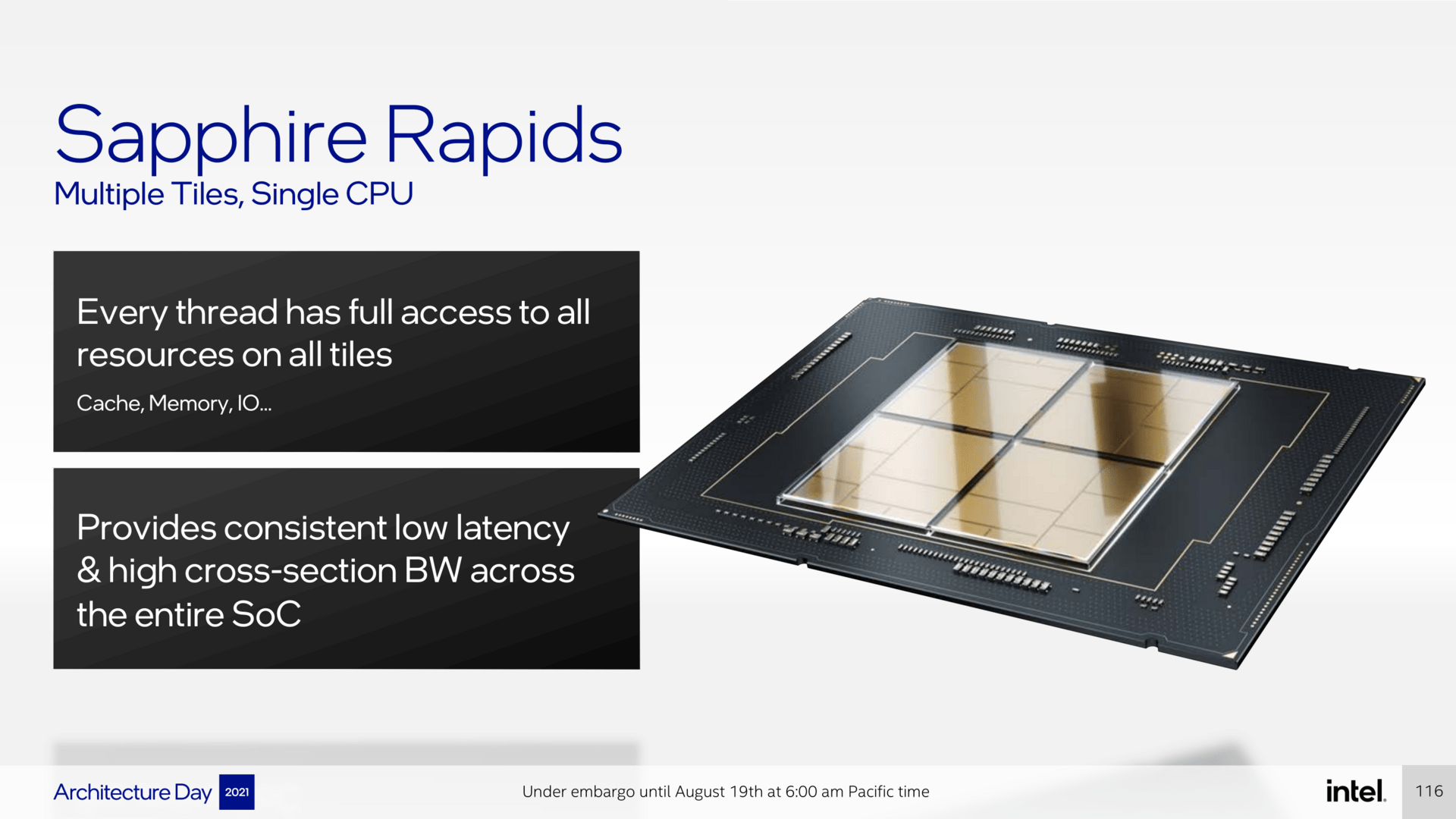

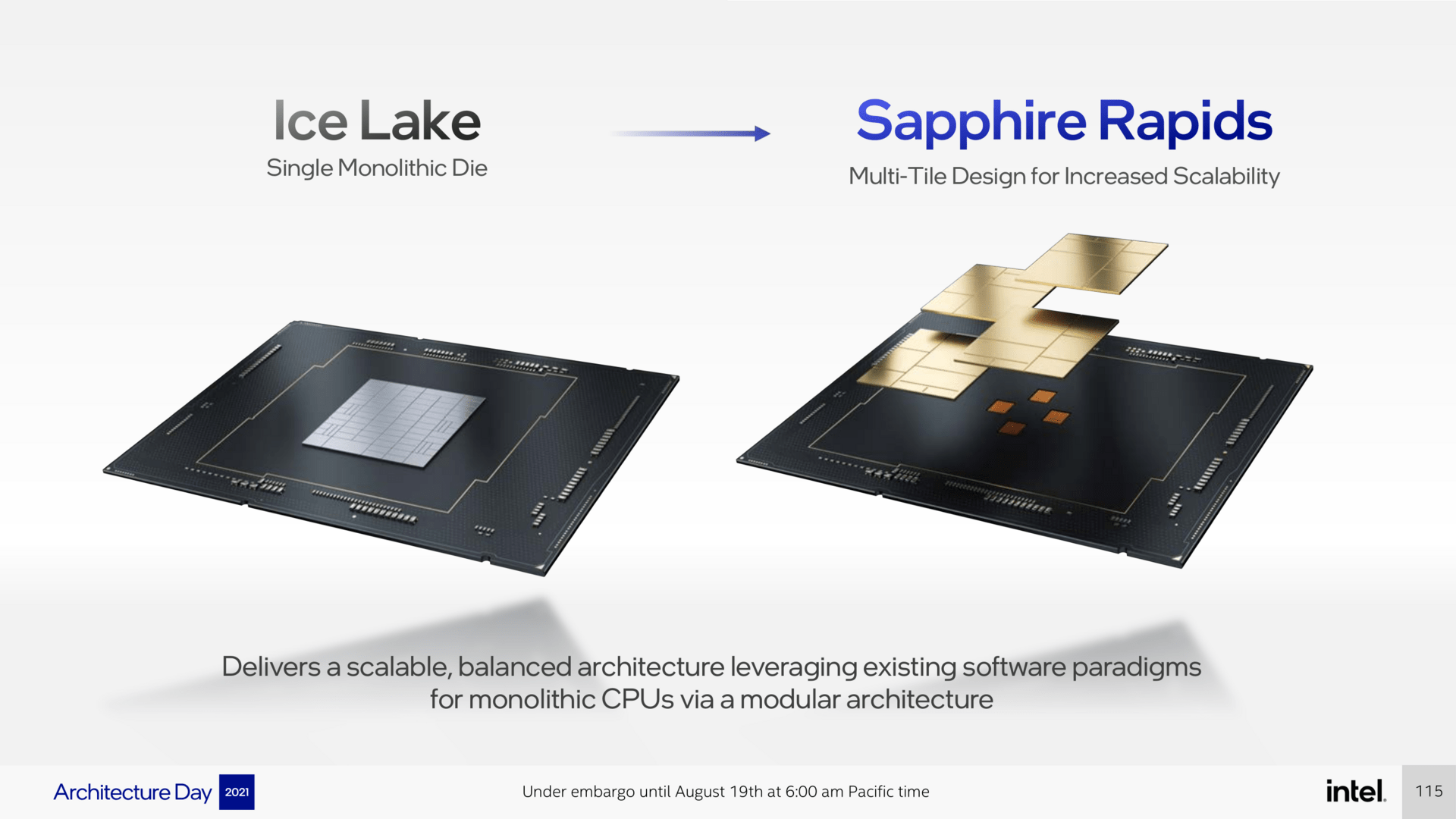

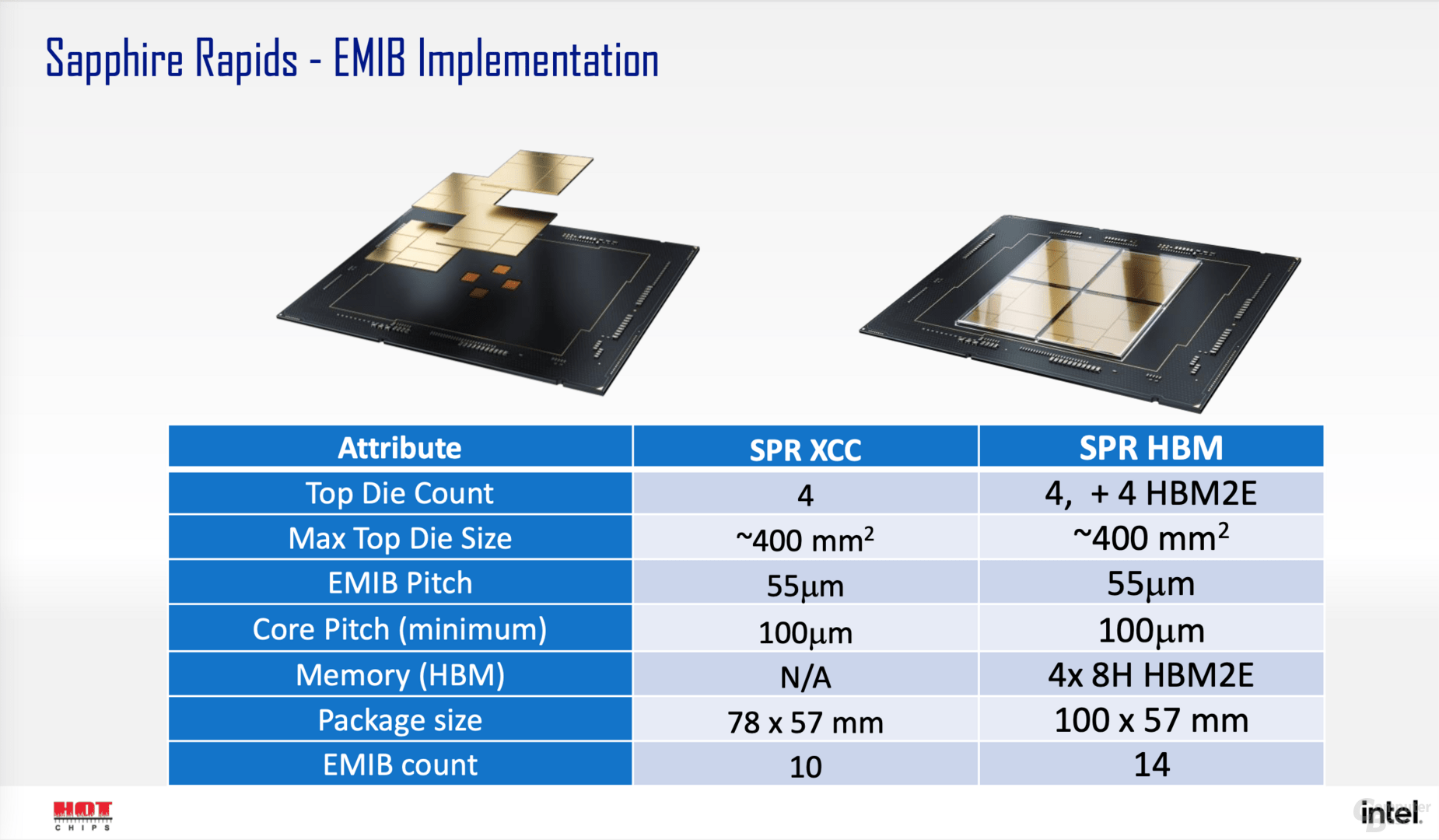

Sie stehen für den Wechsel bei Intel vom klassischen monolithischen CPU-Design hin zu einer Multi-Chip-Lösung, die Intel in den Ausführungen jeweils „Tiles“ nennt. Erst die Aufgabe der klassischen Herangehensweise ermöglicht mehr Kerne, mehr und neue I/O, Unterstützung für schnelleren Speicher und HBM, soll jedoch ohne große Nachteile von Multi-Chip-Designs daherkommen. Dafür sorgen soll EMIB, Intels bereits seit Jahren bekannte Interconnect-Technologie, die kurze Wege direkt auf dem Package überbrückt und hohe Bandbreite bei sehr geringen Latenzen bietet. Sie stellt sicher, dass jeder Tile Zugriff auf alle Ressourcen hat.

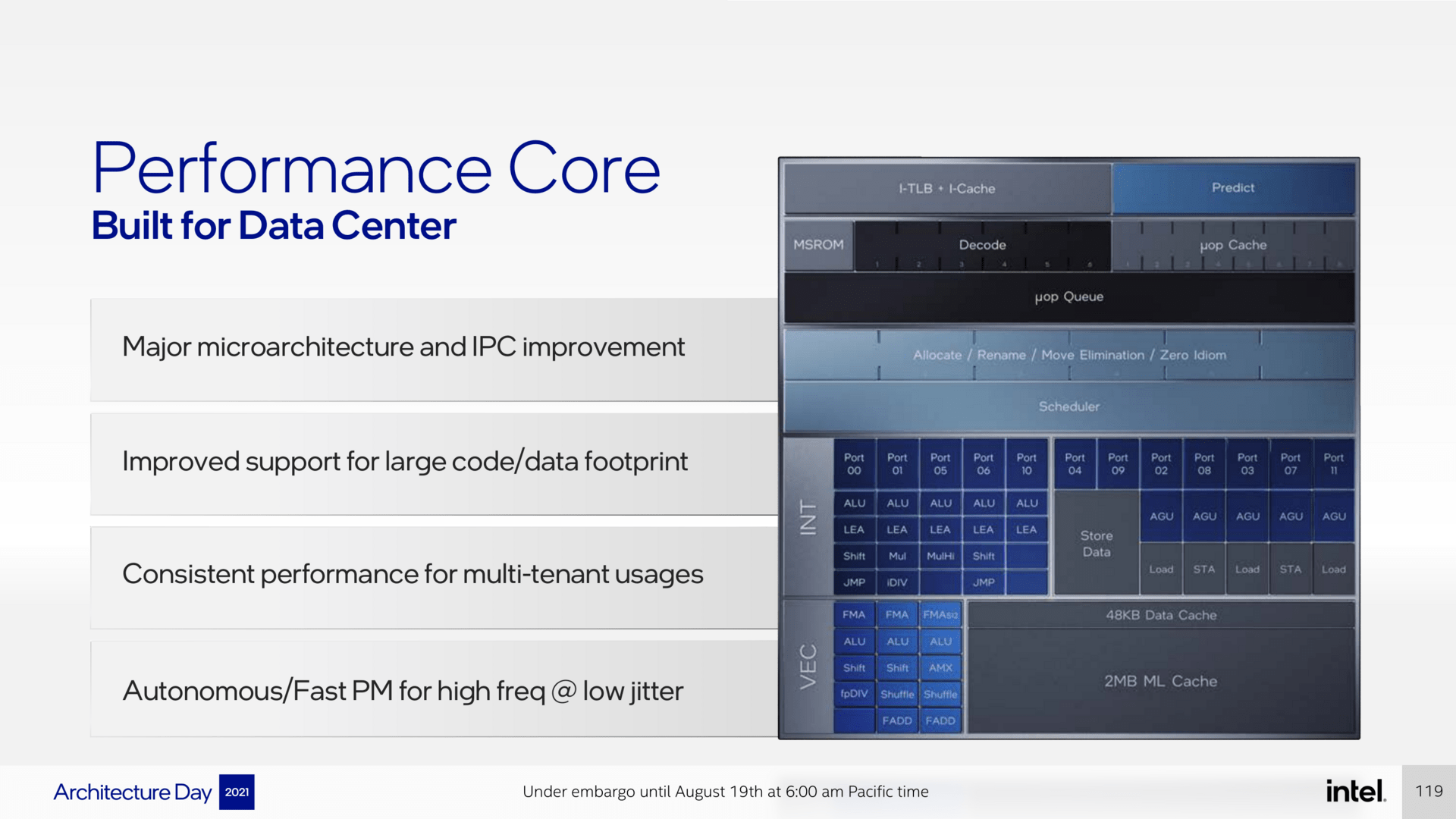

Der neue Golden-Cove-Kern im Vollausbau

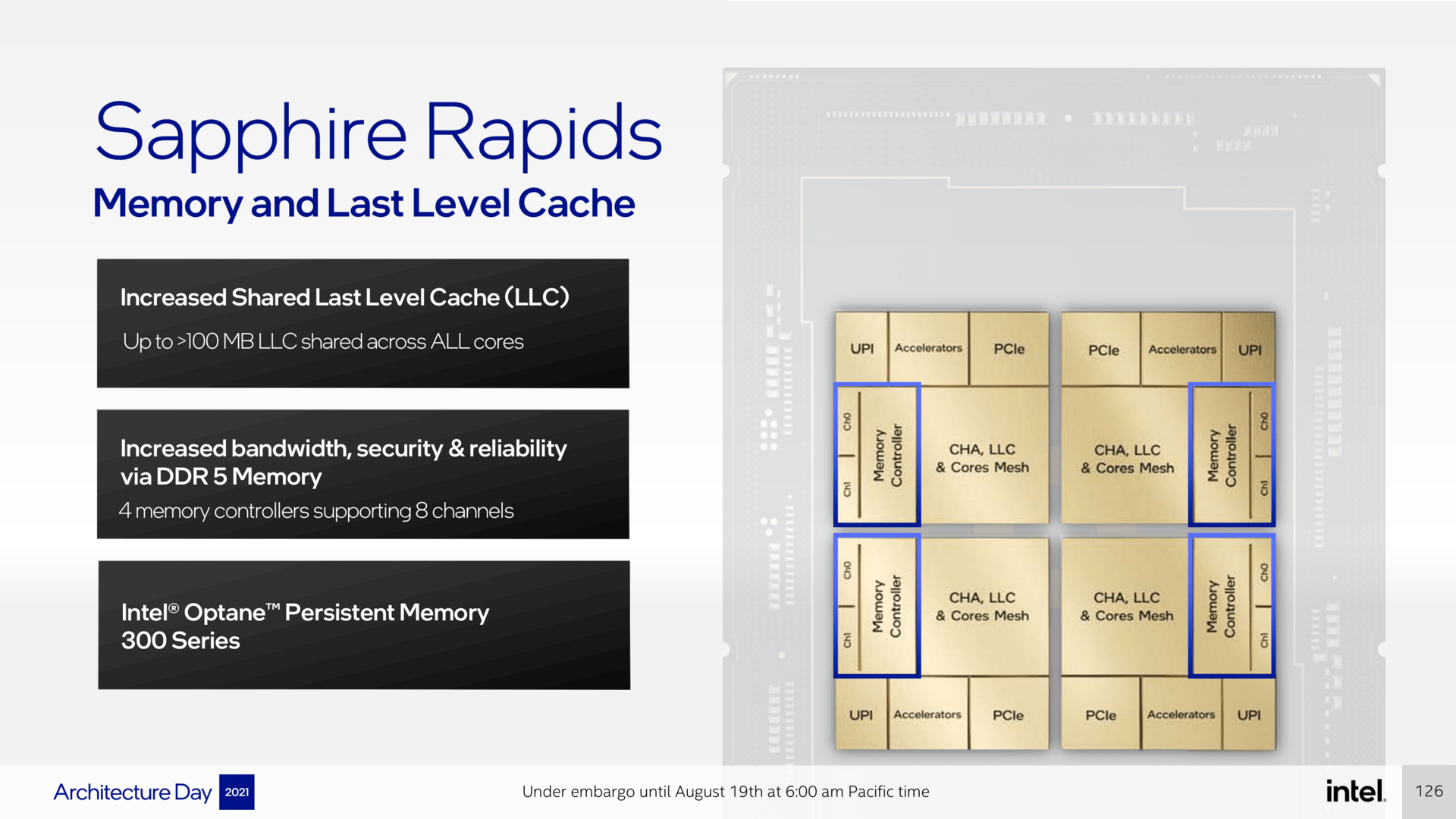

Basis für alle neuen Xeon-SP der nächsten Generation wird der big core, Codename Golden Cove. Die grundlegenden Features sind identisch mit der Variante, die in Alder Lake als P-Core ihre Premiere feiert, im Datacenter darf der neue Kern aber 2 MByte L2-Cache aufbieten – pro Kern versteht sich. Die vermutlich knapp 60 Kerne im Maximalausbau bieten also insgesamt über 100 MByte L2-Cache auf, hinzu kommt ein Last-Level-Cache, auf den alle Kerne zugreifen können, der ebenfalls über 100 MByte groß sein darf. Cache ist zweifelsohne Trumpf geworden in den letzten Jahren bei AMD und Intel.

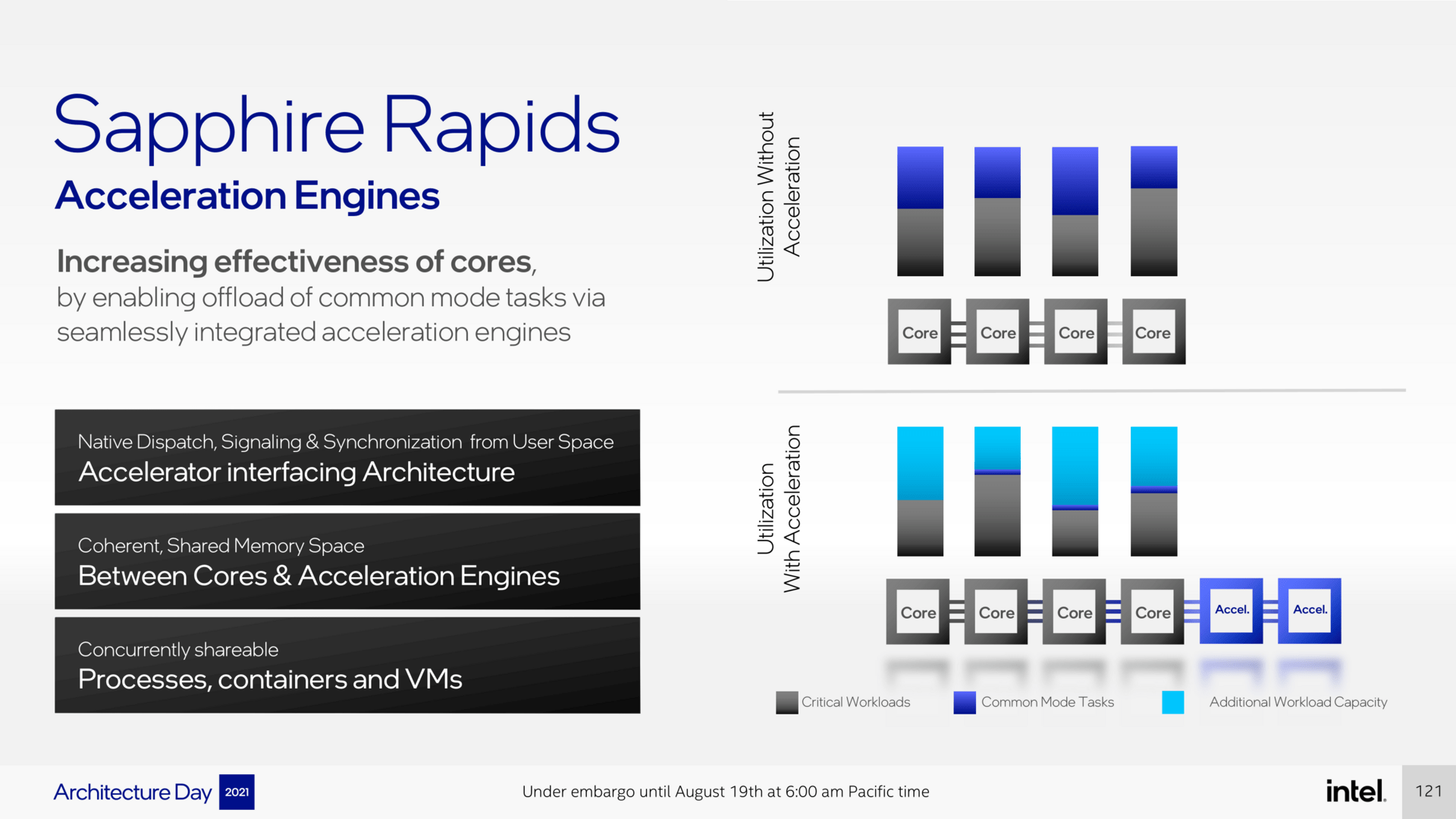

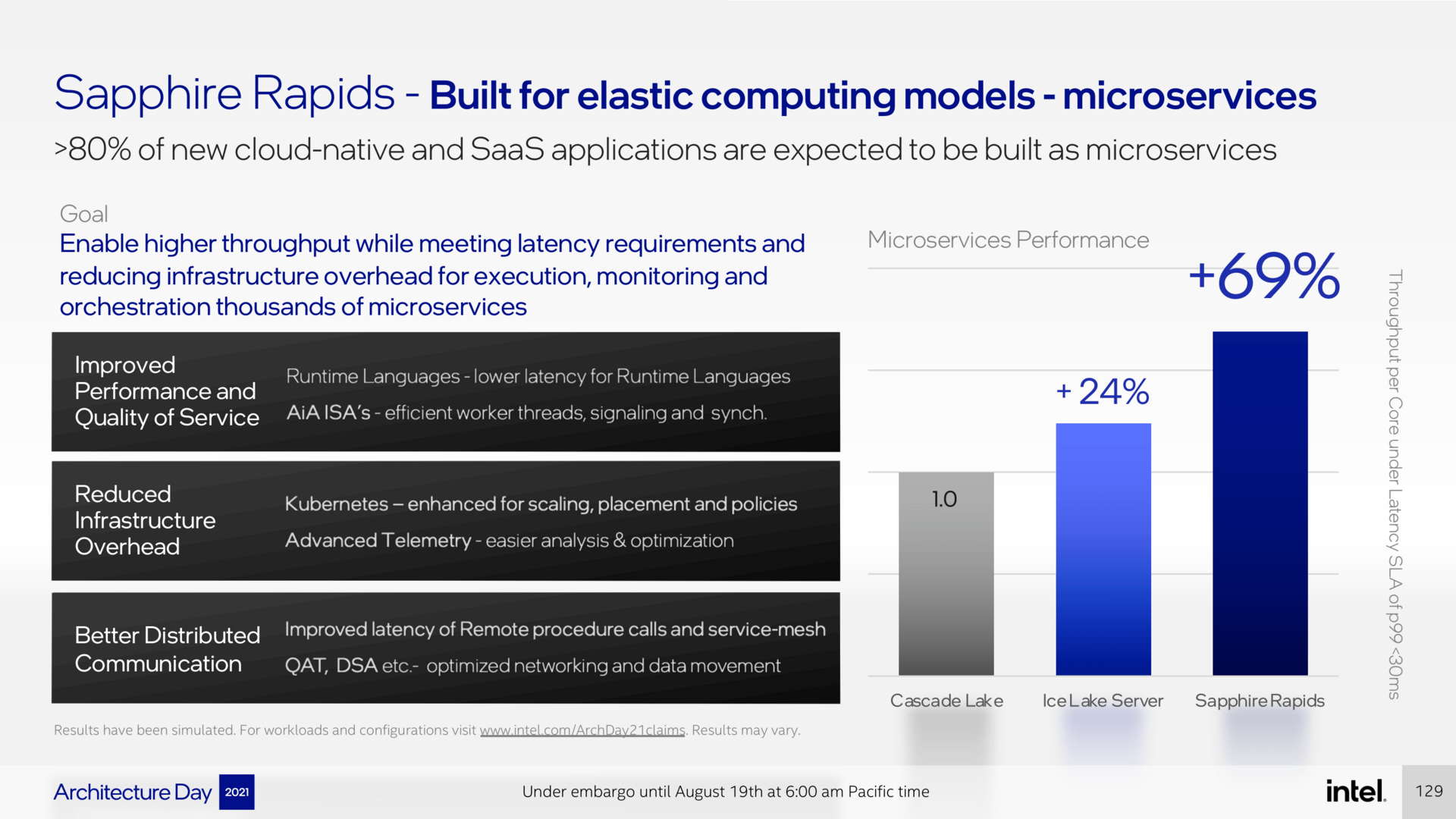

Zur Geltung kommen im Profi-Bereich aber die Features, die im Desktop und Notebook zwar interessant sind, aber vor allem zu Beginn kaum Relevanz haben dürften. AMX, die neuen Advanced Matrix Extensions, sind hier ein Beispiel, aber auch integrierte Technologien, die sich mehr um die Ansteuerung der einzelnen Kerne und Overhead in gewissen Szenarien kümmern. Dies ist ein großes Problem in Cloud-Datacentern, in denen viele Server mit Nebensächlichkeiten beschäftigt sind, statt ihrer eigentlichen Aufgabe nachzukommen.

Das Drumherum um die CPU-Kerne wird auf den Standard der nächsten Generation gehoben. PCI Express 5.0 ist mit dabei, aber auch CXL nach Standard 1.1 hält nun erstmals in Prozessoren Einzug. Neben einem Acht-Kanal-Speicherinterface für DDR5 wird auch HBM unterstützt, natürlich auch die nächste Generation an Optane Memory.

Für die Kommunikation mit anderen Systemen wurden die UPI-Links auf einen neuen Standard aufgewertet, 16 GT/s schaffen sie nun, zudem sind vier davon pro Prozessor zu finden. Das soll auch zur Skalierbarkeit in Rechenzentren helfen, 8-Sockel-Systeme werden nach wie vor maximal unterstützt. Hier ist Intel seit Jahren einziger Anbieter von CPUs, AMD fokussiert sich nur auf den Dual-Sockel-Markt, der jedoch zweifelsfrei der größte ist.

Das Gesamtpaket soll am Ende großes leisten, verspricht Intel. Erneut hebt der Hersteller hierbei hervor, dass es nicht nur um Prozessorkerne geht – der Wink mit dem Zaunpfahl in Richtung AMD – sondern das komplette Paket. Zur Schau stellt man deshalb ein Bild der Leistung eines neuen Kerns gegenüber den letzten beiden Generationen, das die Leistung unter sehr geringer Latenz zeigt. Hier sollen die neuen Lösungen noch deutlich performanter sein, als es die 19 Prozent IPC-Steigerung von Golden Cove gegenüber den Vorgängerkernen zeigen. Wie das am Ende unabhängig aussieht, wird sich in knapp einem Jahr offenbaren.

Zur Eröffnung von Hot Chips 33 hat Intel am Sonntag weitere kleine Einblicke in Sapphire Rapids in Bezug auf das Packaging gegeben. Demnach sind zehn EMIB-Verbindungselemente unter den einzelnen Chips in einem normalen Modell zu finden, kommt HBM hinzu, werden es insgesamt 14 – und das auf deutlich größerem Package. Die Angaben garniert Intel mit einigen Zahlen, die die Vorteile des Tile-Ansatzes untermauern: Die CPU-Kerne sind zusammen nur 400 Quadratmillimeter groß, das ganze Package für die Variante ohne HBM etwas kleiner. Weitere Details zum Intel-Packaging und auch Sapphire Rapids von der Hot Chips 33 gibt es im Laufe der kommenden beiden Tage.

ComputerBase hat die Informationen im Rahmen des Architecture Day 2021 von Intel vorab auf einem Event in Berlin unter NDA erhalten. Eine Einflussnahme des Herstellers auf die Berichterstattung fand nicht statt, eine Verpflichtung zur Veröffentlichung bestand nicht. Einzige Vorgabe war der frühestmögliche Veröffentlichungstermin.

- Hot Chips 33: Samsung zeigt HBM-PIM und riesige Speichermodule

- Hot Chips 33: IBMs Telum-Architektur setzt auf 32 MB L2-Cache – pro Kern

- Hot Chips 33: Intel Alder Lake steht und fällt mit dem Thread Director

- +7 weitere News