Ponte Vecchio: Intels HPC-Grafiklösung wird ein Monster

Intel im HPC-Segment stand bisher für Prozessoren, sonst nichts. Ponte Vecchio soll das ändern, technisch ist es ein noch nie dagewesenes Unikat. Vor dem Start im kommenden Jahr gab Intel noch einmal einige zusätzliche Einblicke, was erwartet werden kann.

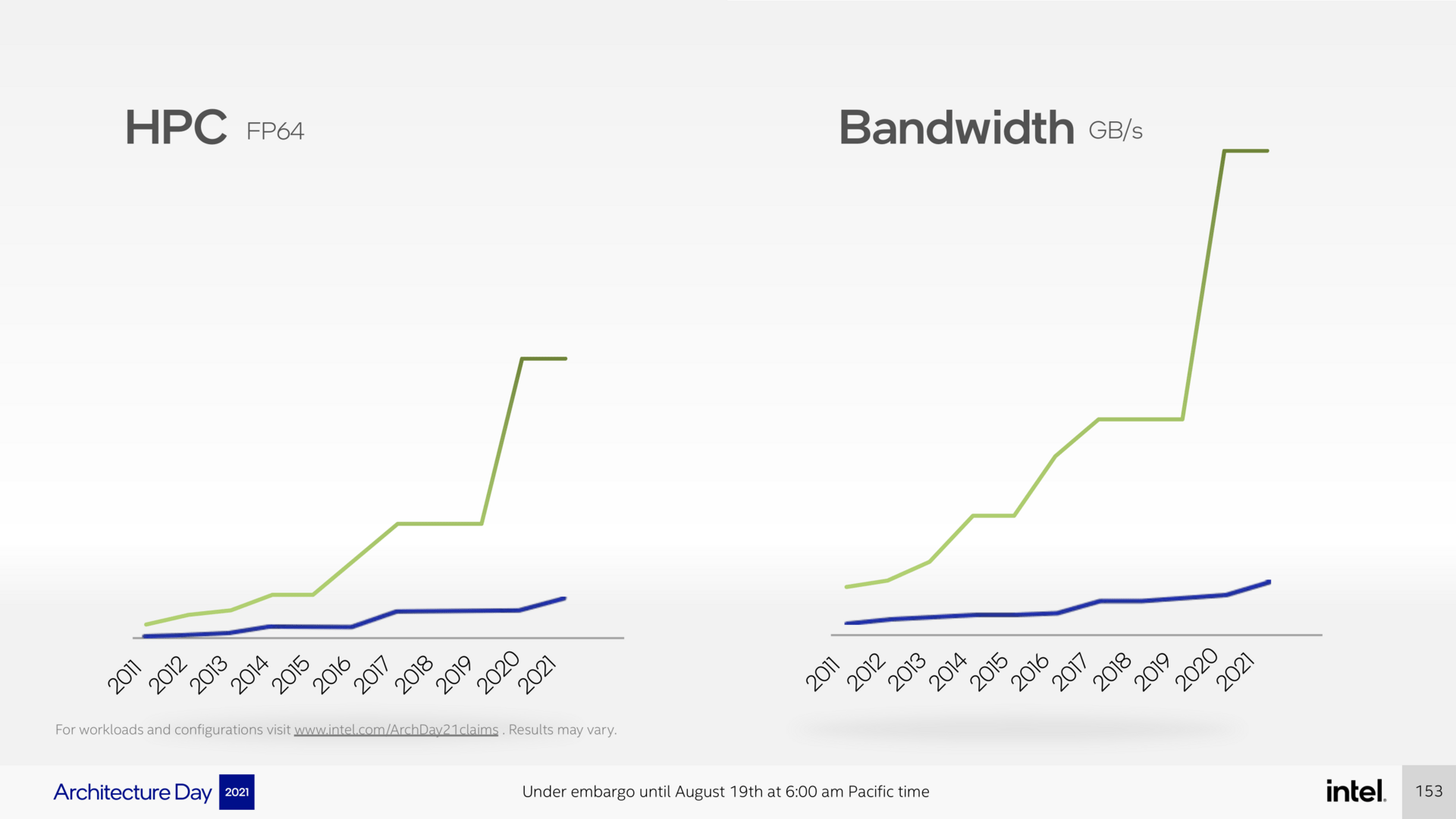

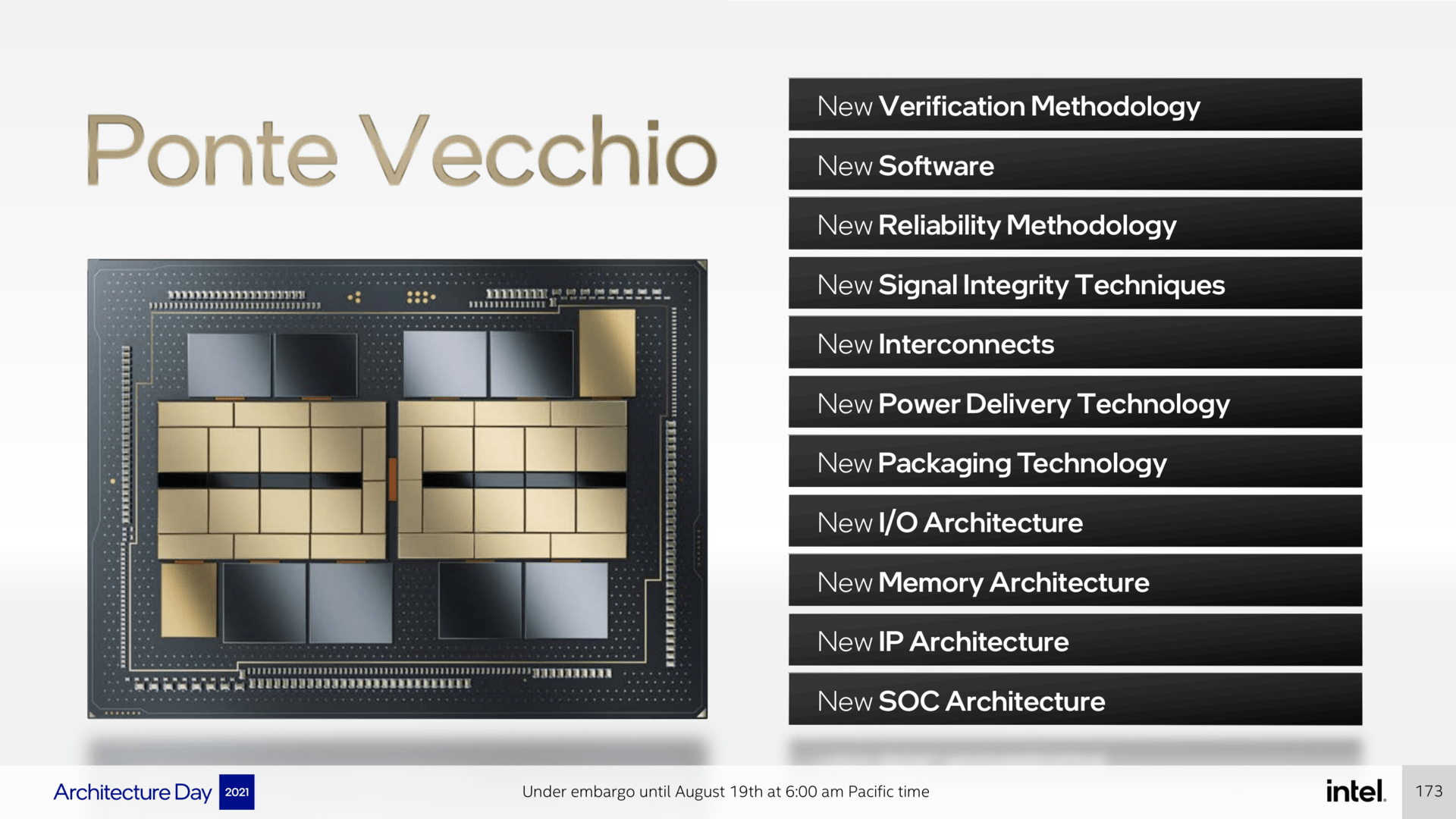

Viele Informationsschnipsel aber auch Guerilla-Marketing haben zuletzt immer wieder kleine Details zu Ponte Vecchio dargelegt. Denn an Intels Versuch, Nvidia im Datacenter Paroli zu bieten, hängt für Intel viel ab. Wie sie selbst sagen, haben sie den Trend bisher nicht nur ein wenig, sondern fast komplett verschlafen. Jahrelang konnte sich Nvidia an der Spitze sonnen, doch genau das will Intel mit einem Paukenschlag ändern. Die Präsentationsfolie sorgte in ihren Schritten im Rahmen einer Veranstaltung in Berlin deshalb durchaus für einen Lacher – insbesondere der letzte, indem Intel alles in den Boden stampfen will.

Intel Xe HPC ist die Grundlage

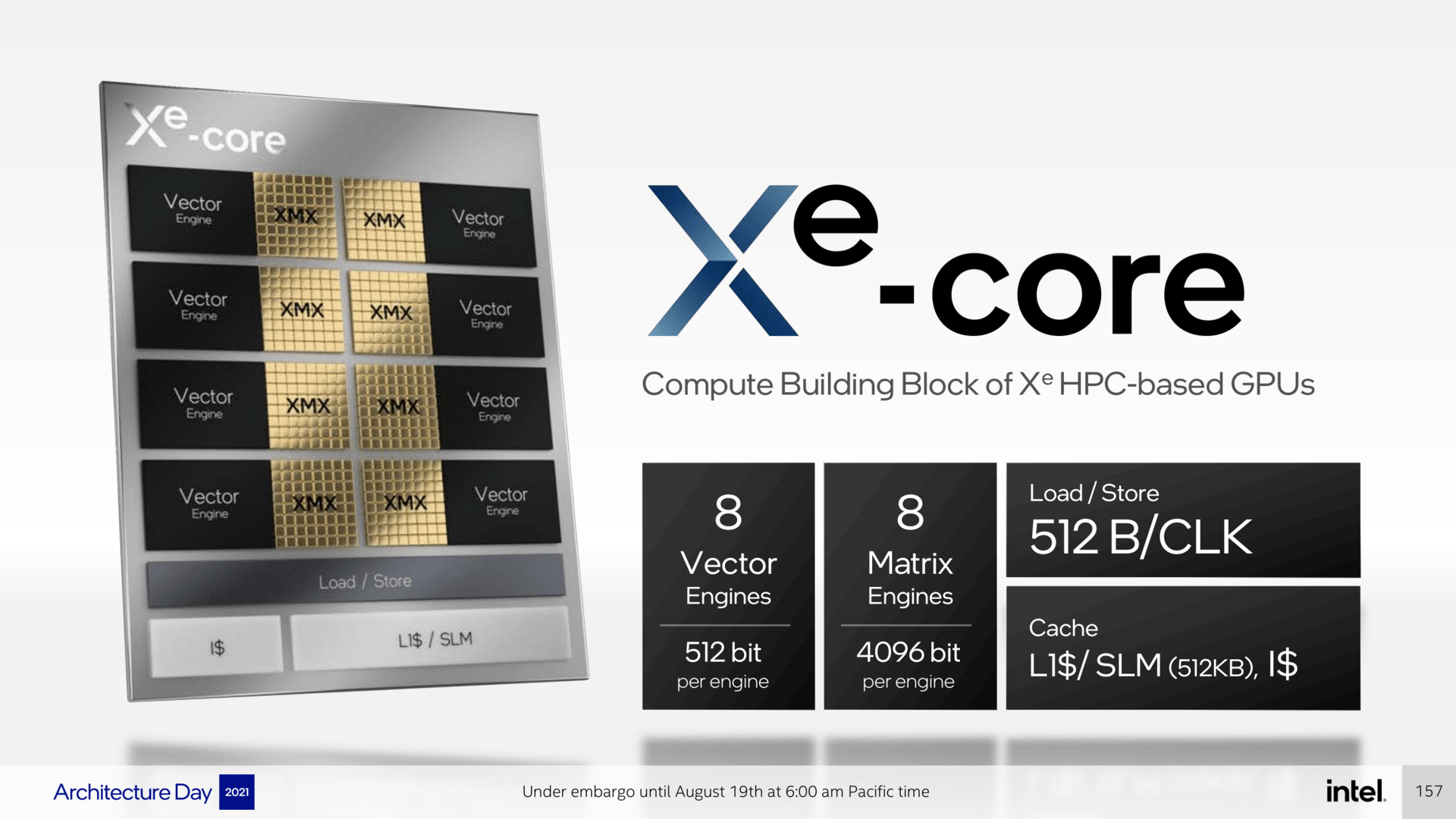

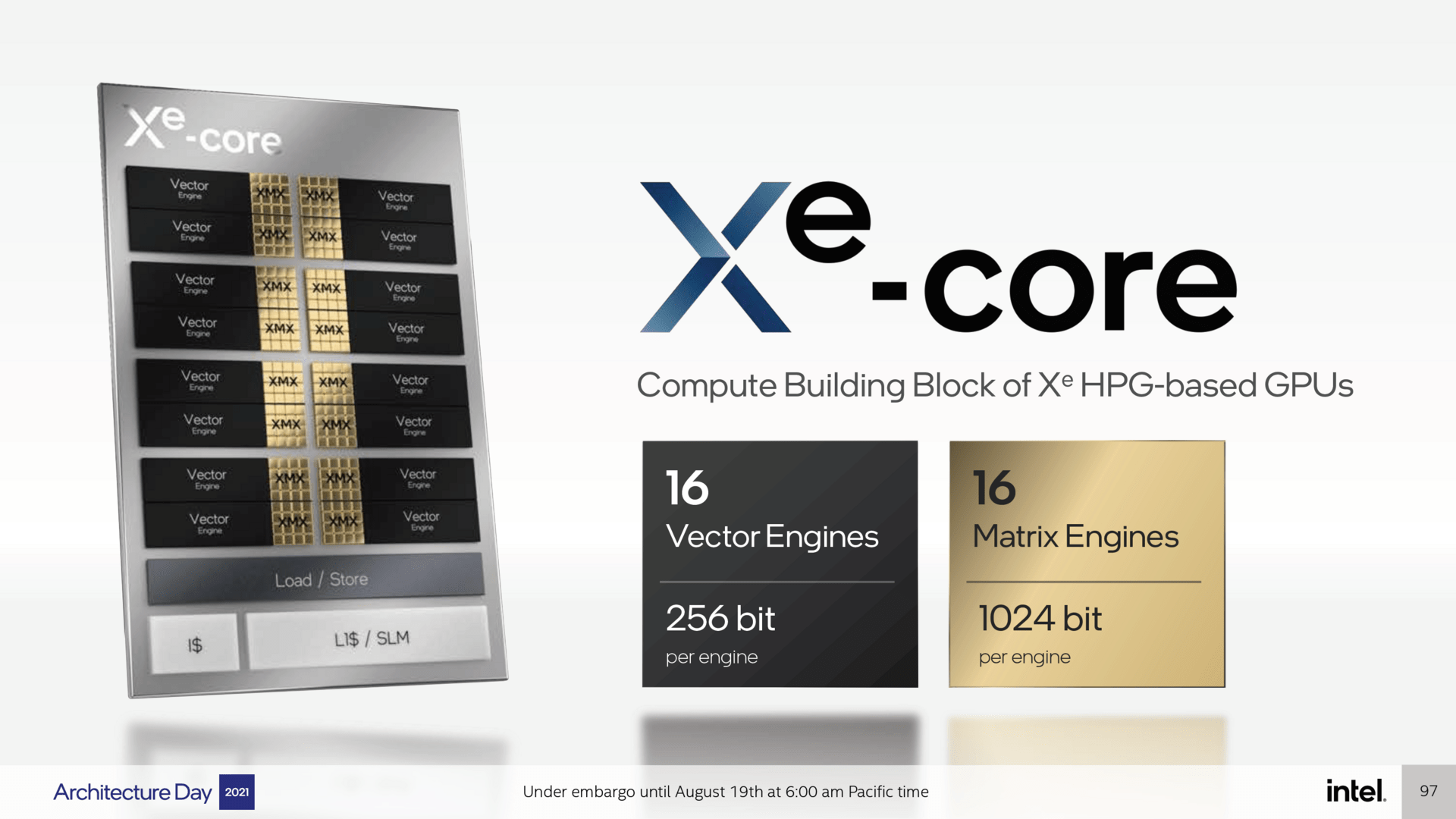

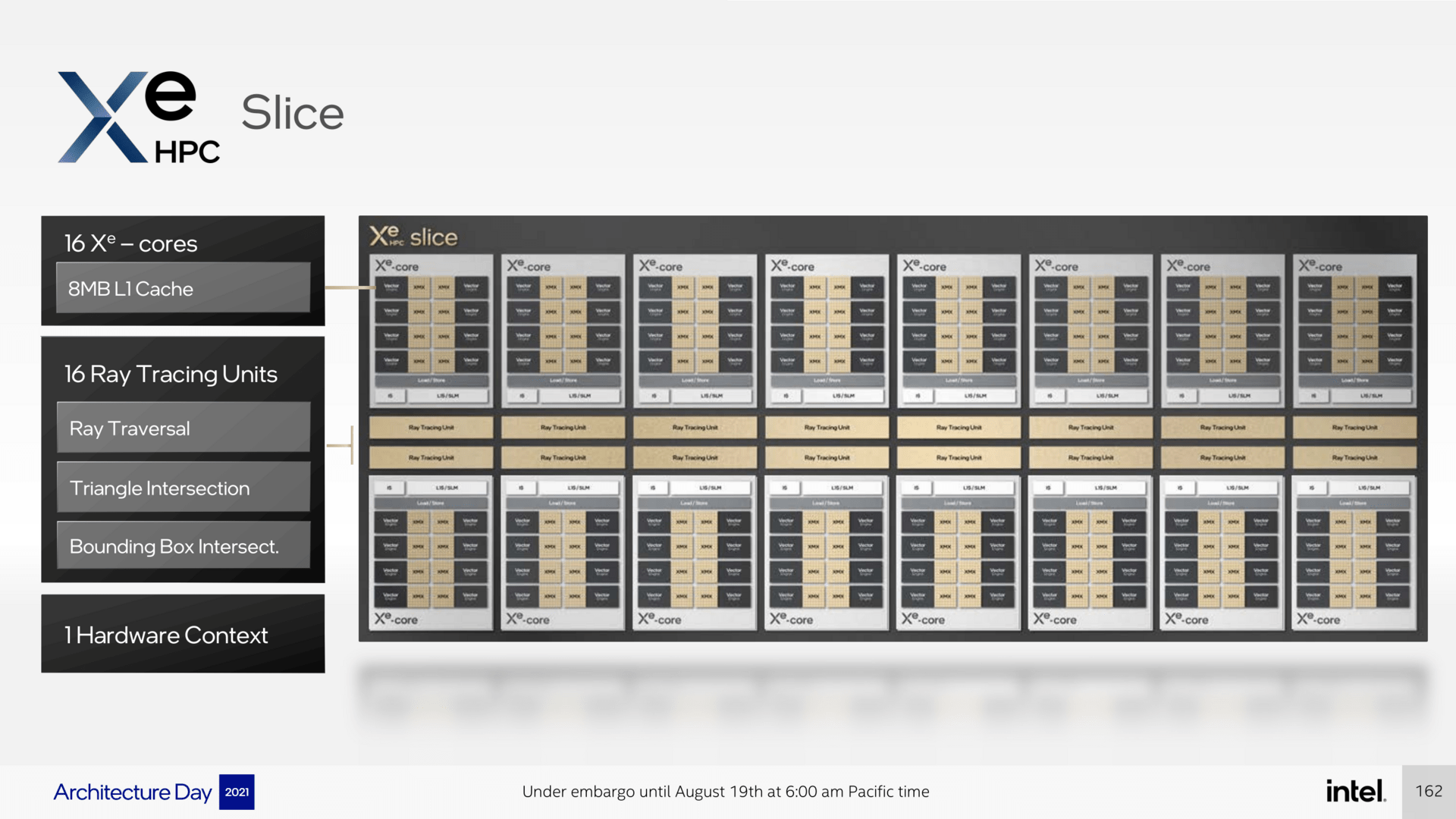

Das Herzstück der Bemühungen ist der Xe-Grafikkern, wie Intel die Einheiten seit heute nennt. Dieser unterscheidet sich im Profi-Bereich aber von dem aus den Desktop-Lösungen, wenngleich überall „Xe Core“ steht. Hier gilt es fortan stets zu beachten, welches Marktsegment denn gemeint ist, denn die Unterschiede sind für das gewählte Anwendungsprofil durchaus beachtlich.

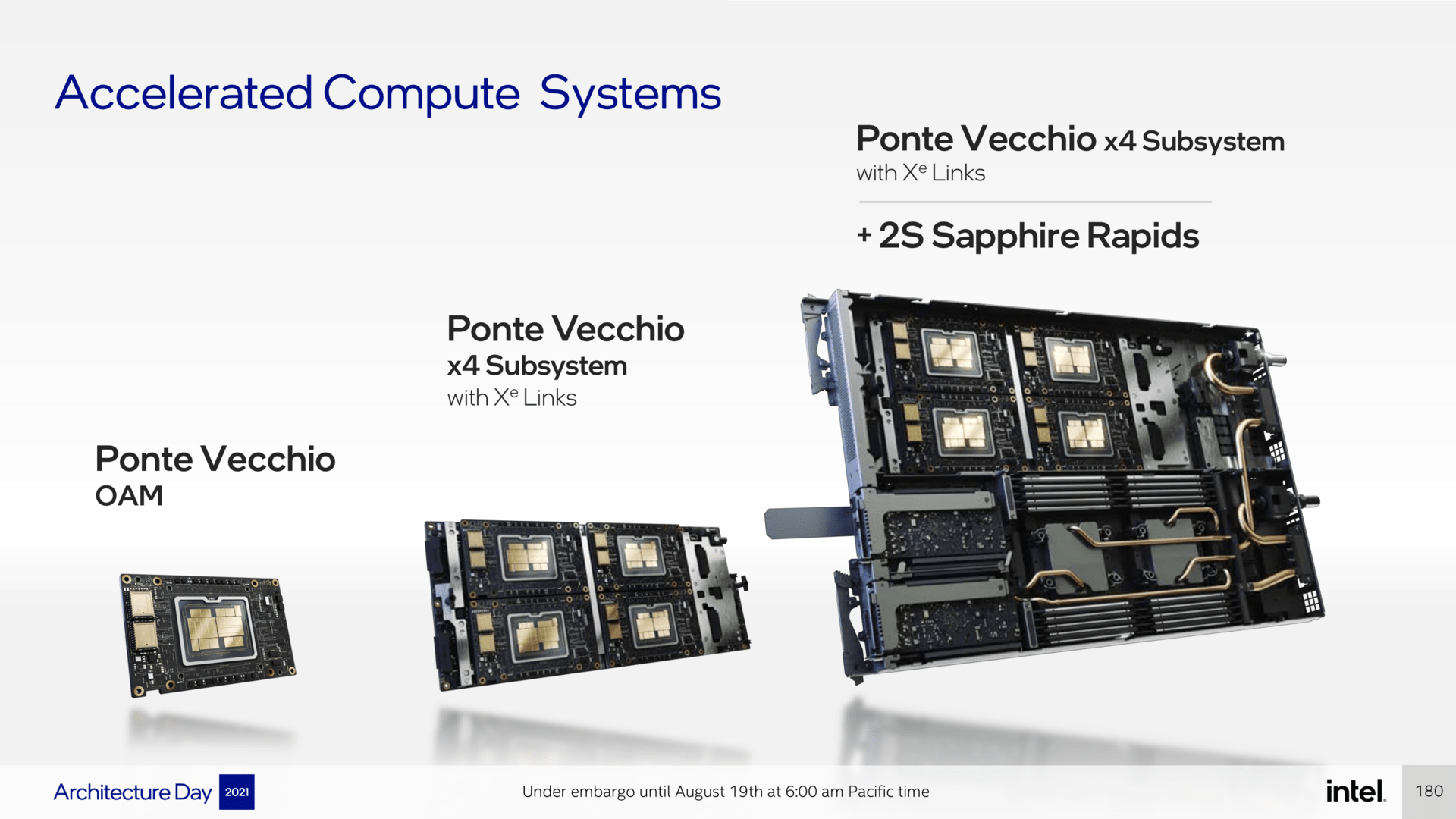

Der Clou wird letztlich ohnehin die Skalierung nach oben, von einem Slice über ein Stack bis hinauf zu acht an der Zahl, die wiederum per Xe Link als neuem Fabric mit anderen kombiniert werden. Damit dies möglichst effizient geschieht, setzt Intel für diese HPC-Chips auf TSMCs N5-Fertigung, die Xe-Link-Tiles wiederum sind von TSMC in N7 gefertigt worden.

Ponte Vecchio für Supercomputer

In Ponte Vecchio soll die HPC-Grafikarchitektur dann erstmals genutzt werden. Doch hier kommt noch viel mehr ins Spiel, auf dem Chip sind 47 verschieden Einzelteile zu finden, die in fünf verschiedenen Fertigungsverfahren sowohl bei Intel als auch extern bei TSMC vom Band laufen. Die große Herausforderung war am Ende, dies alles auf einem Package zusammenzufügen, was laut Intel tausende Leute beschäftigt hat.

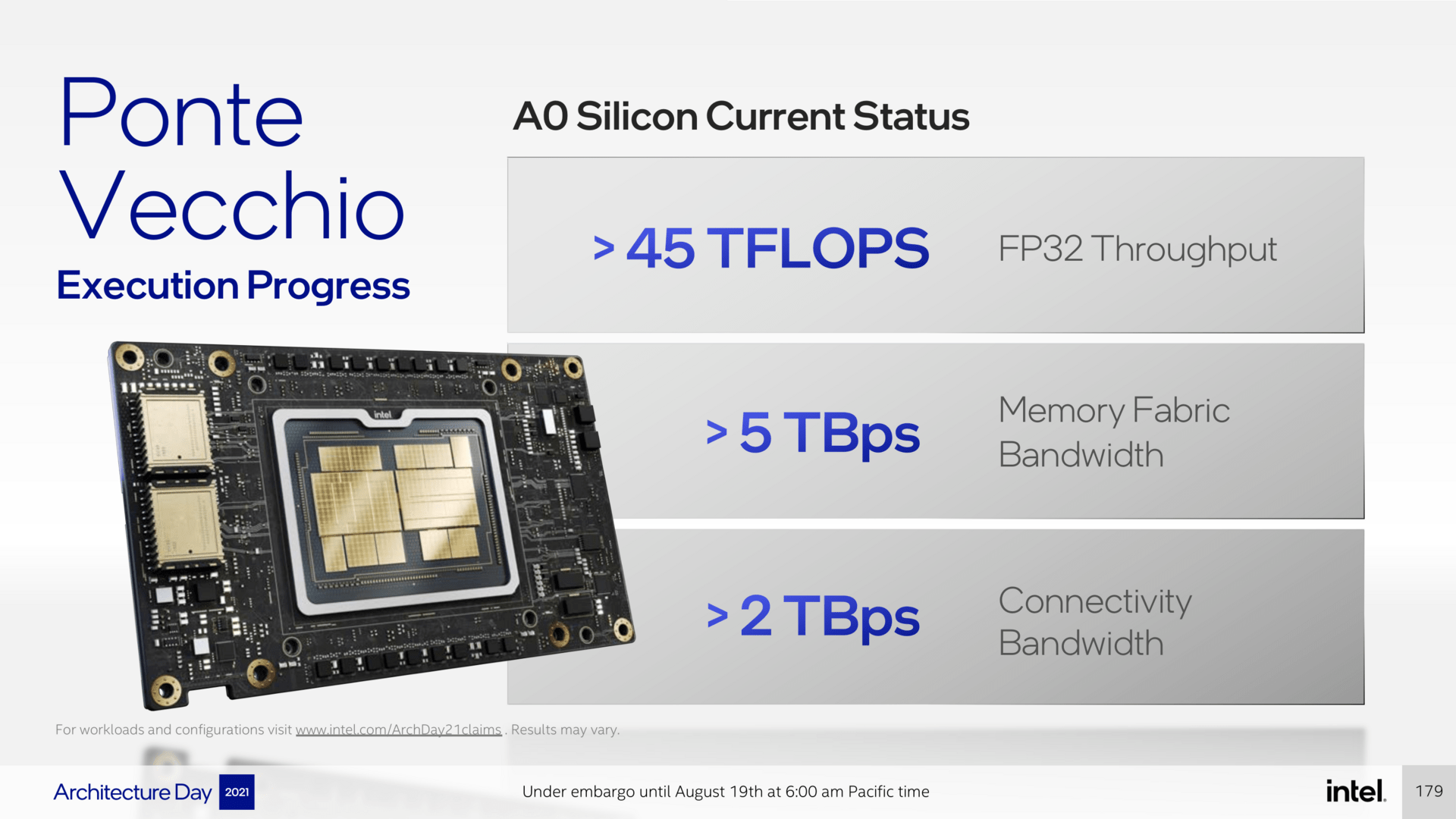

Mit lauffähigen Prototypen wird derweil im Labor am Feinschliff gearbeitet. Das A0-Silizium, wie Intel mehrfach betonte, wurde dadurch zuletzt bereits schneller, statt bisher rund 42 TFLOPs FP32-Leistung, die Intel zuletzt für HPC-Lösungen darlegte, gibt man für Ponte Vecchio nun bereits mehr als 45 TFLOPs an. Nvidias Lösung A100 liefert 19,5 TFLOPS in FP32-Anwendungen. Parallel dazu suchen die Bandbreiten von Intels Produkt in den einzelnen Bereichen ihresgleichen.

Am Ende wird die Zielgruppe der Lösung vermutlich jedoch klein bleiben, Intel will vor allem das Prestige-Projekt rund um den ersten Exascale-Computer antreiben. Wie reguläre Systeme davon profitieren können, wird Intel zum Start im kommenden Jahr darlegen.

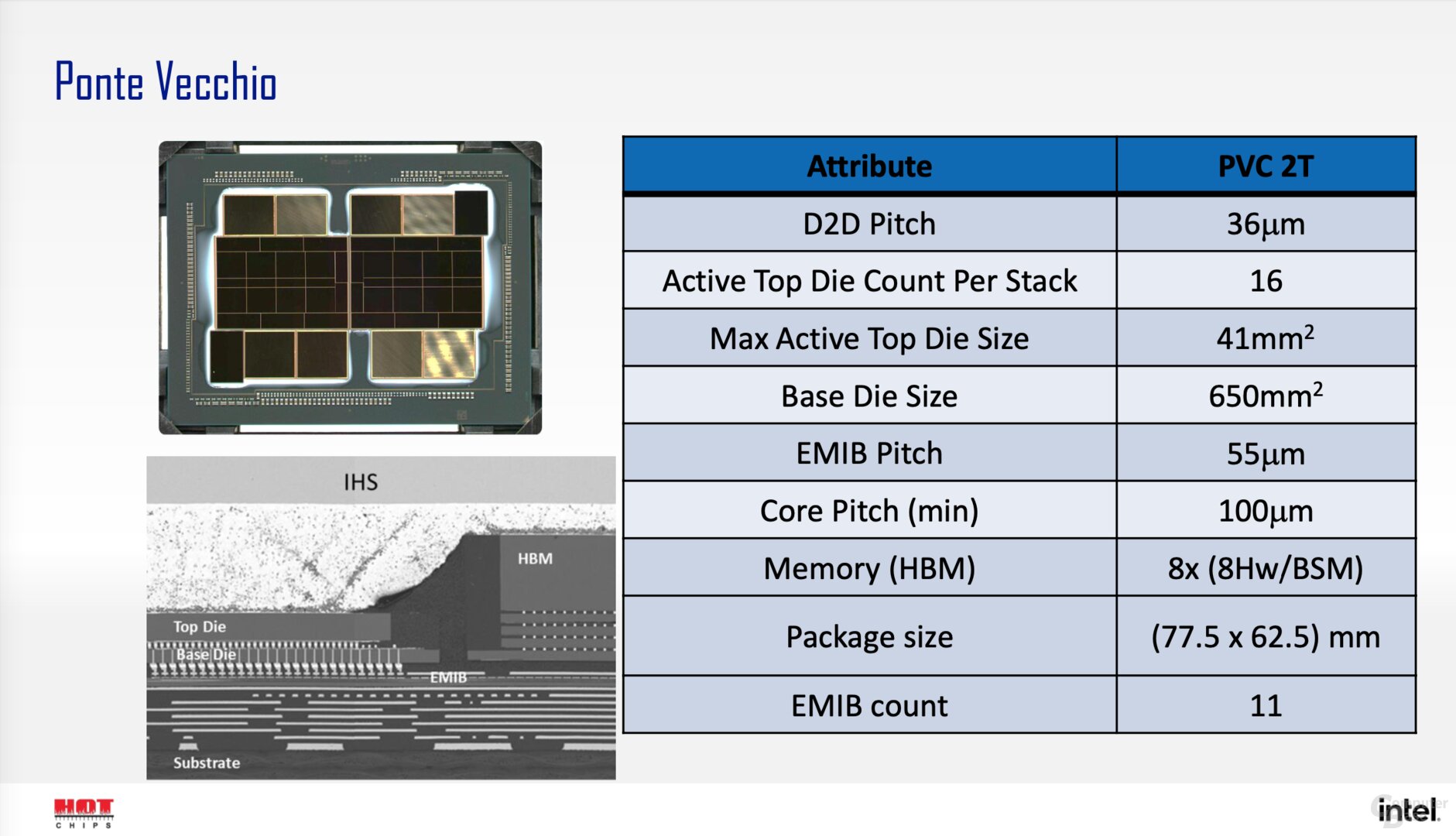

Auch zu Ponte Vecchio gibt Intel zum Auftakt von Hot Chips 33 einige Details zum Packaging preis. Das Gesamtkonstrukt ist, wie bereits gezeigt, sehr groß, doch die eigentlichen Rechenelemente sitzen auf dem verhältnismäßig kleinen, 650 Quadratmillimeter fassenden Base Die, wovon das größte Element darauf wiederum maximal 41 Quadratmillimeter groß ist. Elf EMIB-Verbindungselemente sorgen in der 2D-Ebene für die Kommunikation, Foveros übernimmt dann in der dritten Dimension.

ComputerBase hat die Informationen im Rahmen des Architecture Day 2021 von Intel vorab auf einem Event in Berlin unter NDA erhalten. Eine Einflussnahme des Herstellers auf die Berichterstattung fand nicht statt, eine Verpflichtung zur Veröffentlichung bestand nicht. Einzige Vorgabe war der frühestmögliche Veröffentlichungstermin.

- Hot Chips 33: Samsung zeigt HBM-PIM und riesige Speichermodule

- Hot Chips 33: IBMs Telum-Architektur setzt auf 32 MB L2-Cache – pro Kern

- Hot Chips 33: Intel Alder Lake steht und fällt mit dem Thread Director

- +7 weitere News