Chipfertigung: Innovationen gestern, heute und morgen

Was steckt hinter der Halbleiterfertigung von Transistoren mit Maßen von wenigen Nanometern, aus denen Chips für CPUs, GPUs, SoCs und Co. bestehen? ComputerBase-Leser Christoph Riedel gibt einen fundierten Überblick über wesentliche Aspekte und Innovationen der Chipfertigung.

Zu Inhalt und Autor dieses Artikels

Dieser Artikel behandelt sowohl die verhältnismäßig einfachen Grundlagen zum Thema Transistoren als auch die verschiedenen Fortschritte und Innovationen, die deutliche Verbesserungen ermöglicht haben und in Zukunft noch ermöglichen werden. Oxiddicke, Materialien, FinFET, Multipatterning und Gate-All-Around. Über die Grundlagen der Chipfertigung hat im Artikel Vom Silizium zum Die: So werden aus Wafern im Reinraum Chips wiederum schon ComputerBase-Autor Thomas Böhm geschrieben.

Wie bei den vorangegangenen Artikeln von Christoph Riedel, „Was steckt hinter der EUV-Lithografie“ und „So werden Strahlen von GPUs beschleunigt“, hat es sich der Autor erneut zur Aufgabe gemacht, wissenschaftliche Erkenntnisse für ein breites Feld an Lesern verständlich zu beschreiben.

Dieser Text basiert in Teilen auf einem Artikel der Fachzeitschrift Journal of Physics mit dem Titel Review of Modern Field Effect Transistor Technologies for Scaling, der von Forschern der University of Dublin im letzten Jahr veröffentlicht wurde und frei verfügbar ist.

Grundlage aller im weiteren Verlauf behandelten technologischen Fortschritte ist der Transistor, aus den „Chips“ bestehen. Auch dem Transistor sollen deshalb noch ein paar Absätze gewidmet werden.

Transistor, MOSFET und CMOS kurz erklärt

Ein Transistor ist ein elektronisches Bauteil, das im Grunde einen Ein-/Ausschalter darstellt. Ein Steuersignal am Eingang, der Basis, ermöglicht einen Strom zwischen den beiden Ausgängen namens Kollektor und Emitter zu fließen oder eben auch nicht.

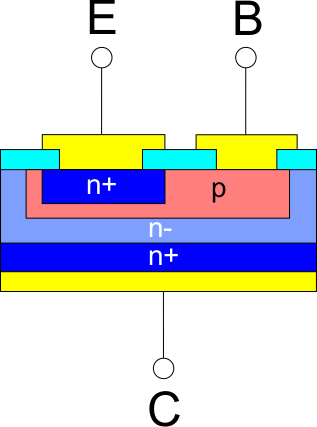

Ein einfacher Transistor ist der Bipolartransistor, der aus dotiertem Silizium besteht, das eine höhere Leitfähigkeit als unbehandeltes Silizium besitzt. Je nach Fremdmaterial, das in das Siliziumgitter eingebracht wird, spricht man von n-dotiertem (elektronenreichem) oder p-dotiertem (elektronenarmem) Silizium. Bipolartransistoren existieren als npn- oder pnp-Transistoren, wobei sich lediglich die Richtung des Stromflusses unterscheidet.

Beim npn-Transistor wird eine positive Spannung an die Basis gelegt, so dass ein kleiner Steuerstrom zwischen Basis und Emitter fließt. Dieser Strom wird vom Transistor um einen fixen Wert verstärkt, so dass ein größerer Strom zwischen Kollektor und Emitter fließt. Der Verstärkungsfaktor wird durch die externe Beschaltung mit Widerständen bestimmt. Ein Bipolartransistor ist dadurch ein analoger Stromverstärker, wie er heutzutage noch in Audio-Verstärkern eingesetzt wird.

-

Schematischer Aufbau eines Bipolartransistors mit Emitter (E), Basis (B) und Collector (C). (Bild: Wikipedia)

Schematischer Aufbau eines Bipolartransistors mit Emitter (E), Basis (B) und Collector (C). (Bild: Wikipedia)

Über MOSFETs zum CMOS

Für digitale Schaltungen benötigt man zwei deutlich voneinander abgegrenzte Spannungslevel für die Werte 0 und 1, z. B. 0 V und 5 V. Ein dafür passender Schalter wechselt zwischen diesen beiden Spannungslevel hin und her und nimmt keine Zwischenzustände ein. Um Verluste möglichst gering zu halten, sollte der Verstärker einen verschwindend geringen Stromfluss für den Schaltvorgang haben, was Bipolartransistoren ausschließt.

Diese Anforderungen wurden durch die Entwicklung von Feld-Effekt-Transistoren (FETs) erfüllt, die praktisch ohne Stromfluss arbeiten. Bei FETs werden die drei Anschlüsse als Gate, Source und Drain bezeichnet. Das Gate eines FETs ist durch eine isolierende Schicht vom Rest des Transistors getrennt. Wird am Gate eine Spannung angelegt, entsteht statt eines Steuerstromflusses ein elektrisches Feld, das eine erhöhte Leitfähigkeit zwischen Source und Drain bewirkt. Der FET schaltet daher stromfrei. Da nachfolgende FETs ebenfalls keinen Stromfluss benötigen um zu schalten, reicht ein Durchreichen der Schaltspannung von z. B. 5 V, um ganze Schaltungen zu betreiben. Eine digitale Schaltung bestehend aus einer Reihe von FETs ist daher theoretisch verlustfrei. Die Standard-Herstellungstechnik für FETs besteht aus einer Kombination von Metallen (M), isolierenden Oxiden (O) und Halbleitern (engl. Semiconductor, S), weswegen die Technologie für Feld-Effekt-Transistoren als MOSFET abgekürzt wird.

Für eine perfekte digitale Schaltung hat ein einzelner Transistor aber weiterhin einen Nachteil: Wenn er im gesperrten Zustand ist, ist die Spannung an seinem Ausgang nicht klar definiert. Es sind zwar nicht die 5 V der Versorgungsspannung, denn die ist gesperrt, aber es sind auch nicht exakt 0 V (GND), da dafür eine Leitung mit 0 V durchgereicht werden müsste. Diese Uneindeutigkeit im gesperrten Zustand wird dadurch aufgelöst, dass man zwei entgegengesetzt dotierte MOSFETs kombiniert. In einem Aufbau aus einem n-MOSFET und einem p-MOSFET arbeitet der erste Transistor wie oben beschrieben, während der zweite Transistor exakt 0 V durchreicht, wann immer der erste sperrt. Da sich die beiden Transistoren komplementär ergänzen, spricht man im Englischen von „Complementary MOSFET“, kurz CMOS. Die CMOS-Technologie ermöglicht saubere digitale Signale bei besonders niedrigem Energieverbrauch und kurzen Schaltzeiten.

Auf Basis dieses Wissens sollen nun die Fertigungstechniken und die Funktionsweise moderner CMOS-Transistoren betrachtet werden.

Das Ziel der Halbleiterfertigungstechnik

Das Ziel der Halbleiterfertigungstechnik ist die immer kleinere Fertigung von Feld-Effekt-Transistoren, wodurch immer komplexere Schaltungen mit sinkenden Kosten gefertigt werden können, denn jeder belichtete mm² auf dem Wafer kostet. Weitere Vorteile wie erhöhte Schaltgeschwindigkeiten und eine verringerte Leistungsaufnahme der Transistoren sind sekundäre Effekte verbesserter Fertigung. Eine detailliertere Übersicht über die Halbleiterfertigung im Reinraum hat ComputerBase bereits vor einigen Jahren im Selbstversuch erstellt.

Die Fertigung durch Foto-Lithografie baut einen Transistor grundsätzlich von unten nach oben auf. Verglichen mit einem Bipolartransistor ist der Aufbau eines CMOS-Transistors in den unteren Schichten sehr ähnlich. Diese Bereiche werden durch die unterschiedliche Dotierung des Siliziums erreicht. Für jede Dotierung ist dabei ein Lithografie-Schritt, bestehend aus der Aufbringung von Fotolack, der Belichtung und dem Entwickeln, notwendig. Der besondere Unterschied beim FET ist die Integration eines kondensatorähnlichen Aufbaus an der Basis, der Ladungsträger ober- bzw. unterhalb der Oxidschicht (je nach Spannung) ansammelt. Dadurch werden zwei weitere Lithografie-Schritte notwendig, bei denen anstelle einer Dotierung erst der Isolator und dann der Metallkontakt aufgetragen werden.

Ihr habt die Wahl: Macht mit bei den Reader's Choice Awards 2025 und bestimmt eure Hersteller des Jahres!