Genoa (Zen 4): AMD Epyc unterstützt 12 TB RAM und DDR5-5200

Nächstes Jahr wird AMD die nächste Generation Server-CPUs der Epyc-Familie bringen. Auf Milan mit Zen-3-Architektur folgt Genoa mit Zen 4. Bis zu 96 Kerne hatte AMD schon öffentlich angekündigt. Dass auch die Zahl der Speicherkanäle um 50 Prozent steigt, verraten Einträge im Linux-Treiber.

Dass AMD Genoa erstmals in der Epyc-Familie DDR5-Speicher unterstützen wird, wie auch bei Intel Sapphire Rapids der Fall, ist längst bekannt. So wundert es auch nicht, dass Entwickler von AMD jetzt per Patch einen Linux-Treiber bereits für die Unterstützung von DDR5-RAM vorbereiten. Die entsprechenden Einträge sind dabei selbsterklärend:

EDAC: Add RDDR5 and LRDDR5 memory types

EDAC/amd64: Add support for AMD Family 19h Models 10h-1Fh and A0h-AFh

EDAC/amd64: Check register values from all UMCs

EDAC/amd64: Add DDR5 support and related register changes

An anderer Stelle gibt es dann den bisher nicht öffentlich kommunizierten Hinweis auf die Anzahl der Speichercontroller (Memory Controller, MC) und die damit verbundene Anzahl der Speicherkanäle. Die maximale Anzahl steigt demnach von bisher 8 auf deren 12. Das entspricht 50 Prozent Zuwachs, wie auch bei der maximalen Anzahl der CPU-Kerne: Die aktuelle Generation Milan (Epyc 7003) bietet bis zu 64 Kerne, der Nachfolger Genoa (Epyc 7004) wird bis zu 96 Kerne aufweisen.

Add a new family type for AMD Family 19h Models 10h to 1Fh. Use this new

family type for Models A0h to AFh also.

Increase the maximum number of controllers from 8 to 12.

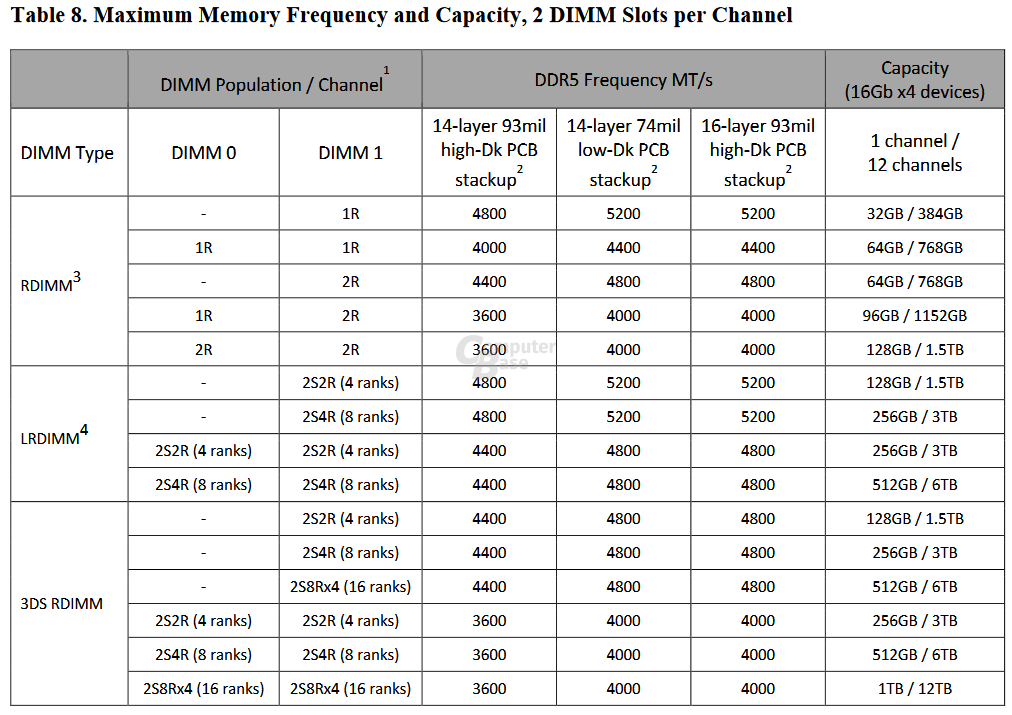

Wie viele DDR5-RDIMMs (Registered DIMM) respektive DDR5-LRDIMMs (Load Reduced DIMM) auf der Plattform insgesamt eingesetzt werden können, sagen die Einträge nicht. Doch gibt es Hinweise an anderer Stelle, dass Genoa ebenfalls bis zu zwei Module pro Kanal unterstützt.

Bis zu 12 TB DDR5 pro Sockel

Milan erlaubt bisher maximal 16 DDR4-Module für bis zu 4 TB RAM mit den größten Modulen à 256 GB. Die gleiche Rechnung würde für Genoa 6 TB bedeuten. Mit den von Samsung angekündigten 512-GB-DDR5-Riegeln wären aber sogar 12 TB pro Sockel möglich, das besagt auch eine durchgesickerte Kompatibilitätsliste von AMD für Genoa.

Diese besagt auch, dass Genoa maximal DDR5-5200 unterstützt. Bei Vollbestückung mit 24 Speicherriegeln der allerhöchsten Kapazität steht aber nur maximal DDR5-4000 zur Verfügung.

Genoa folgt Sapphire Rapids mit großen Schritten

Noch ist nicht bekannt, wann die neue Epyc-Generation Genoa nächstes Jahr den Markt erreichen soll. Kunden von AMD sollen allerdings schon Muster zur Validierung erhalten, wie AMD vor einem Monat mitgeteilt hat. Die neue Plattform hat es in sich, denn nicht nur mehr und potenziell schnellere Kerne, mehr Speicherkanäle und DDR5, sondern auch PCIe 5.0 steht auf der Liste der Neuerungen. Gefertigt wird Zen 4 im N5-Verfahren bei TSMC.

Intel Sapphire Rapids wird zeitlich einen deutlichen Vorsprung haben und bereits Anfang 2022 erhältlich sein. Das Debüt von DDR5 und PCIe 5.0 im Server gebührt somit der neuen Xeon-Plattform. Unklar ist noch, wie viele der schnellen Golden-Cove-Kerne maximal zur Verfügung stehen werden, es dürften aber deutlich weniger als bei Genoa sein; sogar etwas weniger als bei AMD Milan werden erwartet. Die Zahl der DRAM-Channel liegt mit 8 auf dem Niveau der aktuellen AMD-Plattform.

Mit Bergamo will AMD auf 128 Kerne erhöhen

Im ersten Halbjahr 2023 will AMD dann gleich noch eine Schippe drauflegen und mit Bergamo alias Zen 4c eine Spezialausführung für den Cloud-Sektor bringen, die sogar über 128 Kerne verfügt.