PCI Express 6.0: Standard für bis zu 256 GB/s am x16-Slot veröffentlicht

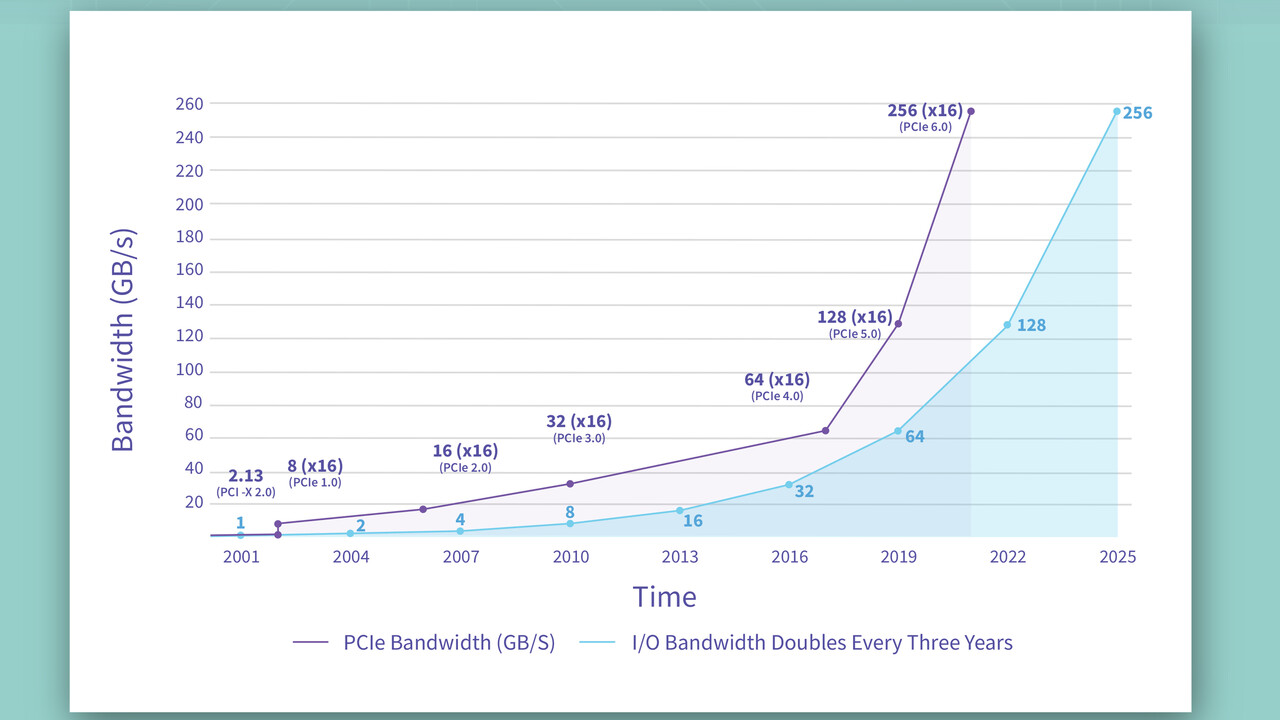

Die breite Markteinführung von PCIe 5.0 steht erst im Laufe des Jahres bevor, da ist der Nachfolger des Schnittstellenstandards bereits final spezifiziert. Die Spezifikationen für PCIe 6.0 mit einer abermals doppelten Datenrate von bis zu 256 GB/s bei PCIe 6.0 x16 wurden jetzt vom zuständigen Konsortium PCI-SIG veröffentlicht.

Während im Consumer-Bereich aktuell noch PCIe 3.0 und PCIe 4.0 mit einer Bandbreite von 1 GB/s respektive 2 GB/s pro Leitung und insgesamt 16 GB/s respektive 32 GB/s in jede Richtung am x16-Slot dominiert, sollen das Refresh der Core-i-12000-Serie (Test) alias Raptor Lake und Ryzen 7000 („Raphael“) auf Basis von Zen 4 erstmals den Schnittstellenstandard PCIe 5.0 in die breite Masse bringen. Auch Alder Lake alias die 12. Generation Core kann bereits PCIe 5.0, allerdings offiziell nur in Form von 16 Lanes für PCIe-Grafikkarten, die es noch nicht mit PCIe 5.0 gibt.

PCIe 6.0 x16 mit bis zu 256 GB/s

Während PCIe 5.0 aktuell gerade erst im Enterprise-Bereich richtig Fuß fasst, hat die PCI-SIG jetzt bereits PCI Express 6.0 in der Version 1.0 spezifiziert und wirbt mit einer Bandbreite von 8 GB/s pro Lane oder bis zu 256 GB/s am PCIe-6.0-x16-Slot.

Damit kommt PCIe 6.0 auf rund 128 GB/s I/O-Bandbreite, da PCI Express aber einen Dual-Simplex-Betrieb mit einer gleichzeitigen Datenübertragung in beide Richtungen ermöglicht, wirbt die PCI-SIG mit 256 GB/s – PCIe 5.0 erreicht analog 128 GB/s, 4.0 64 GB/s und 3.0 32 GB/s.

Die vollständigen Spezifikationen sind nur für Mitglieder des PCI-SIG-Konsortiums einsehbar. Die öffentlich kommunizierten Eckdaten der offiziellen Version 1.0 lauten indes wie folgt:

- 64 GT/s raw data rate and up to 256 GB/s via x16 configuration

- Pulse Amplitude Modulation with 4 levels (PAM4) signaling and leverages existing PAM4 already available in the industry

- Lightweight Forward Error Correct (FEC) and Cyclic Redundancy Check (CRC) mitigate the bit error rate increase associated with PAM4 signaling

- Flit (flow control unit) based encoding supports PAM4 modulation and enables more than double the bandwidth gain

- Updated Packet layout used in Flit Mode to provide additional functionality and simplify processing

- Maintains backwards compatibility with all previous generations of PCIe technology

Wie schon bei den vorherigen Generationen der seriellen Schnittstelle PCI Express soll auch PCIe 6.0 bis hinab zur ersten Generation abwärtskompatibel sein. Weitere Details hierzu liefert die öffentlich einsehbare FAQ zu PCIe 6.0.

PCIe 6.0 nutzt Pulsamplitudenmodulation

Der im Vergleich zum direkten Vorgänger PCI Express 5.0 abermals verdoppelte Datendurchsatz wird durch den Wechsel zur Pulsamplitudenmodulation (PAM) mit insgesamt vier Signalzuständen möglich, wodurch in der gleichen Zeit ungleich mehr Bits übertragen werden können.

Den Bedarf an solch hohen Übertragungsraten sehen Branchenexperten und die PCI-SIG unter anderem in den Bereichen High-Performance Computing (HPC), Künstliche Intelligenz, Machine Learning, IoT, Netzwerke, Storage und Supercomputer. Außerdem wird auch erstmals der Bereich Automotive als Use Case für PCIe 6.0 genannt.

PCIe 6.0 ist noch Zukunftsmusik

Bis PCIe 6.0 im Consumer-Bereich seine Spuren hinterlässt, dürften aber noch einige Jahre ins Land ziehen. Im Enterprise-Sektor haben unter anderem Intel und AMD in Aussicht gestellt, den neuen Standard mit CXL alias Compute Express Link vorantreiben zu wollen. Intels und AMDs nächste Server-CPU-Generationen, Sapphire Rapids und Genoa, werden CXL nutzen, dann allerdings noch auf Basis von PCIe 5.0.