IMW 2022: Kioxia experimentiert mit 7 Bit pro NAND-Speicherzelle

Hatte Kioxia im letzten Jahr die Möglichkeit, unter extremen Bedingungen 6 Bit in einer NAND-Flash-Zelle zu speichern (HLC), demonstriert, erhöht der Hersteller dieses Jahr auf 7 Bit. Praktikabel ist die Machbarkeitsstudie bei Temperaturen von -196 °C allerdings nicht. TLC- und QLC-NAND werden noch lange bleiben.

Wie schon bei der Konzeptstudie eines Hexa-Level-Cell-NAND (HLC) mit 6 Bit pro Speicherzelle klappte das erfolgreiche Schreiben und Lesen von 7 Bit in respektive aus Hepta-Level-Cell-NAND (ebenfalls HLC?) nur bei einer extrem niedrigen Temperatur von 77 Kelvin respektive -196 °C. Erneut dürfte flüssiger Stickstoff als Kühlmittel gedient haben. Die neue Studie wurde im Rahmen des International Memory Workshop (IMW) vorgestellt.

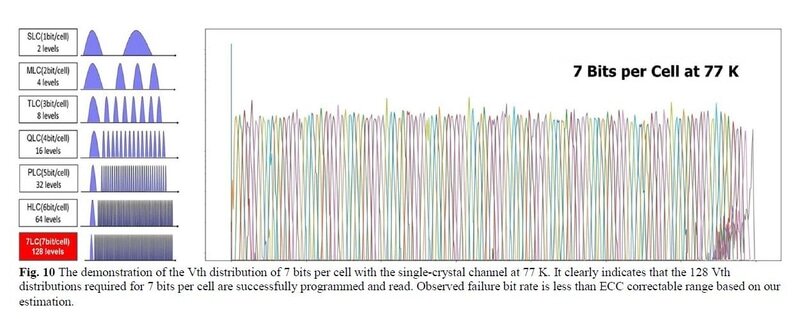

128 Spannungen für 7 Bit in der Zelle

Um ein weiteres Bit in der Zelle unterzubringen, was ganze 128 zu unterscheidende Spannungsniveaus bedeutet, mussten die Forscher von Kioxia allerdings weitere Maßnahmen ergreifen. So kam für den Kanal (Channel) Silizium in Monokristall-Struktur (mono-Si) als Material zum Einsatz, während beim 6-Bit-Versuch Polycrystalline Silicon (poly-Si) verwendet wurde. Durch das mono-Si mit niedrigerem elektrischen Widerstand wurde unter anderem der Leckstrom reduziert. Die Varianz der Schwellenspannung wurde dadurch verringert und es gelang, die 128 Spannungslevel für 7 Bit an Information in der Zelle zu schreiben und zu lesen.

-

Kioxias Experiment mit 7-Bit-Flash-Speicher (Bild: Kioxia (via PC Watch))

Kioxias Experiment mit 7-Bit-Flash-Speicher (Bild: Kioxia (via PC Watch))

Grafiken veranschaulichen um wie viel komplexer der Speichervorgang mit jedem weiteren Bit pro Zelle wird. Es ist daher zweifelhaft, dass dies in absehbarer Zeit unter normalen Temperaturbedingungen und mit brauchbarer Leistung und Haltbarkeit der Zellen gelingen wird, wenn überhaupt.

TLC und QLC werden noch lange bleiben

Aktuell bilden 4 Bit pro Zelle bei QLC-NAND das verfügbare Maximum. Die Zelle muss dafür in der Lage sein, 16 verschiedene Spannungszustände eindeutig unterscheidbar dauerhaft abzuspeichern. Es wird aber bereits die Kommerzialisierung von Penta-Level-Cell (PLC) NAND mit 5 Bit pro Zelle erwogen, was 32 verschiedene Zustände pro Zelle notwendig macht; vor 2026 ist damit aber wohl nicht zu rechnen. Doch vorerst wird die Branche weiter vor allem TLC-NAND (3 Bit) produzieren sowie den QLC-NAND weiter verbessern, sodass dieser mehr Leistung bietet.

| 1 Bit (SLC) | 2 Bit (MLC) | 3 Bit (TLC) | 4 Bit (QLC) | |

|---|---|---|---|---|

| Benötigte Spannungszustände | 21 | 22 | 23 | 24 |

| 1 | 0 | 0 0 | 0 0 0 | 0 0 0 0 |

| 2 | 1 | 0 1 | 0 0 1 | 0 0 0 1 |

| 3 | – | 1 0 | 0 1 1 | 0 0 1 1 |

| 4 | – | 1 1 | 1 1 1 | 0 1 1 1 |

| 5 | – | – | 1 0 0 | 1 1 1 1 |

| 6 | – | – | 1 1 0 | 1 0 0 0 |

| 7 | – | – | 0 1 0 | 1 1 0 0 |

| 8 | – | – | 1 0 1 | 1 1 1 0 |

| 9 | – | – | – | 1 0 0 1 |

| 10 | – | – | – | 0 1 1 0 |

| 11 | – | – | – | 1 1 0 1 |

| 12 | – | – | – | 1 0 1 1 |

| 13 | – | – | – | 0 1 0 0 |

| 14 | – | – | – | 0 0 1 0 |

| 15 | – | – | – | 0 1 0 1 |

| 16 | – | – | – | 1 0 1 0 |

Denn mit jedem weiteren Bit wird auch mehr Zeit für das Lesen und Schreiben in der Zelle benötigt. Bei manchen SSDs mit QLC-NAND macht sich dies in äußerst geringen Schreibraten auf HDD-Niveau bemerkbar, sobald der SLC-Schreibpuffer mit 1 Bit pro Zelle ausgeht.