Maximale Flexibilität bei TSMC: Fünf N3-Fertigungsstufen, N5 gestapelt ab 2023

Drei Jahre Laufzeit zwischen neuen Nodes kompensiert TSMC mit neuen Zwischenstufen und mehr Flexibilität – schon auf Transistorebene. FinFlex nennt TSMC diesen Ansatz, bei dem Kunden in einer bestimmten Fertigungsstufe noch zwischen Fläche, Leistung und Energieaufnahme priorisieren können. Heraus kommen unzählige Möglichkeiten.

N3-Nodes in diversen Ausführungen

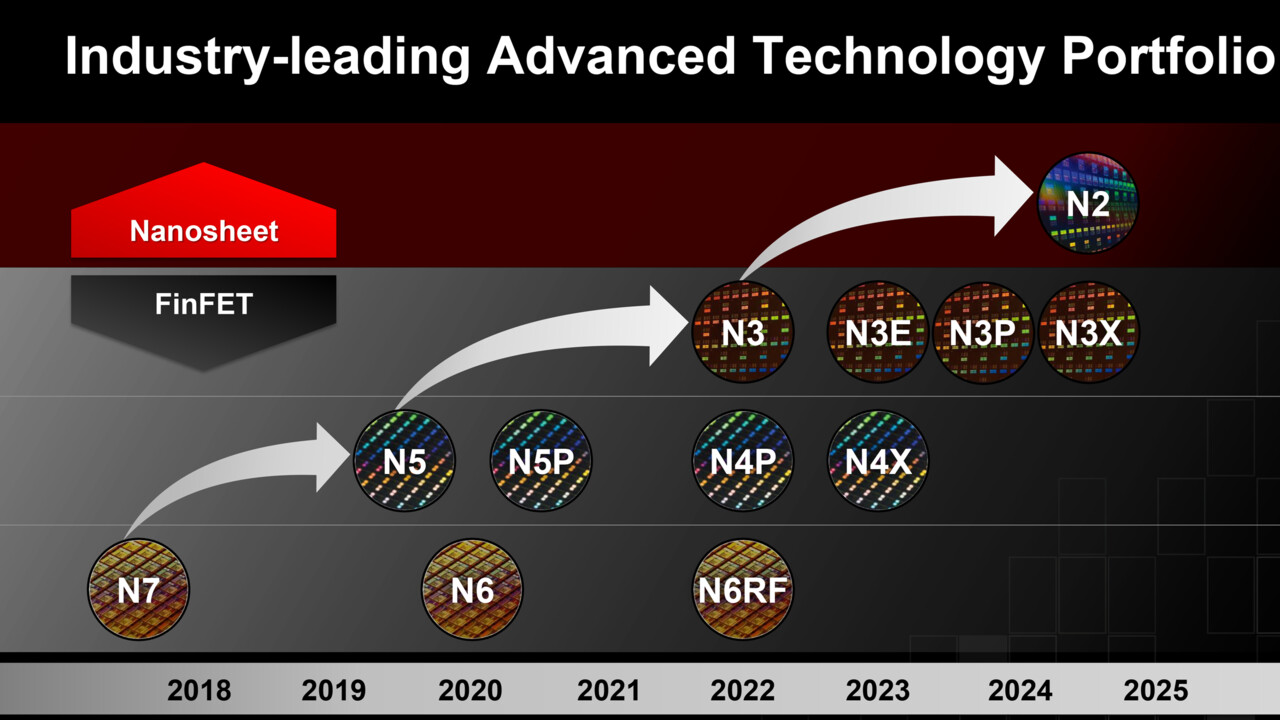

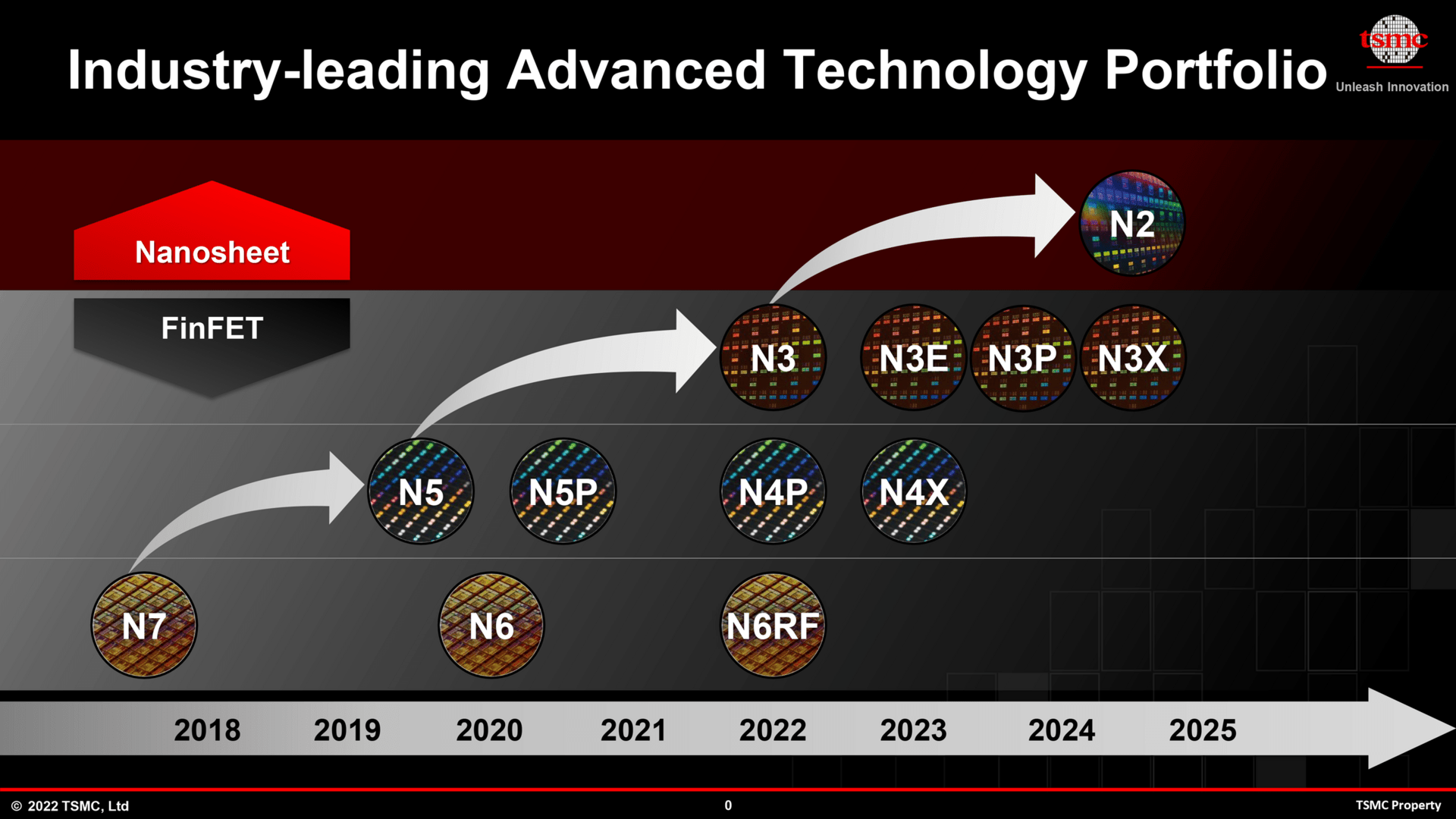

Grundlage für FinFlex wird ein N3-Prozess von TSMC sein. Von denen plant der weltgrößte Auftragsfertiger nun mit bereits fünf Varianten: N3 als Basis-Version, die jedoch kaum genutzt werden dürfte. N3E hingegen als Enhanced-Variante, der Fokus liegt voll auf dieser Stufe. Es folgt die klassische Lösung N3P als Performance-Variante und N3X als Extreme-Performance-Version und damit Nachfolger von N4X, welches erst im nächsten Jahr zur Verfügung stehen wird – entsprechend spät kommt dadurch wiederum N3X. Und mitten drin wird als spezielle Variante noch N3S eingepflegt, die exakten Boni dieser Lösung sind heute unklar, weshalb es nicht einmal einen Roadmap-Eintrag dazu gibt.

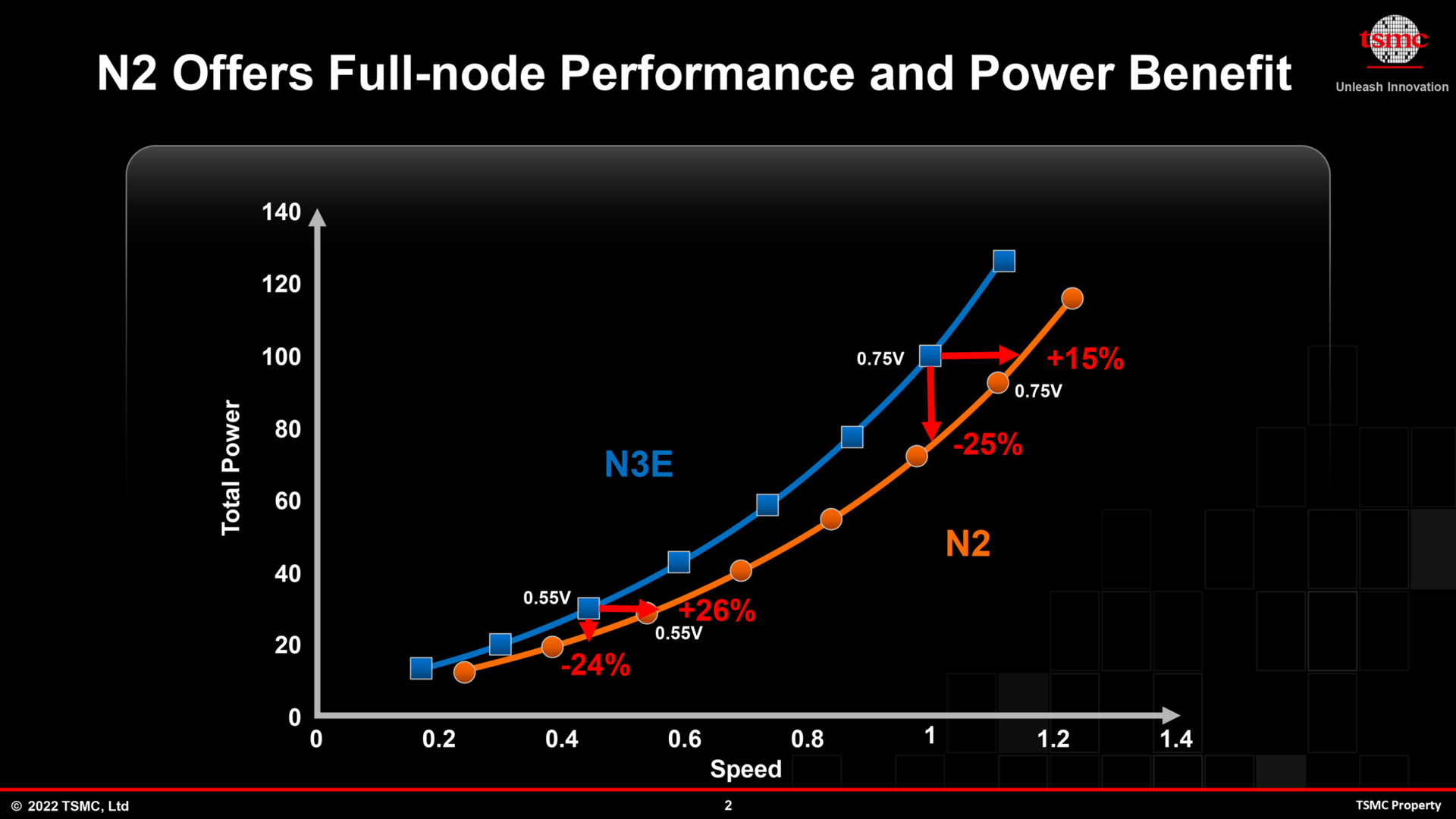

Interessant sind die Bezugsangaben von TSMC heute. Nahezu in keinem Diagramm oder auf einer Folie wird der Basis-Prozess N3 gewählt, sondern stets direkt zu N3E übergegangen. Es wird bereits seit einiger Zeit gemunkelt, dass TSMC mit der ersten Auskopplung seine liebe Mühe hatte, sowohl was die Boni gegenüber bisherigen Prozessen als auch die Ausbeute angeht. TSMC betont heute die Yield sind „gut“, Ende des Jahres wird die Produktion anlaufen. N3E folgt jedoch binnen Monaten mit noch mehr Leistung oder geringerem Verbrauch und verbesserten Yields, was eher dafür spricht, dass TSMC beim Ursprung die anvisierten Pläne nicht so umsetzen konnte – leistungstechnisch und zeitlich. Deshalb ist N3E de facto die neue Basis, auch im Vergleich zum nächsten großen Prozess: N2 auf Basis von Nanosheets a.k.a Gate All Around.

FinFlex für das Beste aus Leistung, Watt & Fläche

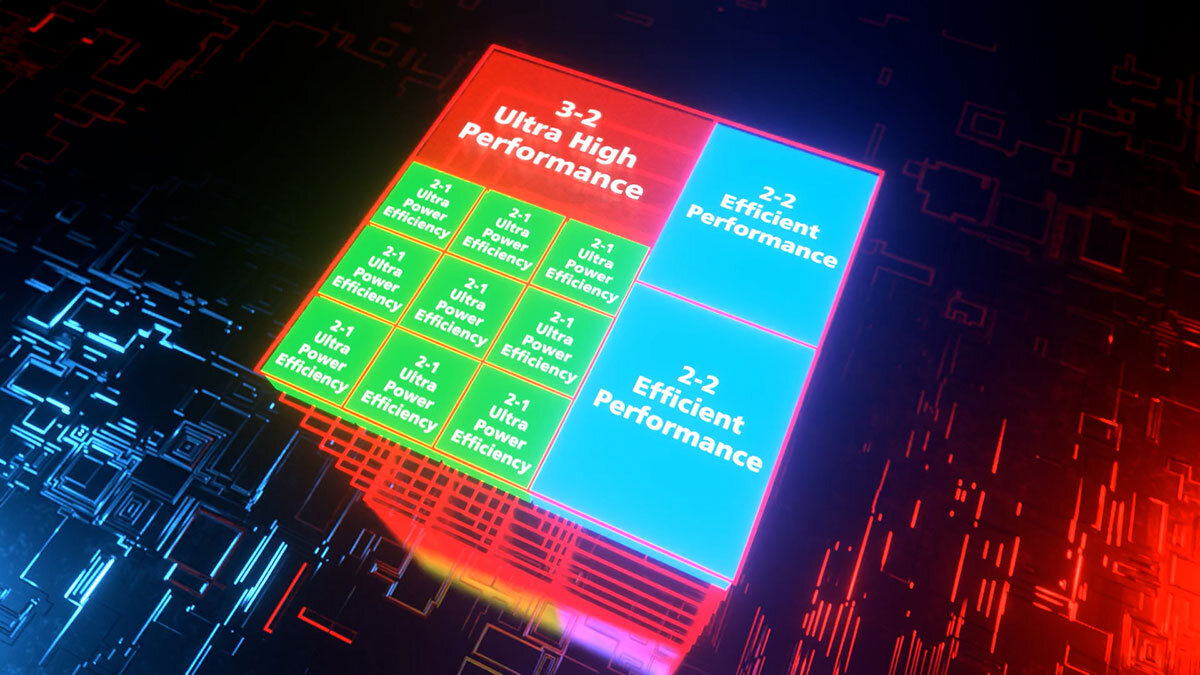

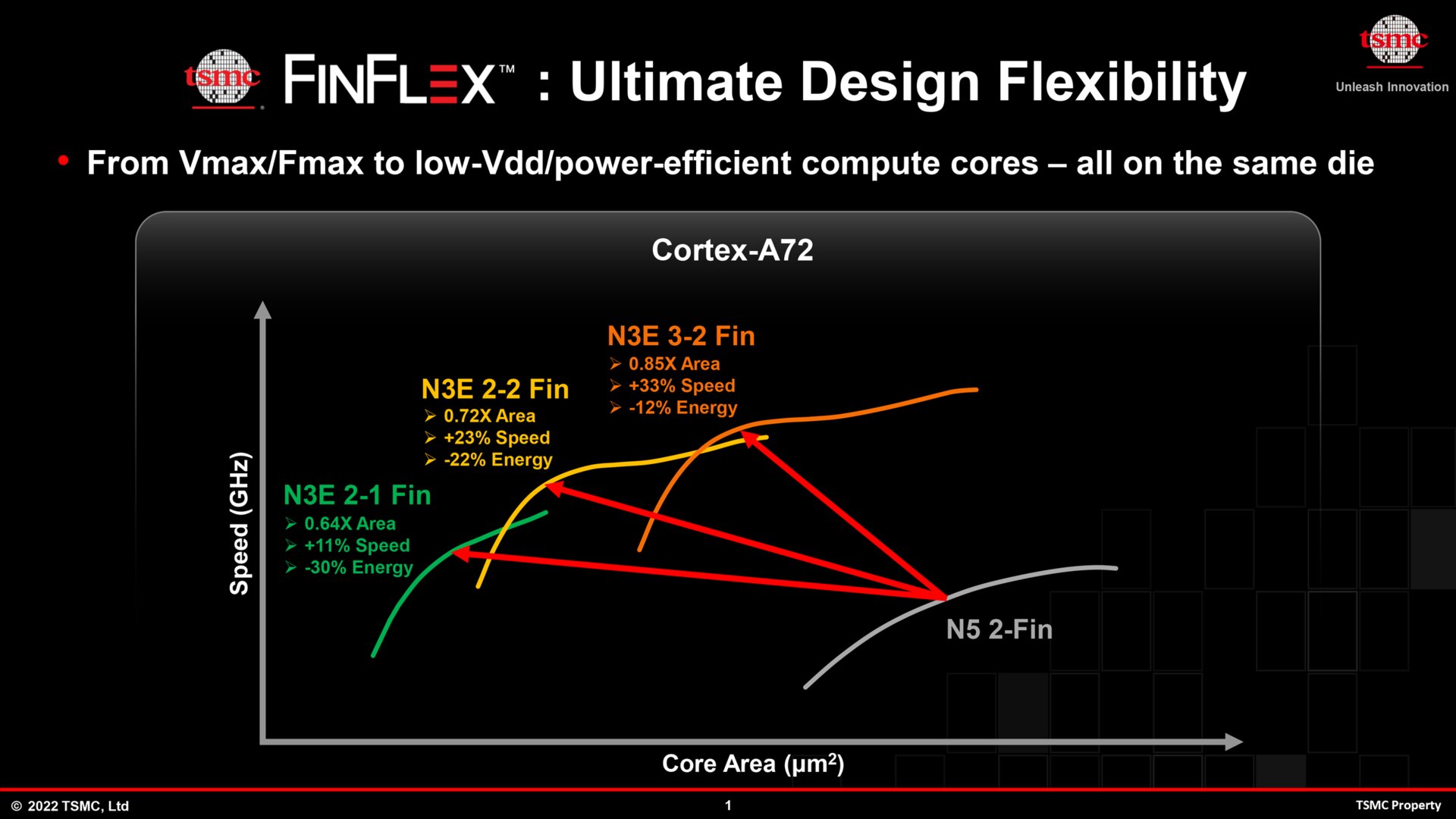

Genau an diesem N3E-Prozess erklärt TSMC auch die neue FinFlex-Umsetzung. Chips sind heute nicht mehr nur für einen einzigen Einsatzzweck gebaut, sondern sollen viele Sachen beherrschen. Die neuen flexiblen Umsetzungen erlauben es, auf einem einzigen Die drei verschiedene Arten von Transistoren zu nutzen, um nicht komplett einen Kompromiss zum Einsatz zu bringen, sondern die jeweiligen Teilbereiche zu ihrer besten Performance oder der höchsten Ersparnis zu verhelfen.

CPU-Kerne werden dann beispielsweise mit neuen 3-2-Fins gefertigt, die mittlere Lösung umfasst ein 2-2-Finblock, während am unteren Ende eine 1-2-Fin-Lösung steht, die voll auf Stromsparen ausgelegt ist. Diese Kombination ermöglicht es laut TSMC auch, im Vergleich zu einer auf normalen Weg umgesetzten Lösung bis zu 23 Prozent an Fläche einzusparen. Ein Common Design Kit soll Kunden helfen, die für sie beste Lösung schnell zu finden und umzusetzen. Ein kleines Video von TSMC erklärt dies ein wenig.

Gestapelter N5-Prozess für 2023 im Plan

Auch ein Update gab TSMC zu den modernen Stapel-Technologien. Im Fokus steht medial ganz vorn AMDs 3D-V-Cache-Lösung, die auch bei kommenden Zen-4-Prozessen zum Einsatz kommen wird. Diese wurden bisher für 2023 prognostiziert, TSMC erklärt nun, dass der N5-Prozess dann bereit ist für diese Lösungen, die neu gebaute 3DFabric-Fabrik soll im zweiten Halbjahr dieses Jahres nahezu vollautomatisiert in Betrieb genommen werden und deutlich mehr Kapazität bieten als für die erste Generation zur Verfügung stand. Im Test des AMD Ryzen R7 5800X3D mit dieser Technologie zog die Redaktion bereits im April das Fazit, dass diese Technologie gekommen ist, um zu bleiben.

Ihr habt die Wahl: Macht mit bei den Reader's Choice Awards 2025 und bestimmt eure Hersteller des Jahres!