Next-Gen-GAA-Fertigung: Ab N2 kommen auch bei TSMC Nanosheets zum Einsatz

Nanosheets werden in Zukunft bei allen großen Halbleiterherstellern eine Rolle spielen. Auch TSMC setzt ab der Fertigungsstufe N2 auf GAA, wie die weltgrößte Foundry bestätigt. Zum Einsatz könnte die Technologie ab dem Jahr 2025 kommen. Samsung will wiederum bei 3 nm schon in diesem Jahr darauf setzen.

Nanosheets gehen Hand in Hand mit Gate-All-Around-Transistoren

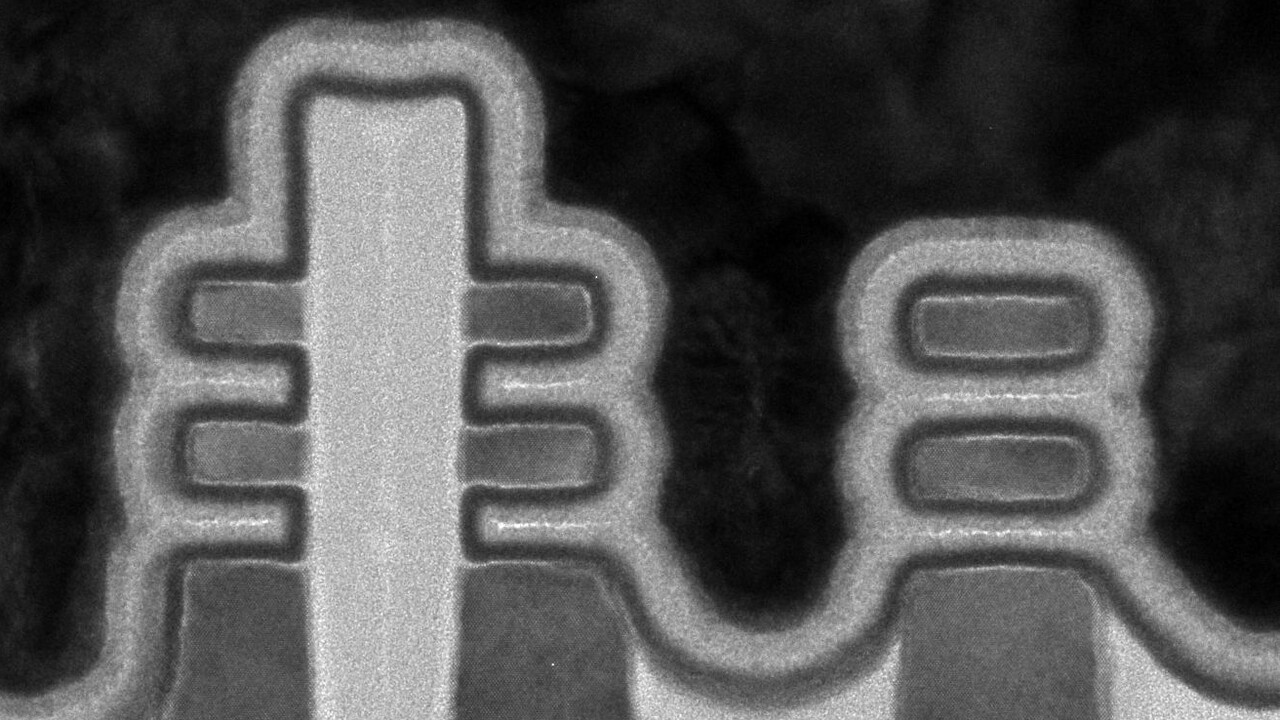

Nanosheets respektive Nanowires sind zweidimensionale Strukturen mit einer Dicke von unter 100 nm. Sie sind seit Jahren auf den Roadmaps und in den Forschungslaboren der Chipindustrie ein Thema, sollen sie doch die Nachfolge-Technologie von FinFET möglich machen, die Transistoren in dreidimensionaler Finnenstruktur nutzt.

Nanosheets werden erstmals mit der neuen Gate-All-Around-Fertigung (GAA) zum Einsatz kommen, denn die ist auf die neuen dünnen „Fäden“ angewiesen. Gate-All-Around ist in der Basis zwar dem heute gängigen dreidimensionalen FinFET sehr ähnlich, soll mit gezielten Anpassungen aber den Sprung auf unter 5 nm ermöglichen.

Die weitere Verbesserung der Transistorleistung ergibt sich, wenn man die letzte verbliebene Seite, die Unterseite des Kanals, ebenfalls mit Oxid und Gate-Kontakt umschließt. Dadurch entsteht ein Gate-All-Around-FET oder GAAFET. IBM hat dieses Verfahren erstmals 2017 veröffentlicht.

Bei dieser Technologie liegt Samsung auf dem Papier deutlich vorn und will noch dieses Jahr erste Produkte liefern, bei TSMC plant man die Einführung erst für das Jahr 2025.

TSMC wechselt mit N2 von FinFET auf GAA

Immerhin hat TSMC nun ebenfalls den Einsatz dieser Nanosheets bestätigt – und damit auch, dass man beim N2-Fertigungsschritt von FinFETs auf die GAA-Technologie wechseln wird. TSMC gilt hier als sehr zurückhaltend, sucht bei der anstehenden neuen Fertigungsstufe N3 das Heil noch in den klassischen FinFETS. Zu diesem Thema gab es zuletzt Gerüchte, denen zufolge es zu Problemen bei der Skalierung kommen könnte respektive die anvisierten Ziele nicht erreicht würden, welche TSMC jedoch verneinte. Laut TSMC verlaufe demnach bei den neuen Nodes N3 und N3E alles nach Plan, Produktionsbeginn ist das zweite Halbjahr 2022 in kleiner Stückzahl.

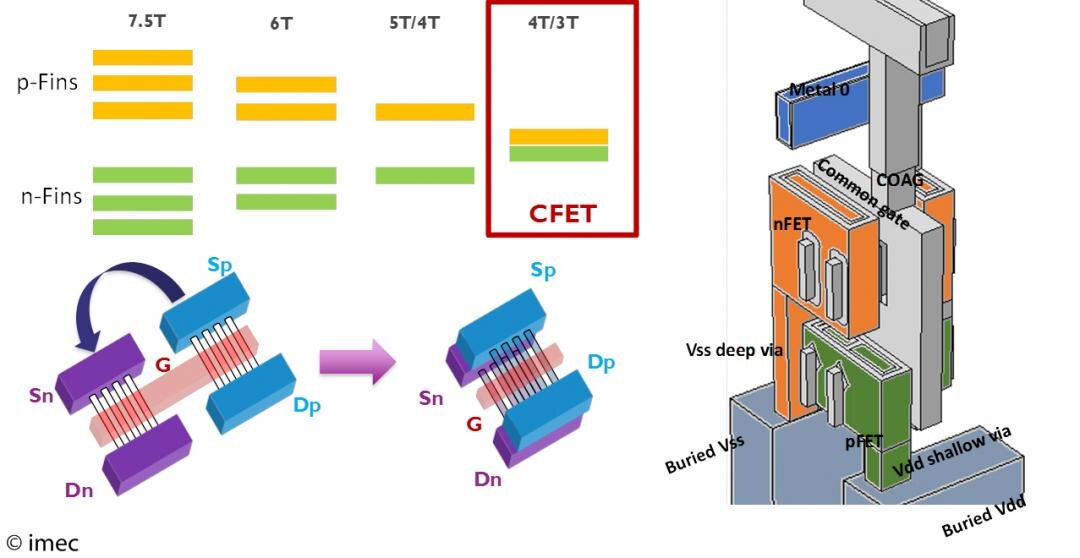

Nanosheets sind aber auch bei TSMC nur der erste Schritt, den der Hersteller gehen muss. Den weiteren Blick voraus wirft TSMC direkt auf complementary FET (CFET). Dabei wird durch das Stacking von n-type- und p-type-Halbleitern eine massive Reduzierung in der benötigten Fläche versprochen. Daran forschen viele Unternehmen zum Teil in Zusammenarbeit bereits seit Jahren, bereits 2018 gab es die ersten Vorträge. Auch bei TSMC steht die Technologie hoch im Kurs, steckt aber ebenfalls noch in der Forschung.

Als Überbrückung bis dahin könnten Forksheets übernehmen – die kleinen Sheets mit gleicher Basis sehen aus wie die Spitze einer auf der Seite liegenden Gabel (englisch: fork). Sie versprechen gegenüber den Nanosheets ebenfalls bereits bis zu 20 Prozent weniger Platzbedarf, zehn Prozent mehr Leistung oder 24 Prozent geringeren Energiebedarf. Da sie als Evolution von Nanosheets angesehen werden, sollen sie mit leichten Anpassungen umsetzbar sein. Letztlich folgt TSMC bei seinen Entwicklungen ziemlich exakt den Weg, den imec bereits seit einigen Jahren beschreibt.

Mehr Informationen zu Technologien in der Chipfertigung

Viele Informationen zu Innovationen in der Chipfertigung, darunter FinFET und GAA, liefert der Artikel Chipfertigung: Innovationen gestern, heute und morgen.

Heute hat TSMC die Fertigungsstufe N2 offiziell enthüllt und die zuvor genannten Daten bestätigt. Der Wechsel zu Gate All Around, oder Nanosheets, wie TSMC den Begriff nutzt, soll gegenüber der Fertigungsstufe N3(E) 10 bis 15 Prozent mehr Leistung bei gleicher Leistungsaufnahme oder aber 25 bis 30 Prozent geringere Leistungsaufnahme bei gleicher Performance bieten. Eine High-Performance-Variante als auch eine Mobile-Version sollen davon aufgelegt werden. Produktionsbeginn ist frühestens im Jahr 2025.

Helfen wird auch bei TSMC in Zukunft High-NA-EUV von ASML. Laut Medienberichten erklärte TSMC zum Technology Symposion in den USA, ebenfalls wie Intel bereits 2024 über die Technologie verfügen zu können.