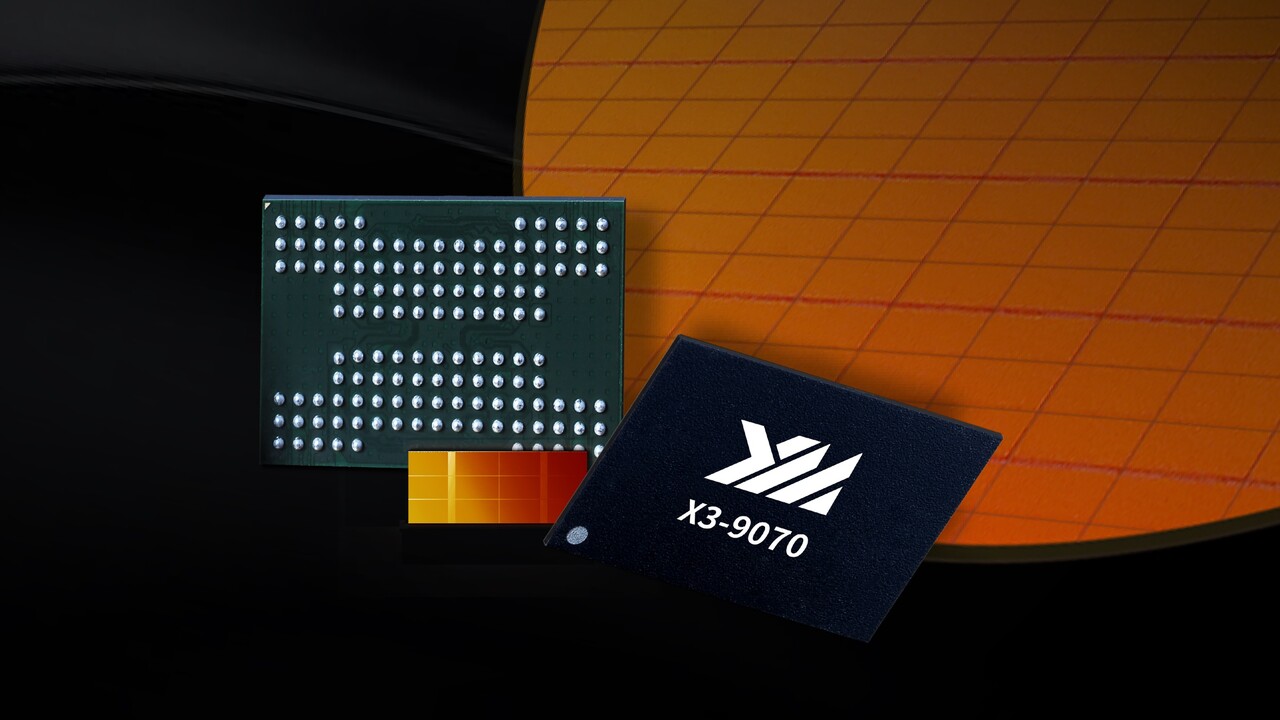

YMTC X3-9070: Neuer TLC-NAND aus China umgeht das Layer-Spiel

Auch der chinesische Newcomer unter den Herstellern von Flash-Speicher für SSDs und Smartphones präsentiert zum Flash Memory Summit 2022 eine neue Generation 3D-NAND. YMTC nennt diese X3-9070 und wirbt mit neuer Xtacking-3.0-Architektur. Dass die Anzahl der Layer verschwiegen wird, verblüfft.

X3-9070 steht für TLC

Beim dem X3-9070 genannten Speicher handelt es sich um TLC-NAND mit 3 Bit pro Speicherzelle. Die TLC-Variante der früheren 128-Layer-Generation wurde X2-9060 getauft, während die QLC-Version X2-6070 lautet.

Wie schon bei den vorherigen Generationen von YMTC kommt die sogenannte Xtacking-Technik zum Einsatz: Dabei werden Chip-Logik (I/O) und Speicherbereich zunächst getrennt voneinander auf separaten Wafern gefertigt und erst später zu einem Speicherchip vereint; YMTC spricht von „Hybrid Bonding“. Obwohl somit zwei Wafer benötigt werden, sollen die Kosten insgesamt nicht steigen, da sich auf diesem Weg die Speicherdichte so weit optimieren lasse, dass sich der zusätzliche Wafer rentiert.

YMTC nimmt Layer nicht in den Mund

Was sich nun im Detail mit der inzwischen dritten Ausführung namens Xtacking 3.0 ändert, bleibt vorerst verborgen. Das gilt zur Überraschung vieler auch für die vor allem im Marketing sehr wichtige Angabe der Anzahl der übereinander liegenden Ebenen (Layer) mit Speicherzellen. Warum YMTC diese vorerst verschweigt, ist unklar. Möglich wäre, dass diese deutlich geringer als bei den Konkurrenten Micron mit 232 Layern und SK Hynix mit 238 Layern ausfällt, und dieser Umstand nicht zu sehr ins Rampenlicht gerückt werden soll.

Letztlich könnten es bei YMTC 192 Layer sein, denn im Mai hatte DigiTimes berichtet, dass entsprechende Muster ausgeliefert werden. Einen Monat später folgte aber der Bericht, dass YMTC die 192-Layer-Generation zugunsten der 232-Layer-Generation überspringen werde. Von offizieller Seite gab es dafür aber bisher keine Bestätigung.

ONFI 5.0 mit 2.400 MT/s und 6-Plane-Design

Allerdings nennt YMTC andere Details zum neuen TLC-3D-NAND alias X3-9070. So soll wie bei den Neuheiten von Micron und SK Hynix das NAND-Interface auf 2.400 MT/s (ONFI 5.0) beschleunigt werden und somit gegenüber dem Vorgänger um 50 Prozent zulegen. Wie bei Micron soll der TLC-NAND 1 Terabit speichern, während zuvor 512 Gbit üblich waren und es 1-Tbit-Chips nur bei QLC-NAND mit 4 Bit pro Zelle gab. YMTC spricht von der größten Bit-Dichte in der jungen Geschichte des Unternehmens. Ohne Angabe der Chipgröße lässt sich diese allerdings nicht errechnen.

Für mehr Leistung soll neben der schnelleren Schnittstelle der Wechsel auf ein 6-Plane-Design sorgen. Gegenüber dem 4-Plane-Design soll die Leistung analog um bis zu 50 Prozent steigen, während sich parallel die Leistungsaufnahme um 25 Prozent verringern lasse. Erstmals hatte Micron mit seinem 232-Layer-NAND ein 6-Plane-Design für TLC-NAND präsentiert.

Entwicklungsstand unbekannt

Wie weit die neue 3D-NAND-Generation von YMTC in puncto Marktreife fortgeschritten ist, verrät die Pressemitteilung des Unternehmens aber nicht. So bleibt abzuwarten, wann die Serienfertigung beginnt.

Berichte um „Störfeuer“ aus den USA

Noch vor der Ankündigung von YMTC hatte die Nachrichtenagentur Reuters berichtet, dass die US-Regierung erwägt, die Auslieferung von Anlagen zur Herstellung von Speicherchips mit mehr als 128 Layern in China einzuschränken. Damit sollen die chinesischen Fortschritte im Halbleitersektor eingebremst werden, um US-Firmen wie Micron und Western Digital zu schützen, heißt es weiter. Von einer solchen Maßnahme wäre vor allem YMTC betroffen, aber auch Samsung und SK Hynix besitzen NAND-Flash-Fabriken in China.

Der große Leser-Blindtest Nativ vs. DLSS 4.5 vs. FSR AI!

- Solidigms erste Client-SSD: Die P41 Plus tritt das Erbe der Intel 670p an

- Penta-Level Cell: Solidigm demonstriert erste SSD mit 5 Bit pro Zelle

- Samsung: UFS 4.0 geht in Serie und Memory-semantic SSD geplant

- +8 weitere News