3D-NAND: Intel und SK Hynix setzen neue Maßstäbe bei der Flächendichte

Die jährliche International Solid State Circuits Conference bringt immer wieder erste Details zu kommenden Generationen von NAND-Flash-Speicher hervor. So stellen Intel und SK Hynix Speicherchips in Aussicht, die erstmals eine Flächendichte von über 20 Gbit/mm² aufweisen sollen. Die technische Umsetzung ist sehr unterschiedlich.

Intels PLC-NAND (5 Bit) mit größter Flächendichte

Laut Medienberichten hat Intel auf der ISSCC 2023 einen PLC-Speicher (Penta Level Cell) mit 5 Bit pro Speicherzelle präsentiert, der 1,67 Terabit Speicherplatz auf einer Fläche von 73,3 mm² bietet. Daraus resultiert die nach Kenntnis der Redaktion bisher höchste Flächendichte für NAND-Flash von 23,3 Gbit/mm².

Wie schon zuvor setzt Intel auf eine Floating-Gate-Architektur und stapelt nun 192 Zell-Schichten (Layer) übereinander. Obwohl der Konzern zwischenzeitlich seine Flash- und SSD-Sparte an SK Hynix verkauft hat, woraus das Unternehmen Solidigm entstand, das seinerseits die erste SSD mit PLC-NAND präsentiert hatte, geht die Forschung in diesem Segment offenbar auch bei Intel weiter.

SK Hynix will mit 300-Layer-TLC die 20 Gbit/mm² knacken

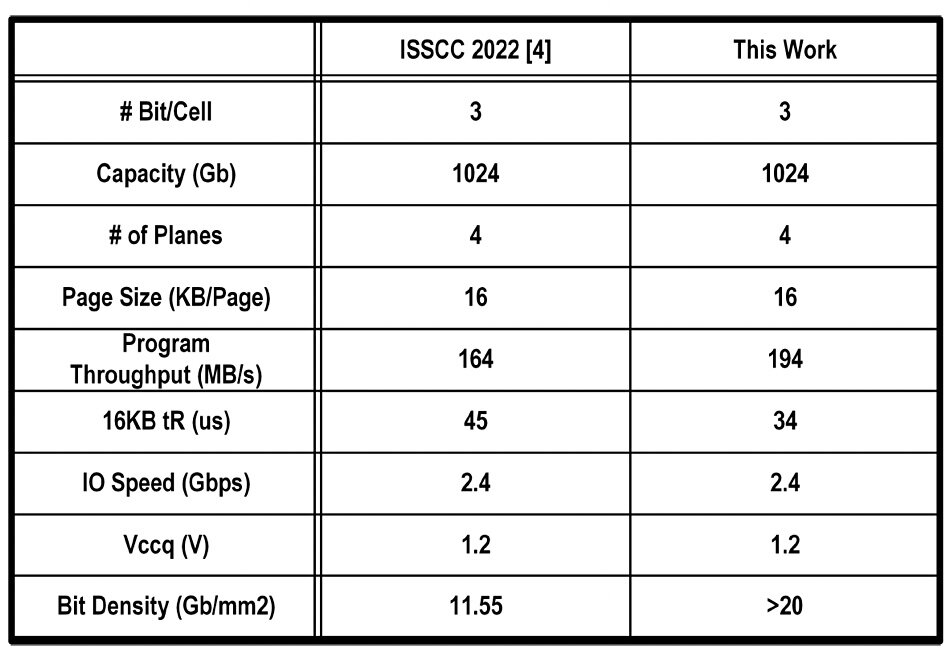

Die Marke von 20 Gbit/mm² will auch SK Hynix knacken. Statt mehr Bit in die Zellen zu packen setzt SK Hynix weiterhin auf 3 Bit (TLC) in Kombination mit deutlich mehr Zellschichten. Der kommende TLC-NAND soll über 300 Layer aufweisen und damit mehr als 20 Gbit/mm² bieten. Die Speicherkapazität bleibt bei 1 Terabit, was also einen wesentlich kleineren Chip bedeuten muss.

Auch in puncto Leistung soll deutlich zugelegt werden. So werden eine Leselatzenz von nur 34 µs und ein Schreibdurchsatz auf Chipebene von 194 MB/s angeführt. Der demnächst in Serie gefertigte 238-Layer-NAND von SK Hynix kommt hingegen auf 45 µs und 164 MB/s. Samsungs V7 als bisheriger Spitzenreiter beim Schreiben würde geschlagen werden.

| Micron B58R | Kioxia/WD BiCS6 | Samsung V8 | Samsung V7 | SK Hynix V9 | SK Hynix V8 | SK Hynix V7 | YMTC | |

|---|---|---|---|---|---|---|---|---|

| Typ (Bit/Zelle) | TLC (3 Bit) | |||||||

| Kapazität | 1 Tbit | 1 Tbit | 512 Gbit | 1 Tbit | 512 Gbit | 1 Tbit | ||

| Planes | 6 | 4 | 6 | |||||

| Layer (WL) | 232 (2×116) | 162 (2×81) | 238 | 176 (2×88) | 300+ | 238 (2×119?) | 176 (2×88) | 232 |

| Die-Fläche | ~70 mm² | 98 mm² | ? | ~60 mm² | ? | ? | ~47 mm² | 68 mm² |

| Dichte | 14,6 Gb/mm² | 10,4 Gb/mm² | 11,5 Gb/mm² | 8,5 Gb/mm² | >20 Gb/mm² | 11,5 Gb/mm² | 10,8 Gb/mm² | 15 Gb/mm² |

| Read (tR) | ? | 50 µs | 45 µs | 40 µs | 34 µs | 45 µs | 50 µs | ? |

| Program | ? | 160 MB/s | 164 MB/s | 184 MB/s | 194 MB/s | 164 MB/s | 168 MB/s | ? |

| I/O | 2,4 Gb/s | 2,0 Gb/s | 2,4 Gb/s | 2,0 Gb/s | 2,4 Gb/s | 1,6 Gb/s | 2,4 Gb/s | |