BiCS8 Flash: Kioxia und WD erhöhen auf 218 Layer mit Waferbonden

Die Flash-Partner Kioxia und Western Digital haben Details zu ihrer nächsten Generation 3D-NAND-Speicher „BiCS8“ enthüllt. Diese soll über 218 Zellschichten (Layer) verfügen und die Bitdichte sowie die Leistung steigern. Ähnlich wie bei YMTC werden Logik und Zellen jeweils auf eigenen Wafern gefertigt und anschließend verbunden.

Dieses sogenannte Waferbonden, das an dieser Stelle als CBA (CMOS directly Bonded to Array) bezeichnet wird, hatte zuerst der chinesische Newcomer YMTC mit seiner Xtacking-Architektur eingeführt. Chip-Logik (I/O) und Speicherbereich werden dabei zunächst getrennt voneinander auf separaten Wafern gefertigt und erst später zu einem Speicherchip vereint. Obwohl somit zwei Wafer benötigt werden, sollen die Kosten insgesamt nicht steigen, da sich auf diesem Weg die Speicherdichte so weit optimieren lasse, dass sich der zusätzliche Wafer rentiere, hieß es bei YMTC.

Speicherdichte und Leistung steigen

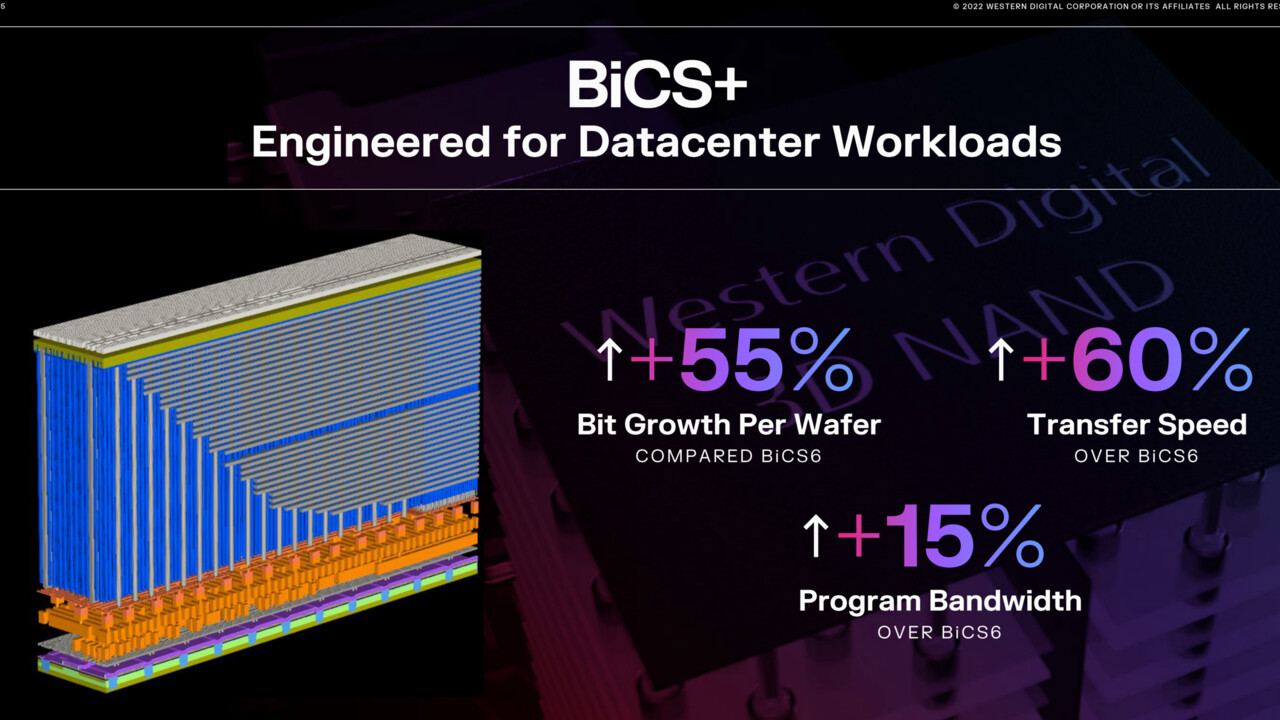

Laut Kioxia und Western Digital soll das neue Design nicht nur die Speicherdichte um 50 Prozent erhöhen, sondern auch die Leistung steigern. Jeweils um 20 Prozent soll die Latenz beim Lesen sowie die Schreibrate verbessert werden. Um satte 60 Prozent soll die interne NAND-Schnittstelle auf über 3,2 Gbit/s beschleunigt werden. Hier wird die TLC-Variante von BiCS 6 mit 2,0 Gbit/s für den Vergleich herangezogen.

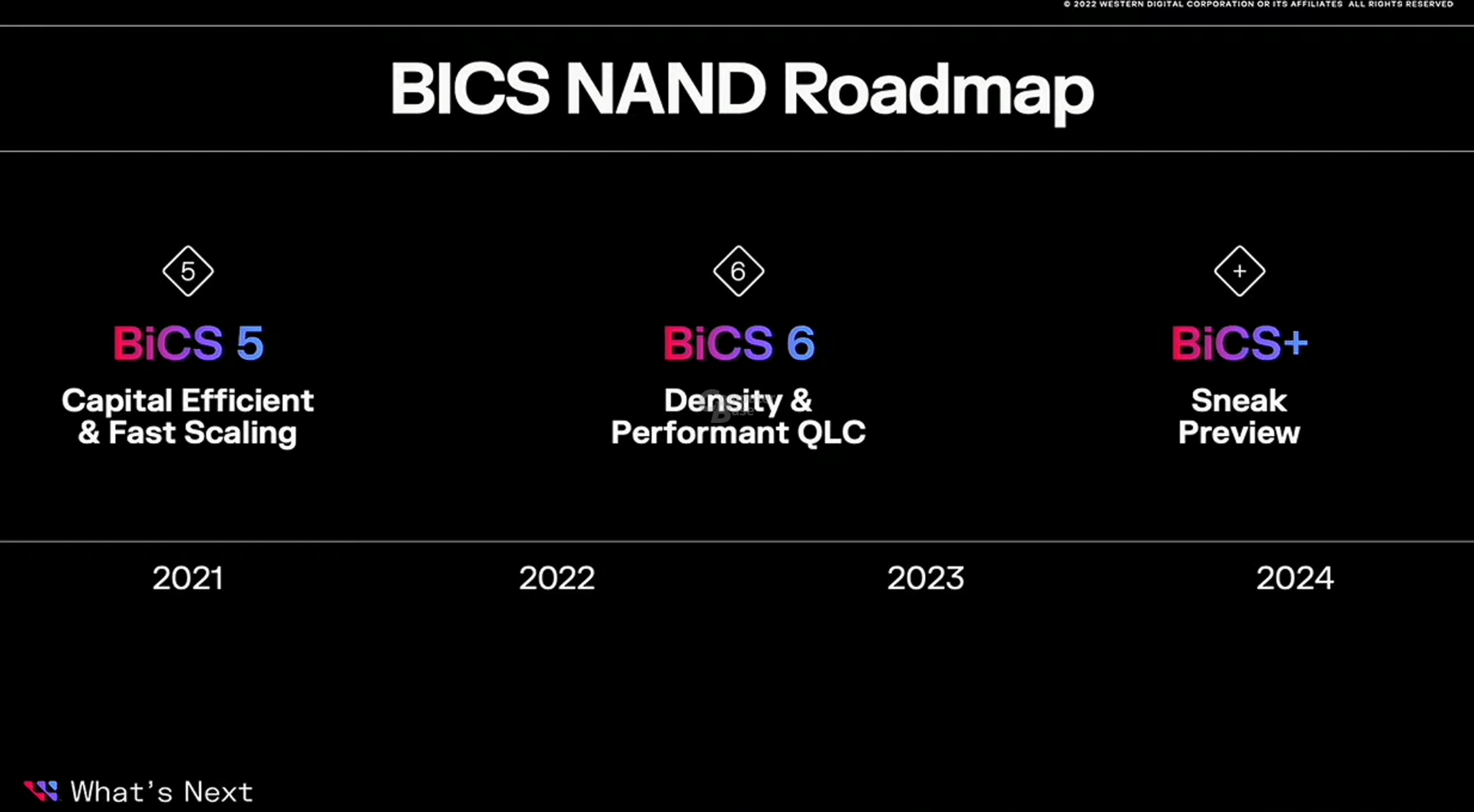

Folgt auf BiCS 6 direkt BiCS 8?

Verwirrend ist allerdings, dass nun von der „achten Generation BiCS Flash“ die Rede ist. Die Roadmap aus dem letzten Jahr hatte als Nachfolger von BiCS 6 lediglich „BiCS+“ genannt. Doch statt des erwarteten BiCS 7 kommt nun direkt BiCS 8? ComputerBase hat Western Digital um eine Erklärung gebeten und wird diese gegebenenfalls nachreichen. Zumindest die nun versprochenen Steigerungen bei Flächendichte, Interface und Schreibleistung (Program) ähneln den zuvor für „BiCS+“ genannten Werten, wie die nachfolgende Bildstrecke zeigt.

Muster des neuen 218-Layer-NAND sollen bereits an einige Geschäftskunden ausgeliefert werden. Wann die Massenfertigung startet oder erste Produkte verfügbar sein werden, lässt die Pressemitteilung aber offen.

Geplant sind TLC- und QLC-Varianten mit 3 Bit und 4 Bit pro Speicherzelle sowie 1 Terabit Speichervolumen pro Chip. Während Micron und YMTC in ihrer jüngsten Generation mit 232-Layern bereits auf ein 6-Plane-Design gewechselt haben, bleibt es bei Kioxia und WD beim 4-Plane-Design.

Die Antwort hat lange auf sich warten lassen, aber ein Sprecher von Western Digital hat auf Nachfrage der Redaktion inzwischen bestätigt, dass es sich bei BiCS8 um die zuvor „BiCS+“ genannte Generation handelt. Warum es kein „BiCS7“ gegeben hat, wurde aber nicht erklärt. Die Leistungsvergleiche zum Vorgänger beziehen sich also auf BiCS8 versus BiCS6.