Zen 4c „Bergamo“: AMDs 16-Kern-CCD benötigt nur 9,6 % mehr Fläche als 8 Kerne

AMD greift beim in der kommenden Woche erwarteten ersten Zen-4c-Prozessor „Bergamo“ tief in die Trickkiste und bringt Erstaunliches hervor. Denn statt wie vorab vermutet die Caches deutlich zu kastrieren, werden Möglichkeiten des Auftragsfertigers TSMC umgesetzt, die eine extrem dicht gepackte Lösung ermöglichen.

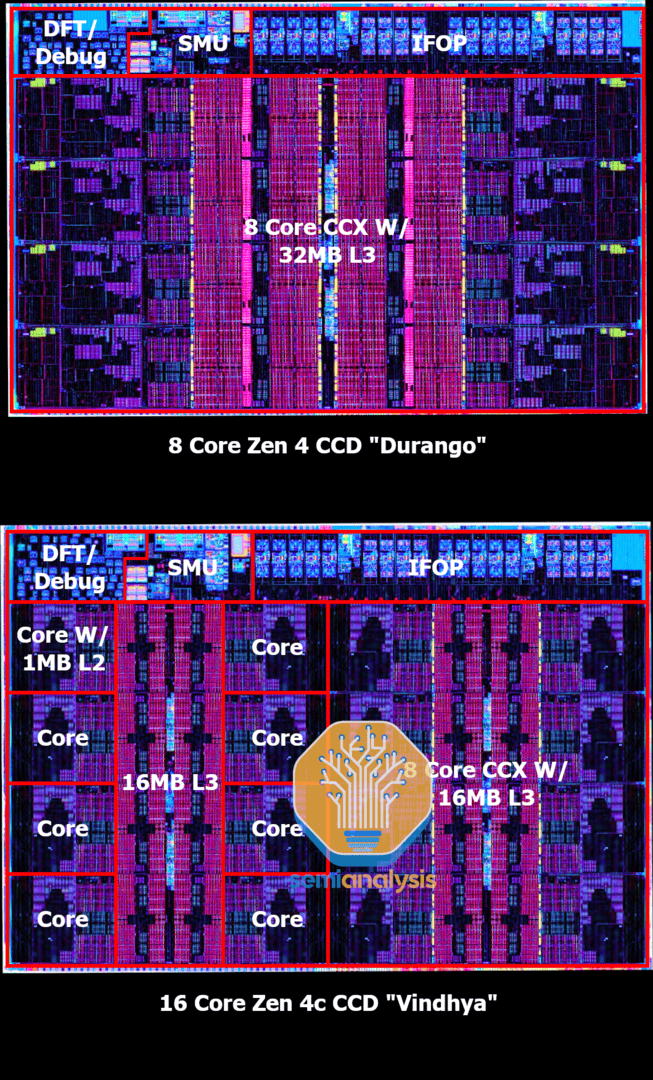

AMD presst 16 Kerne mit den exakt gleichen Caches in quasi das Format, was es bisher für 8 Kerne gab. Das einzige, was dabei nicht mitwächst, ist der L3-Cache, der bleibt im CCD bei 32 MByte – effektiv ist er hier pro Kern also halbiert. Da AMD am Ende auf den Prozessor aber 33 Prozent mehr Kerne packt, sinkt der L3-Cache nur von 384 MByte bei Genoa mit 96 Kernen auf 256 MByte L3-Cache mit Bergamo und 128 Kernen.

Dass die 16 Kerne nebst 32 MByte L3-Cache in Bergamo nur 72,7 mm² belegen ist extrem überraschend, gab AMD für acht Kerne und 32 MByte L3-Cache doch bereits 66,3 mm² Flächennutzung an. Und dies wird in der gleichen N5-Fertigung realisiert, wobei gleich nicht dasselbe ist. Denn zugrunde liegen einige Raffinessen, die das erst ermöglichen. Aber auch auf einen Verzicht hier und da, beispielsweise auf die TSVs, die für einen gestackten L3-Cache beim bisherigen Zen-4-Design stets mit dabei waren. Das wird es bei Bergamo nicht geben, macht im Umkehrschluss aber Platz frei.

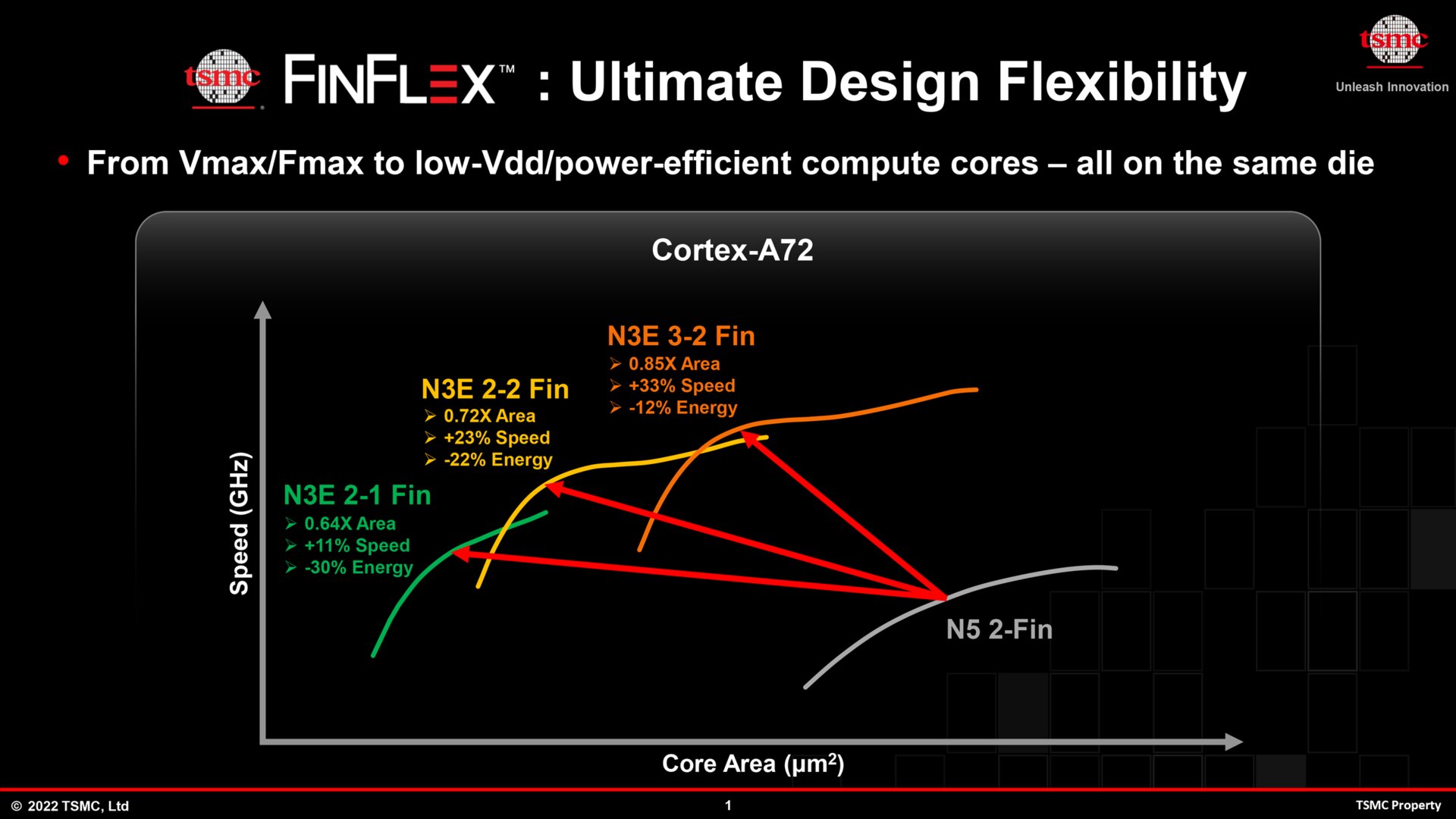

Die Möglichkeiten, einen Chip kleiner zu machen und alles etwas enger zu packen sind begrenzt, aber vorhanden. Die erste ist, den Chip nicht so hoch takten zu lassen – genau das wird unter anderem bei Bergamo genutzt. TSMC hatte zur Vorstellung der fünf N3-Technologien dies in den Fokus gerückt, das Schaubild zeigt aber auch auf der N5-Kurve, dass es stets eine Wahl zwischen mehr Leistung oder deutlich geringerer Fläche gibt. Die jeweiligen Linien entsprechen dabei den Punkten, die TSMC auch adressiert, selbst N5 kann hier deutlich kleiner werden als ein anderes N5-Produkt, ohne dabei massiv an Geschwindigkeit einzubüßen.

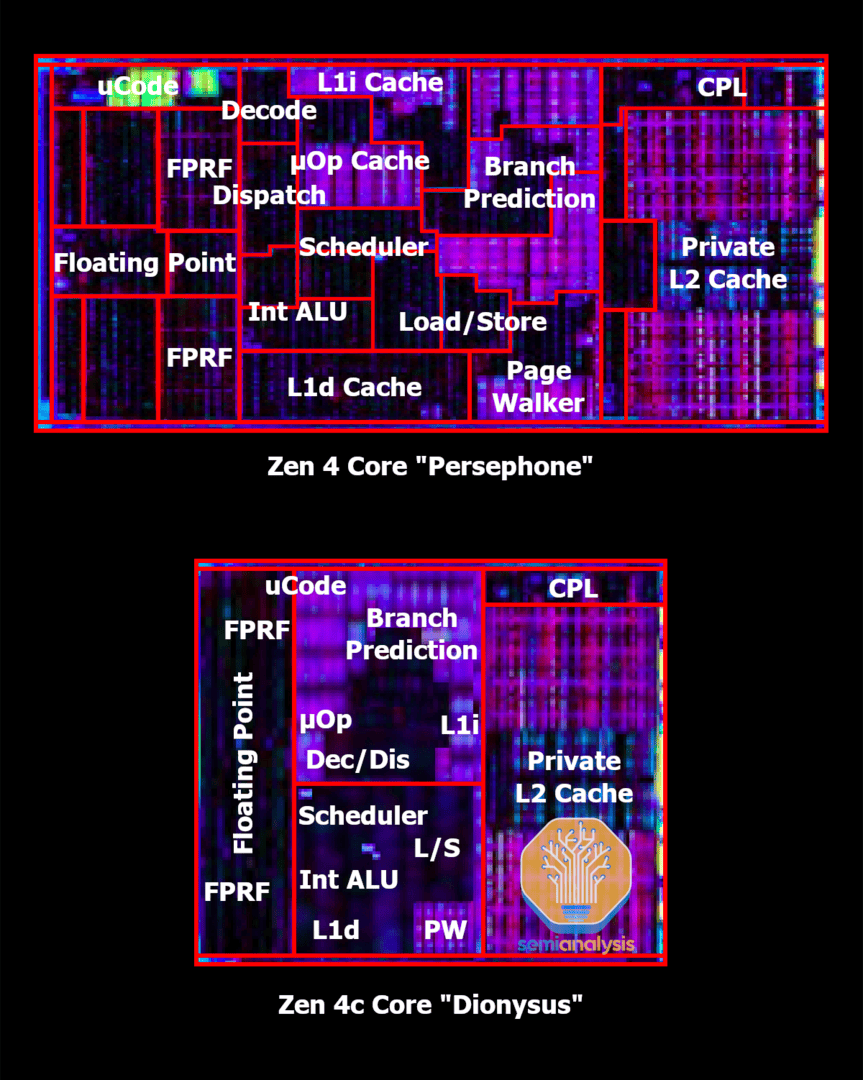

Aber allein das reicht nicht: Der eigentliche Kern wurde komplett umgestaltet, alle Dinge darin neu sortiert. Statt ein wenig unaufgeräumt zu wirken, ist der Kern nun deutlich linearer gestaltet. Anschaulich betrachtet, hat sich der Kern inklusive L2-Cache in der Fläche fast halbiert, im Detail betrachtet steht ein Minus von rund 35 Prozent, einige Teile wurden aber wirklich flächenmäßig quasi halbiert. Auch die Verwendung neuer und deutlich kleinerer 6T-SRAM-Zellen statt 8T helfen hier – diese Entwicklung ist TSMC zu verdanken.

-

Ein Zen-4-Kern oben, Zen 4c unten (Bild: Semi Analysis)

Ein Zen-4-Kern oben, Zen 4c unten (Bild: Semi Analysis)

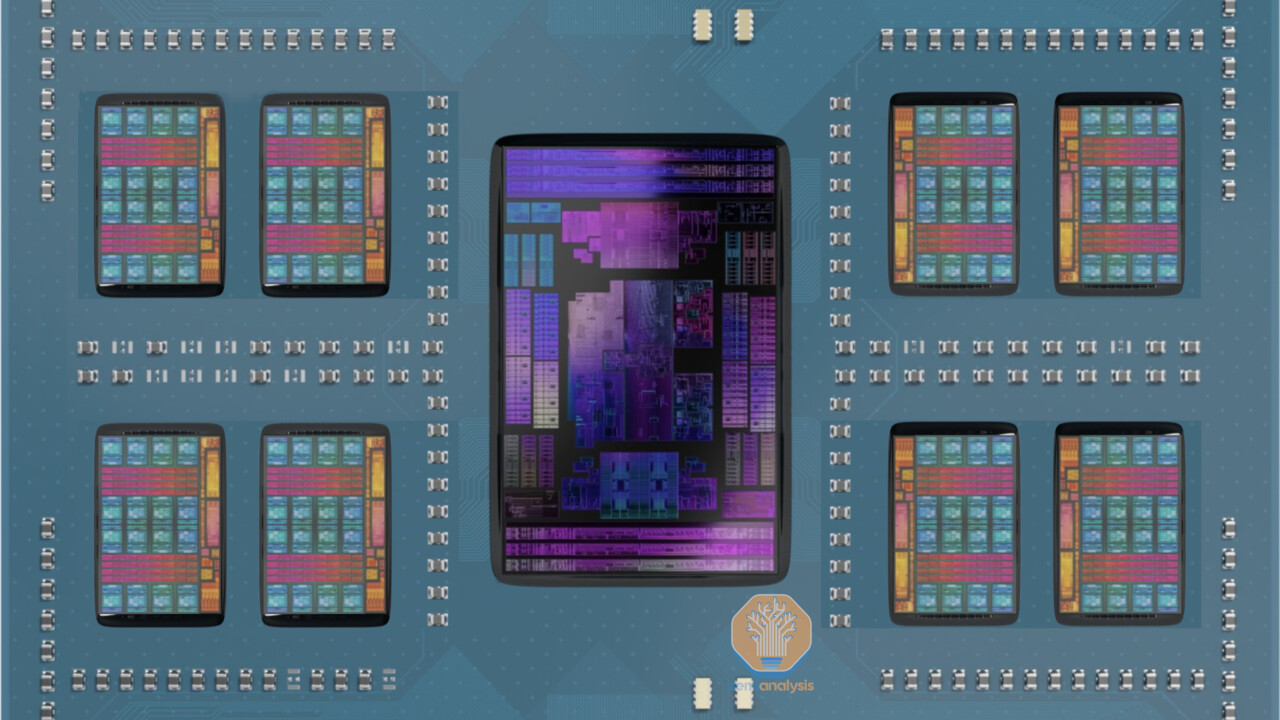

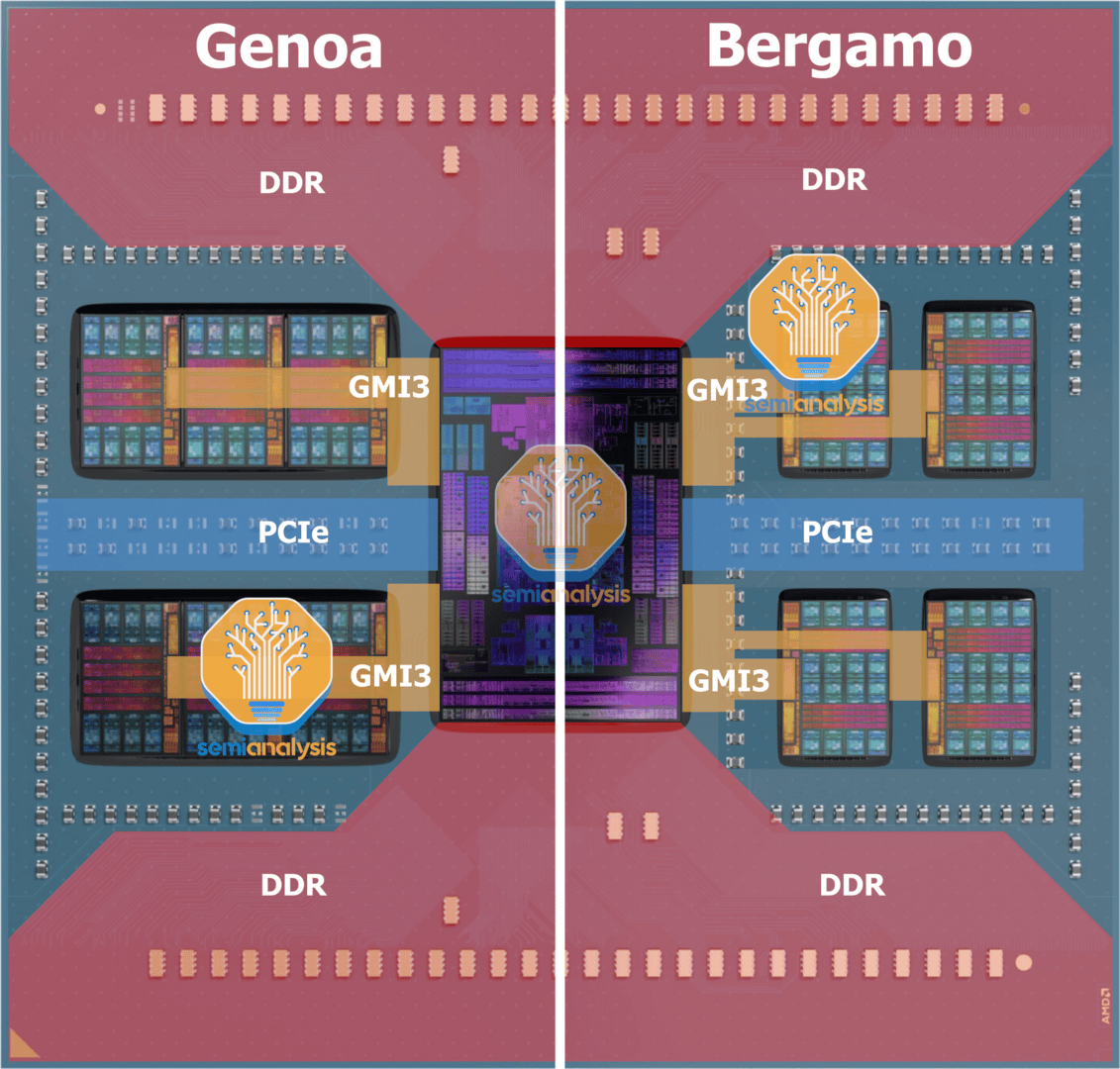

Acht von diesen kleinen Kernen kombiniert AMD mit 16 MByte L3-Cache in einem CCX, verbindet diese mit einem weiteren CCX zu einem CCD. Acht von diesen CCDs sind letztlich auf einem Bergamo-Prozessor zu finden, der I/O-Chip in der Mitte ist identisch zu Genoa, so letztlich auch alle Parameter wie Speichercontroller, PCIe 5.0 und der ganze Rest. Und genau das ist wichtig, denn so muss keine Software angepasst werden, auch der Prozessorsockel SP5 ist vollständig kompatibel.

-

Genoa links, Bergamo rechts (Bild: Semi Analysis)

Genoa links, Bergamo rechts (Bild: Semi Analysis)

Am Ende steht die Frage, ob AMD nicht einfach wieder 12 CCDs wie bei Genoa auf ein Package hätte packen können um so direkt 192-Kern-Bergamo zu ermöglichen. Hier steht jedoch vorerst ein Nein, das Package ist nun der limitierende Faktor. Die Lehren aus der ersten Generation des c-Designs werden jedoch flott gezogen, weshalb die bereits spekulierten 192 Kerne bei Zen 5c möglich werden dürften.

Es wird erwartet, dass Bergamo im Rahmen der für den 13. Juni 2023 angesetzten „Data Center and AI Technology Premiere“ vorgestellt wird, letzte Gerüchte hatten zwei Modelle bestätigt.