AMD Ryzen 8000: Strix Point mit 4+8c- und Strix Halo mit 16 Zen-5-Kernen

Bereits vor über zwei Jahren geisterte das erste Mal AMD Strix Point umher. Nun wird es langsam konkreter, 2024 sollen die Prozessoren erscheinen. AMD wird dabei im Notebook-Umfeld mindestens eine Zweiteilung mit unterschiedlicher Leistung beibehalten, insgesamt wird den APUs viel mehr Leistung zur Verfügung gestellt als bisher.

Was AMD derzeit mit den Phoenix-APUs macht und dabei hinter den Kulissen als „Phoenix2“ auflegt, die erstmals Zen-4c-Kerne nutzen, wird als Testlauf für das kommende Jahr gesehen. Denn Strix Point als Mainstream-Lösung soll exakt so eine Kombination dann mit modernen Zen-5-Varianten nutzen: Vier große Zen-5-Kerne sollen auf acht Zen-5c-Kerne treffen.

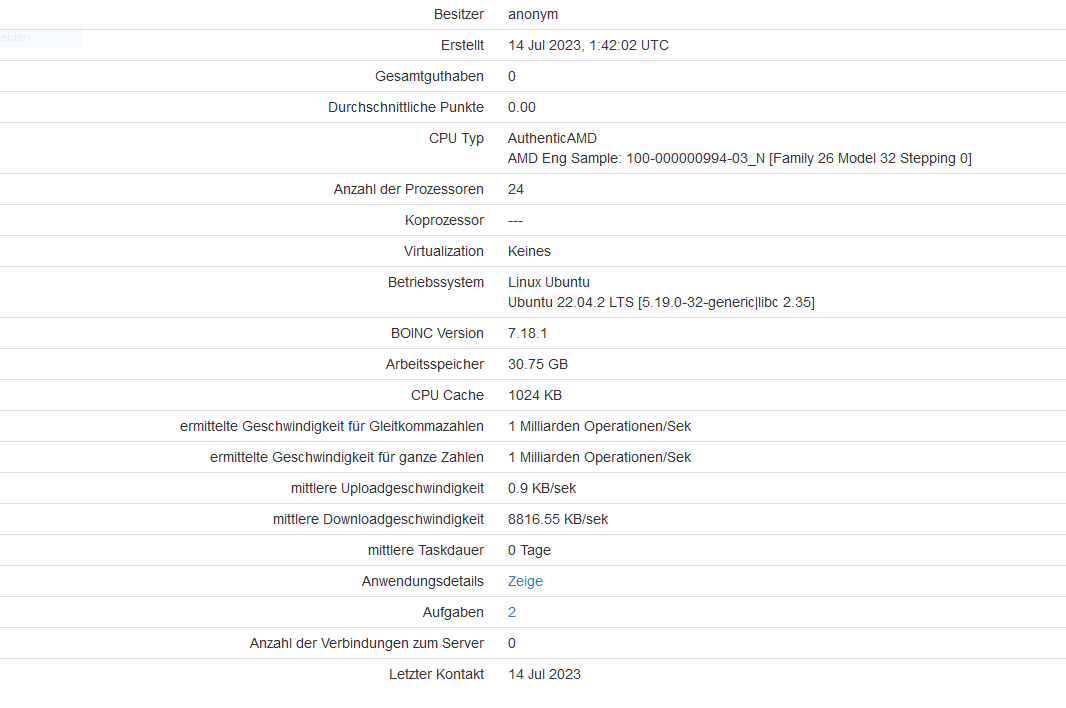

Bereits vor über zwei Jahren gingen die Gerüchte in Richtung eines big.LITTLE-Konzeptes von AMD, was es in gewisser Weise auch ist, nur dass mit dem heutigen Wissen eher „big.BIGGER“ zutreffen würde. Zuletzt tauchten Benchmarks von einer 12-Kerne-AMD-APU auf, denen eine 4+8C-Version zugrunde lag: 24 Threads werden dank SMT-Unterstützung nämlich so realisiert.

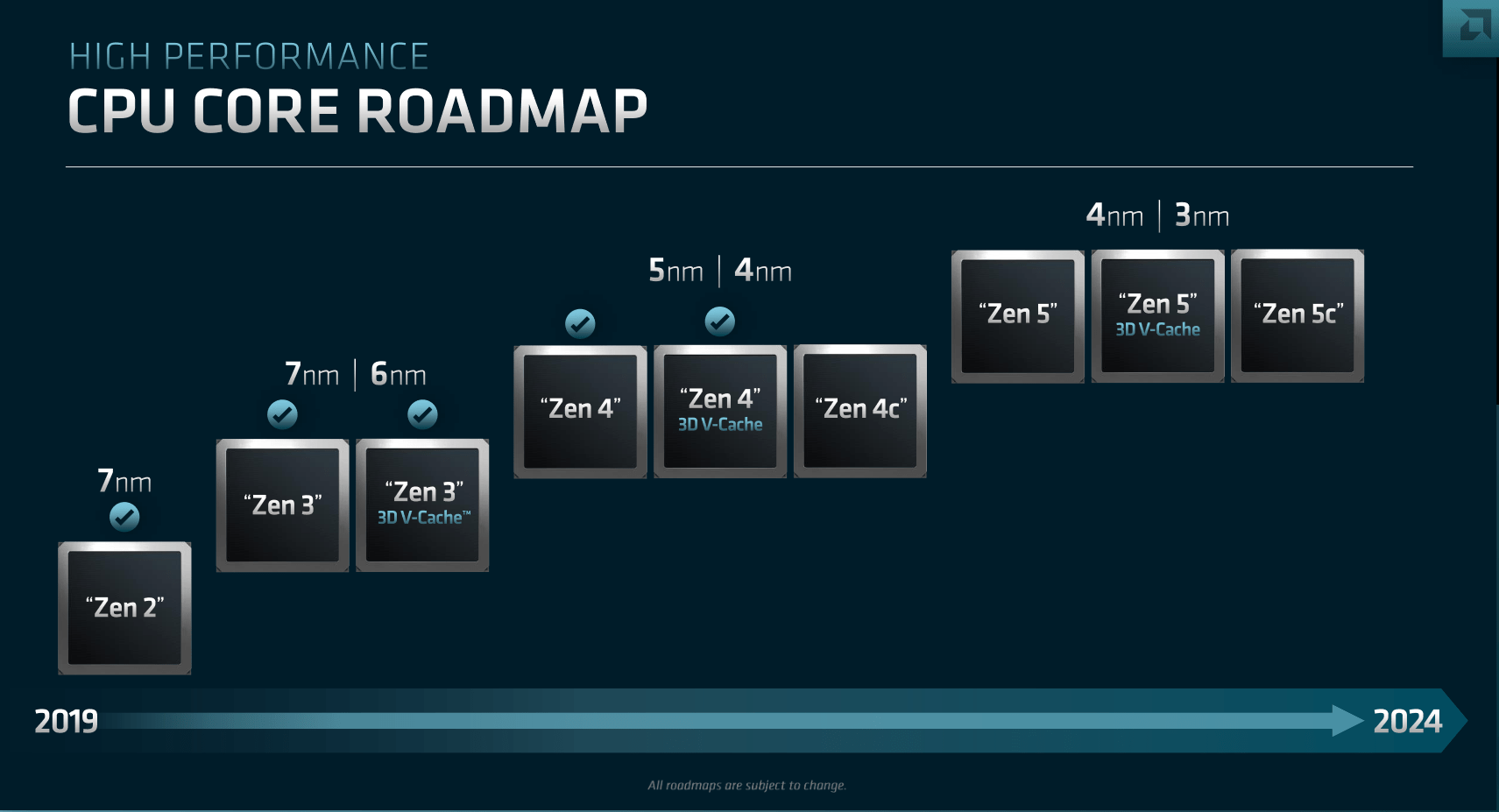

Kürzlich hatte AMD im Rahmen eines Partner-Webinars eine Roadmap gezeigt, die auch Ryzen 8000 mit Zen-5-CPU-Kernen und „Navi 3.5“-GPU offenbarte. Zuvor hatte AMD bereits RDNA3+ genannt. Strix Point wird diese Grafikeinheit nutzen und gegenüber der aktuellen Phoenix-Lösung die Anzahl der CUs von 12 auf 16 steigern.

Halo-Produkt der Strix-Familie mit großer iGPU

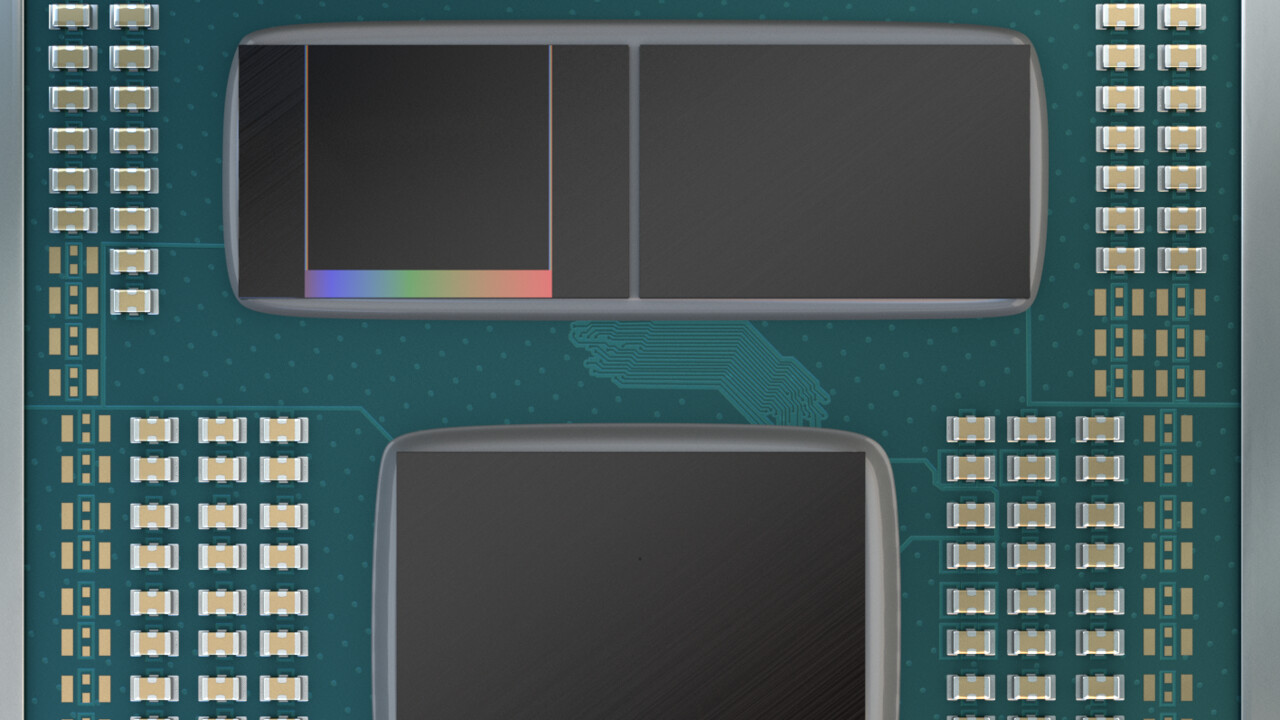

Interessant wird jedoch, was AMD im Portfolio darüber machen wird. Mit Dragon Range (Test) hatte AMD praktisch die Desktop-Chips ins Notebook gesetzt. Diesen Schritt scheint man zum Teil fortzusetzen, jedoch mit Anpassungen zurück in Richtung APU, sprich mit einer größeren integrierten Grafikeinheit. So könnten zwei Zen-5-CPU-Dies mit jeweils 8 Kernen wie im Desktop-Chip Granite Ridge mit einem riesigen Grafikteil über einen angepasstem I/O-Die kombiniert werden, der bis zu 40 CUs fassen soll.

Der Chiplet-Ansatz, den AMD seit einigen Jahren verfolgt, würde dies ermöglichen. Aktuell nutzt AMD die reinen Zen-4-Dies aus TSMCs N5-Fertigung, der I/O-Die wird in TSMC N6 gefertigt, also einem optimierten und günstigeren 7-nm-Prozess. Eine Zweiteilung wird hier auch in Zukunft erwartet, jedoch alles mindestens einen Schritt nach vorne gehen, so wie es die APUs bereits vorleben: Die N4-Fertigung von TSMC dürfte vermutlich in ihren Ausbaustufen N4P und N4X viel Gewicht zufallen, im Idealfall könnten Lösungen mit Fokus aufs Stromsparen Ende 2024 auch bereits mit einem N3-Prozess folgen. AMD hatte diplomatisch bisher einfach stets alle Fertigungsstufen genannt oder lediglich von „Advanced“ gesprochen.

Am Wochenende tauchten weitere Gerüchte zur APU Strix Point auf. Diese untermauern das bereits benannte Kern-Zusammenspiel aus regulären und C-Kernen, geben aber auch zusätzliche Details zur L3-Cache-Ausstattung und der Grafik. 8 WGPs entsprechen nach aktuellem Stand 16 CUs, das wiederum passt zu den bereits zuvor genannten Gerüchten. Bei L3-Cache müssen die C-Kerne auf eine Menge verzichten, hier gibt es für acht Kerne nur 8 MByte L3-Cache, der zweite CCX mit vier großen Zen-5-Kernen bietet angeblich 16 MByte. Unterm Strich bietet die APU mit 12 Kernen und 24 Threads dann 24 MByte L3-Cache.