2 × 2,5 Bit = 5 Bit: SK Hynix will PLC-NAND so schnell wie TLC machen

Um künftig 5 Bit in einer Flash-Speicherzelle unterzubringen, forscht SK Hynix ähnlich wie Kioxia und Western Digital an einer „geteilten“ Zelle. Effektiv werden zweimal 2,5 Bit gespeichert, was wesentlich schneller als einmal 5 Bit vonstattengehe.

Multi-Site-Zellen für mehr als 4 Bit

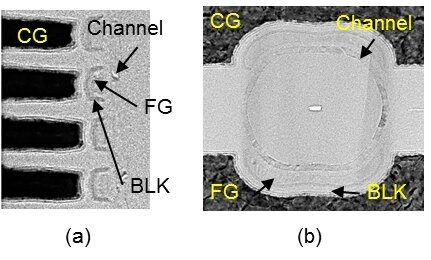

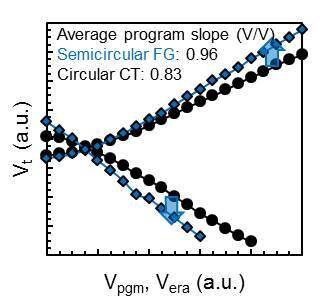

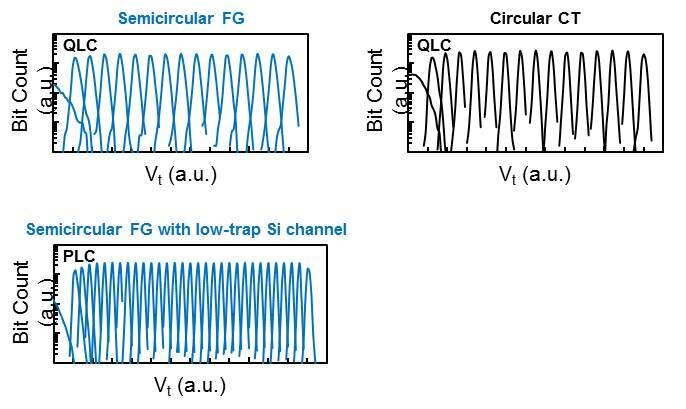

SK Hynix spricht zum Flash Memory Summit 2023 von einer Multi-Site-Zelle auf Basis der Charge-Trap-Flash-Architektur. Die beiden Zellhälften sind getrennt, aber teilen sich eine Bit-Line. Pro „Site“ werden 2,5 Bit gespeichert, wofür lediglich 6 unterschiedliche Spannungen nötig sind. Zusammen ergeben sich 5 Bit bei nur 12 zu unterscheidenden Spannungsleveln. Wäre die Zelle nicht derart geteilt, müssten hingegen ganze 32 Level unterschieden werden.

Je mehr Spannungslevel nötig sind, umso komplexer und entsprechend langsamer ist der Speichervorgang, also das Schreiben von Daten in die Zellen. Zudem nimmt die Haltbarkeit potenziell ab. Daher ist QLC-NAND mit 4 Bit (16 Level) auch deutlich langsamer als TLC mit 3 Bit (8 Level).

Zwei halbe sind schneller als eine ganze

Dank des Tricks mit einer Teilung der Zellen, werden die nötigen Spannungszustände drastisch reduziert und so sollen Daten auch viel schneller geschrieben werden. SK Hynix spricht von ähnlichen Schreibraten wie bei TLC-NAND. Wäre die Zelle nicht aufgeteilt, würde die Schreibrate etwa 20 Mal langsamer als bei TLC ausfallen, argumentiert das Unternehmen auf einer Folie.

Kioxia erwägt ebenso halbierte Zellen

Dieser Ansatz mit geteilten Speicherzellen ist nicht neu, denn Kioxia und Western Digital, die gemeinsam 3D-NAND entwickeln und produzieren, haben schon 2019 ihre Überlegungen zu einer halbierten Speicherzelle unter dem Arbeitsnamen „Twin BiCS Flash“ veröffentlicht.

Bei Solidigm gibt es PLC-NAND schon

Solidigm ist schon weiter und hat vor einem Jahr die erste SSD mit PLC-NAND demonstriert. Im Februar hat das aus Intels ehemaliger NAND-Sparte entstandene Unternehmen einige Details zu seinem PLC-Speicher verraten. Demnach setzt Solidigm wie beim aktuellen QLC-NAND auf 192 Zellschichten (Layer). Dank 5 statt 4 Bit pro Zelle steigt die Flächendichte aber auf 23,3 Gbit/mm², was den bisherigen Rekord markiert.

Doch will SK Hynix mit seinem neuen TLC-NAND der V9-Generation mit satten 321 Layern sogar auf über 20 Gbit/mm² kommen und somit mit nur 3 Bit pro Zelle in ähnliche Regionen vorstoßen. Mehr Layer bedeuten allerdings auch mehr Arbeitsschritte und Kosten.

Da Solidigm ein Tochterunternehmen von SK Hynix ist, hat der südkoreanische Konzern praktisch beide Ansätze für PLC-NAND unter einem Dach.

Ihr habt die Wahl: Macht mit bei den Reader's Choice Awards 2025 und bestimmt eure Hersteller des Jahres!

- 2 × 2,5 Bit = 5 Bit: SK Hynix will PLC-NAND so schnell wie TLC machen

- Flash Memory Summit: SK Hynix entwickelt 321-Layer-TLC-NAND

- Seagate Nytro 5060: Neue SSD-Generation mit bis zu 13 GB/s und 30 TB für Server

- +6 weitere News