Intel-Xeon-Architektur: Granite Rapids und Sierra Forest mit 144 Kernen detailliert

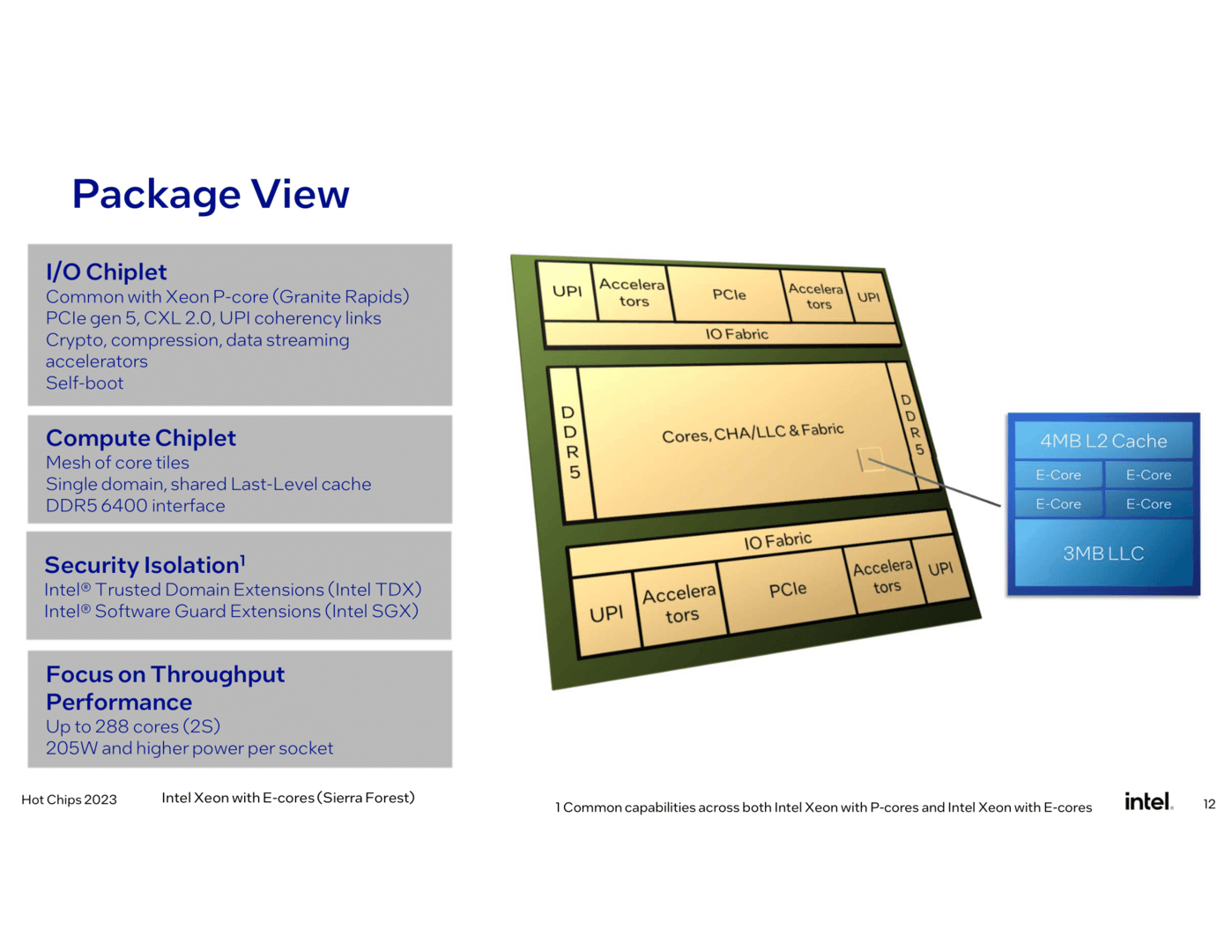

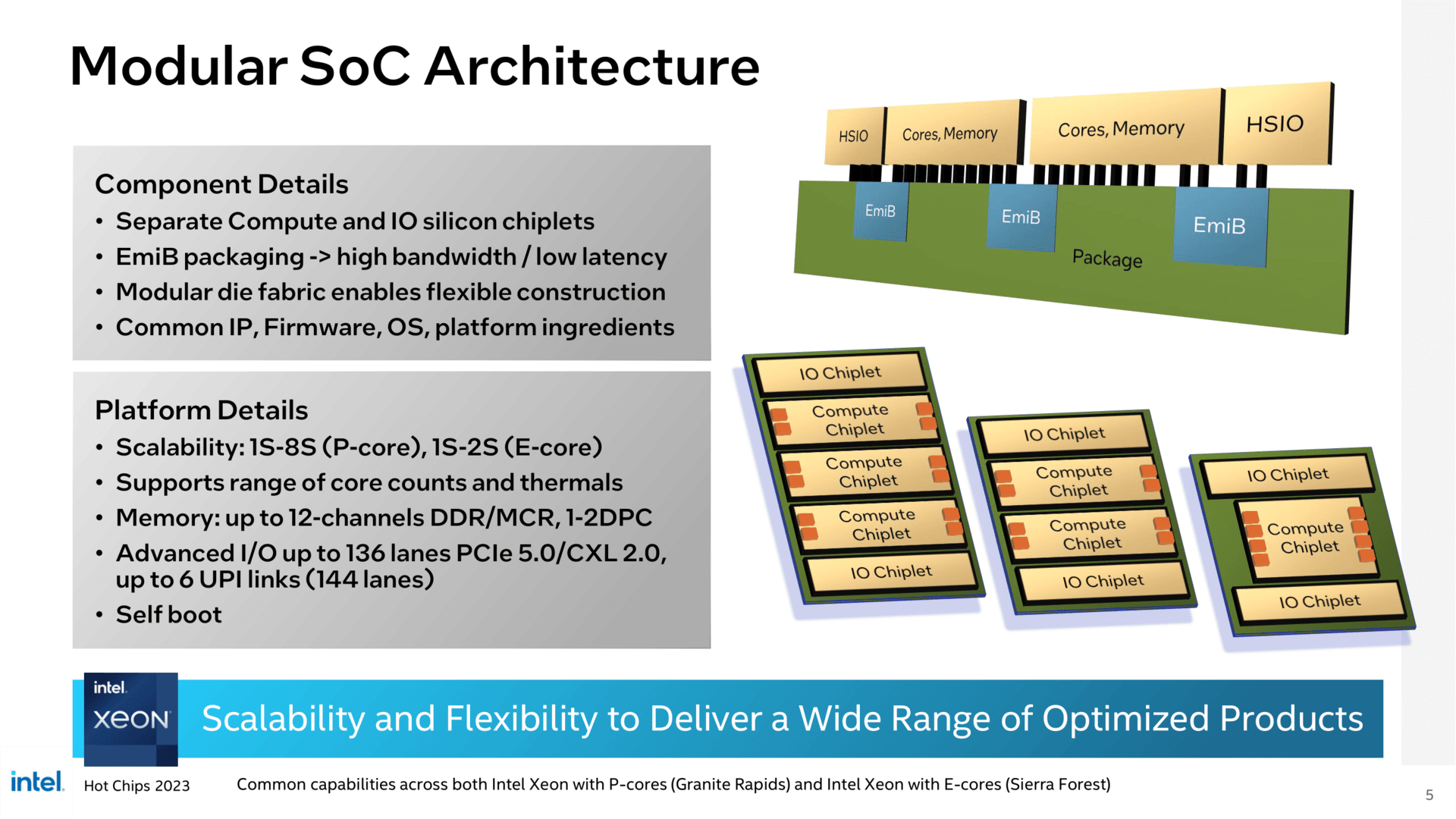

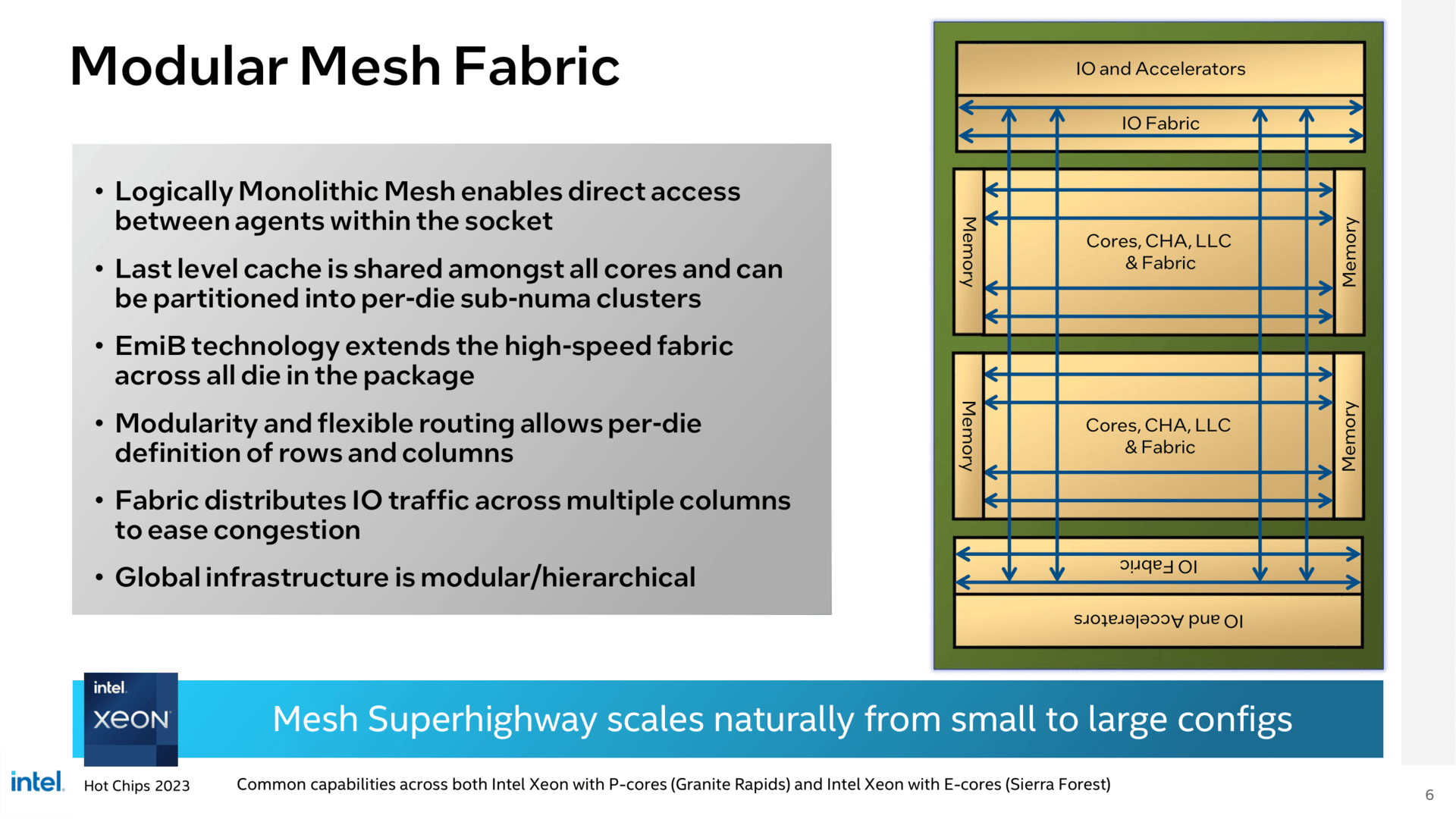

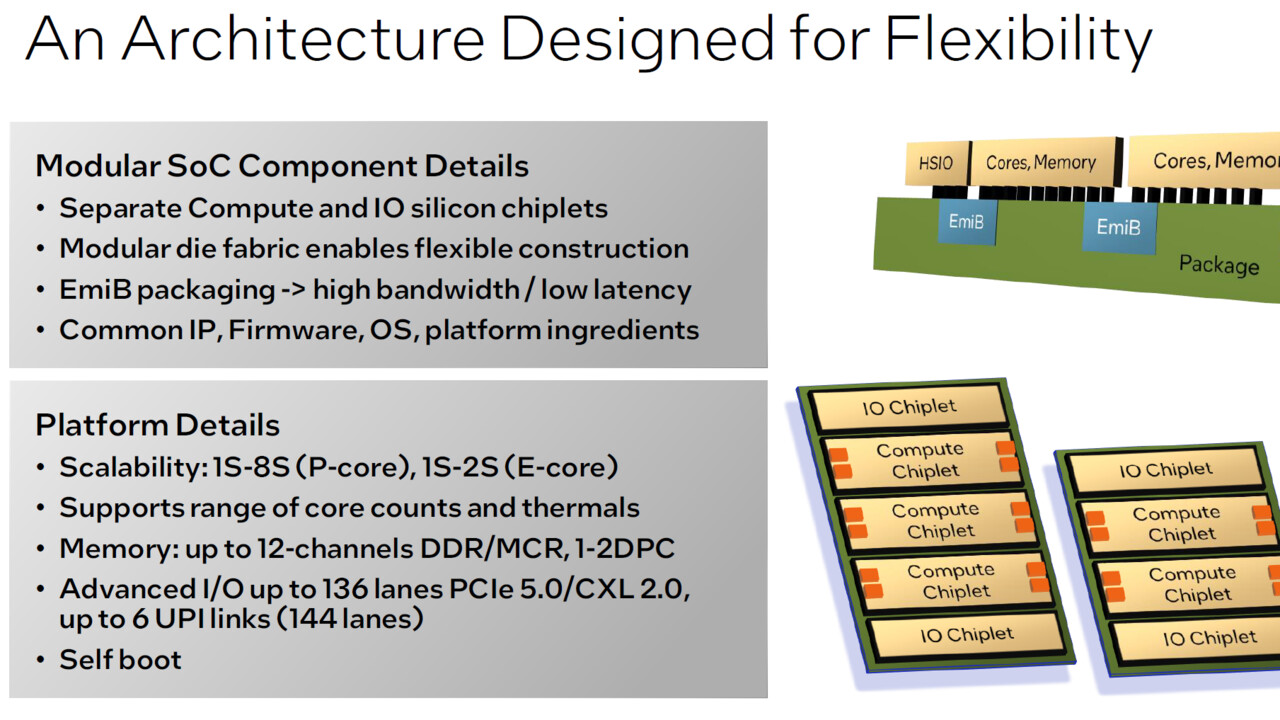

Xeon im Jahr 2024 sollen vor allem für eines stehen: Skalierbarkeit. Deshalb gibt Intel zur Hot Chips 23 einen detaillierten Blick auf Granite Rapids und Sierra Forest. Dabei bedient sich Intel der Mix-&-Match-Technik und packt zu zwei I/O-Chips ein, zwei oder drei Compute-Tiles mit P-Cores oder mit E-Cores.

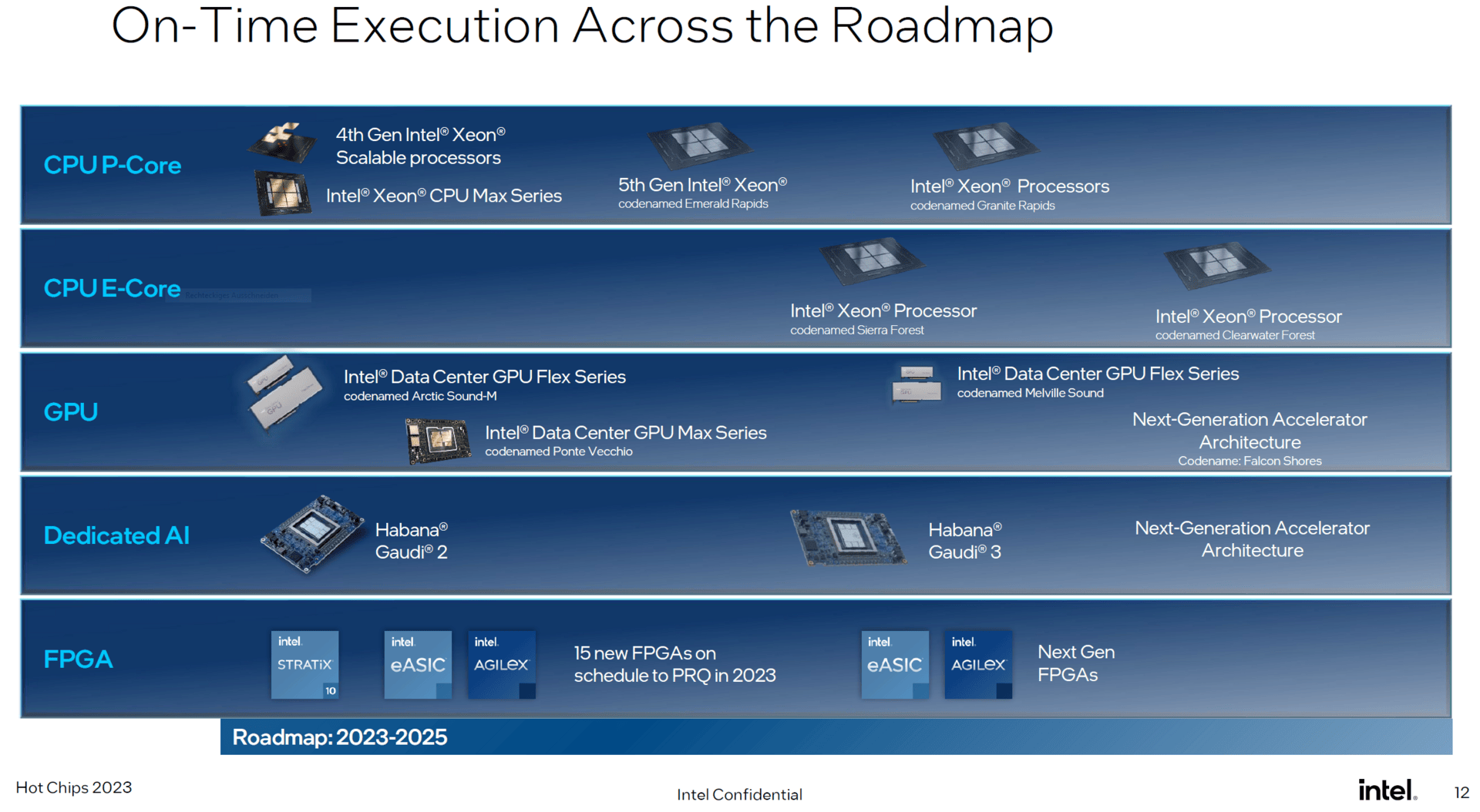

Intels Xeon-Roadmap ist voller Neuheiten

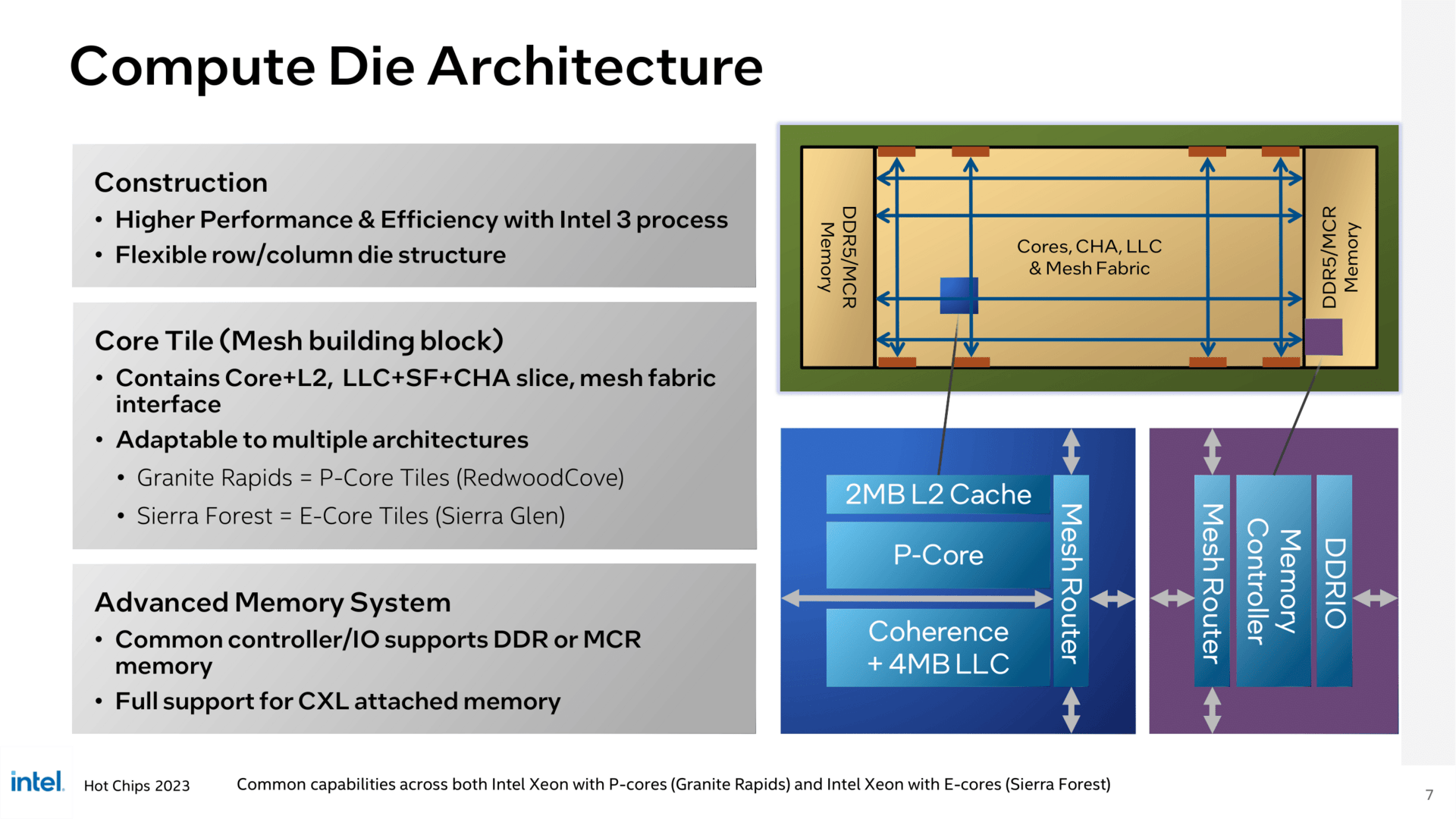

Intels Ansatz, in Zukunft alles mit Tiles – auch Chiplets genannt – zu machen, offenbart sich nicht nur bei der ersten Consumer-Lösung Meteor Lake, sondern auch bei Granite Rapids und Sierra Forest wird das Ganze deutlich. Denn hier wird ein Mix-&-Match mit verschiedenen CPU-Tiles möglich sein, die trotz des Einsatzes auf derselben Plattform ganz unterschiedliche Features bieten können.

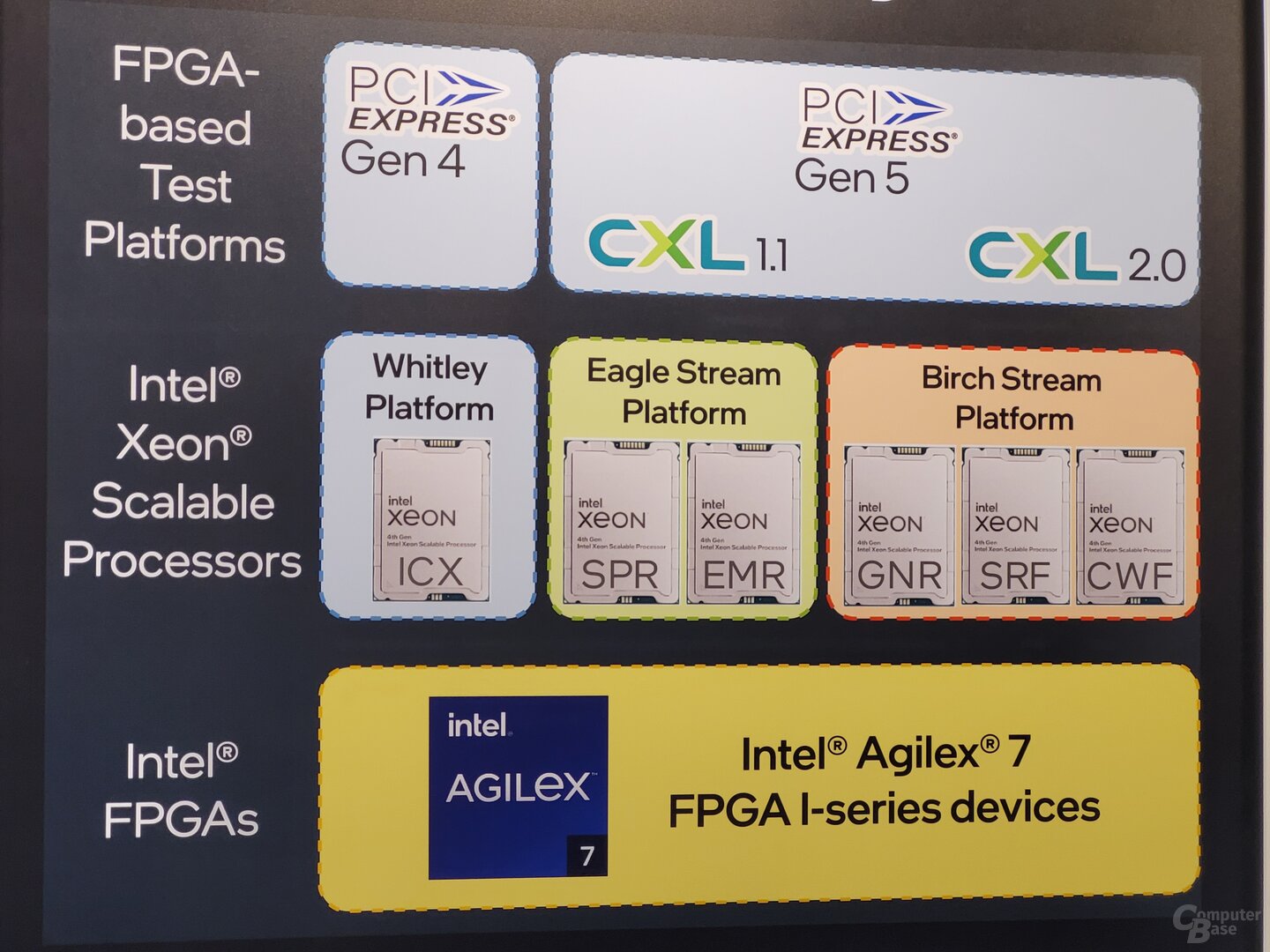

Birch Stream, so der Codename der Plattform, soll so nicht nur die erste Generation dieser Kachel-CPUs angeführt von Granite Rapids aufnehmen, sondern Clearwater Forest (CWF) als zweite Lösung nach Sierra Forest soll hier ebenfalls ihren Platz finden.

Wahlweise P- oder E-Cores aus Intel-3-Fertigung

Was der Kunde letztlich mit der Birch-Stream-Plattform machen will, entscheidet er über die Wahl der Kerne: Sehr viele E-Cores für maximale Parallelisierung oder weniger, dafür leistungsfähigere P-Cores schaffen letztlich zwei Prozessorfamilien: Sierra Forest und Granite Rapids. Beide Core-Typen kommen aus der Intel-3-Fertigung.

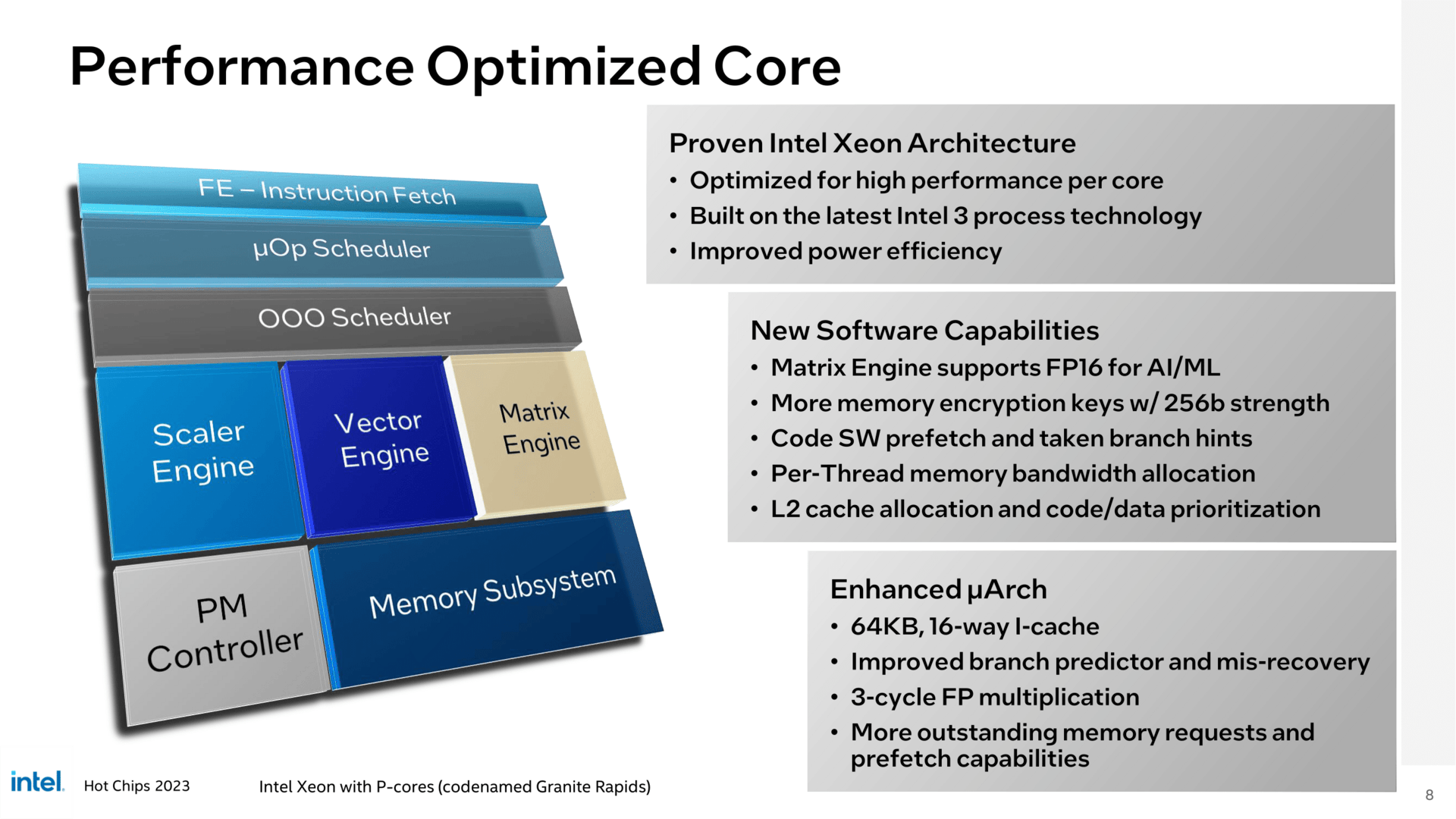

Granite Rapids als klassischer Performance-Xeon

Granite Rapids ist die P-Core-Lösung, Codename Redwood Cove, und optimiert für Server. Intel verfolgt hier den Ansatz, dass größere Caches in einigen Bereichen auch mehr Leistung bringen. Für Instruktionen gibt es 64 KB pro Kern. Die Kerne selbst bekommen ihre typische Überarbeitung beginnend bei der Sprungvorhersage, den Prefetchern, zusätzlichen Instruktionen und mehr. Ins exakte Detail geht Intel hier heute jedoch nicht.

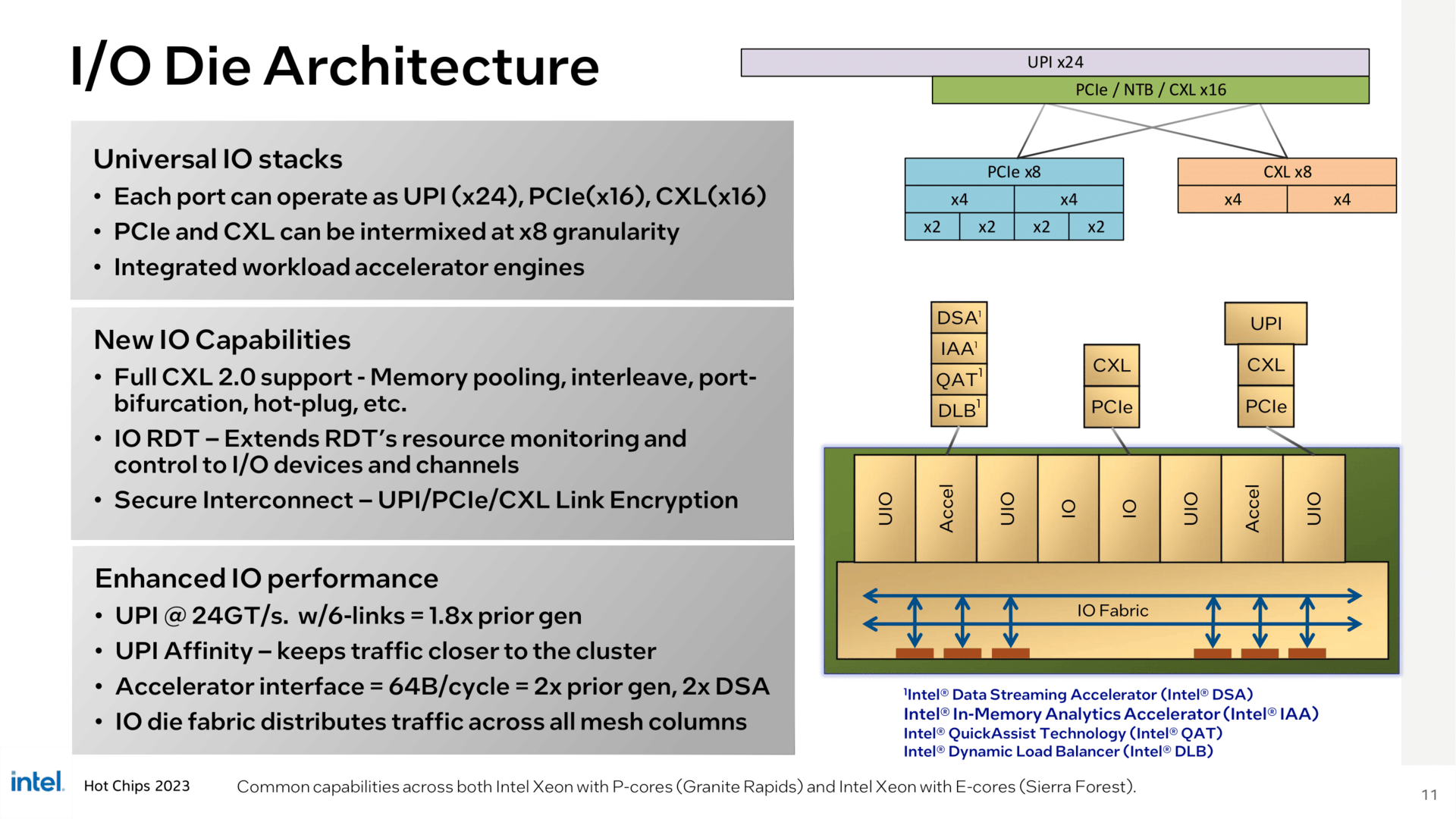

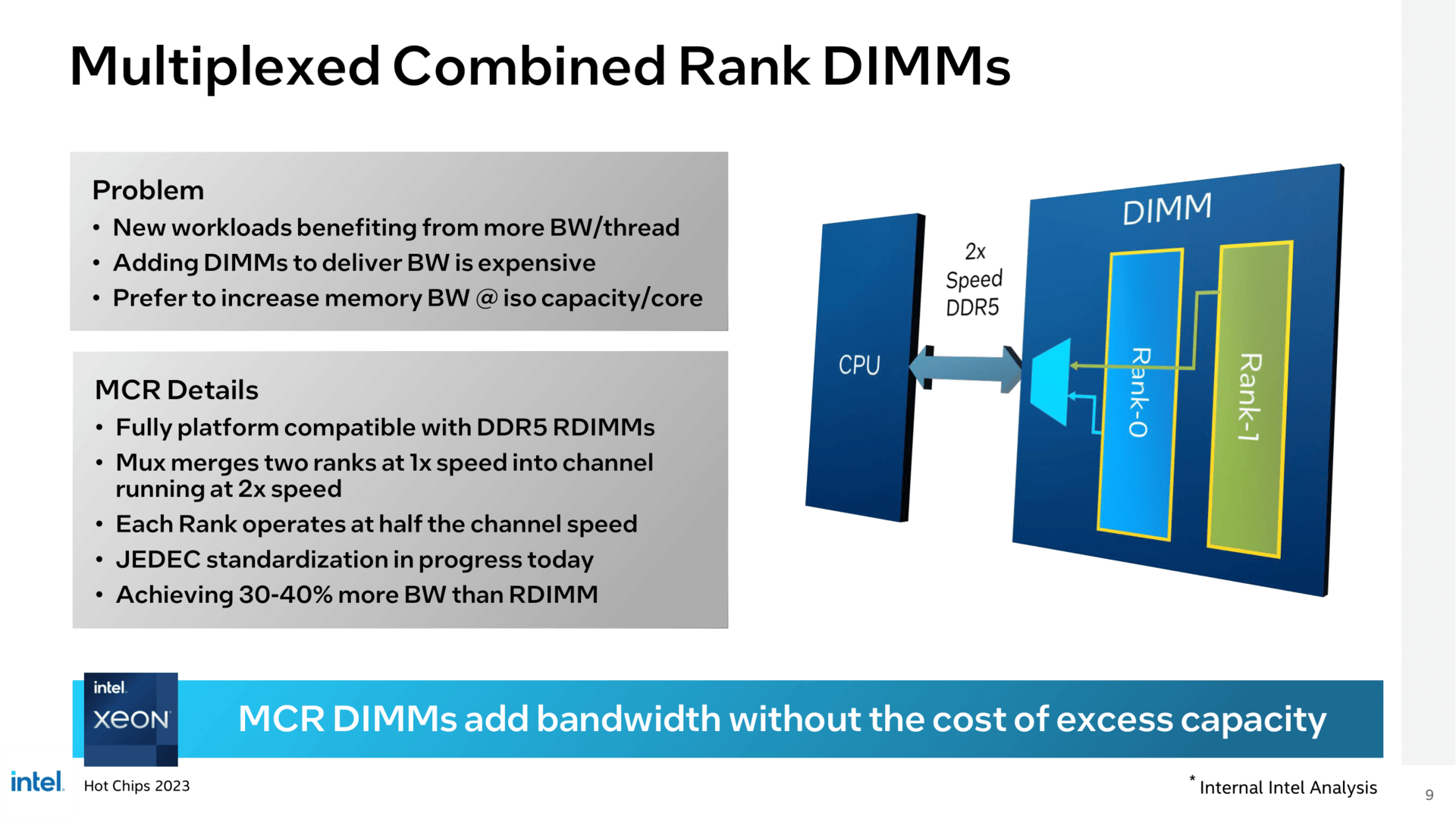

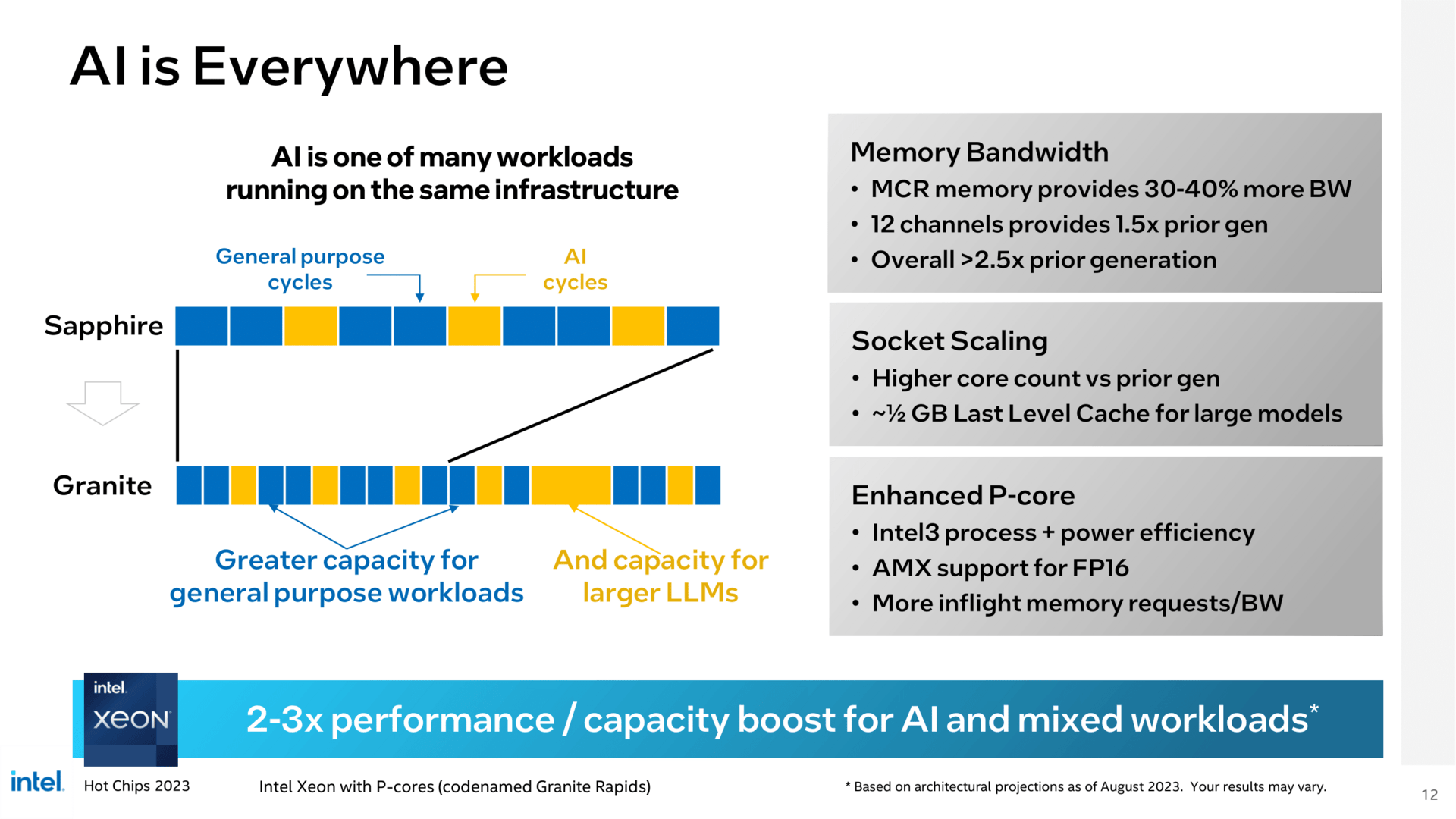

Vor allem das Speicherinterface hat sich Intel vorgenommen, hier unterstützen Granite Rapids und die Plattform nicht nur klassische DIMMs, sondern auch MCR (Multiplexer Combined Ranks). MCR bietet bereits bis zu 40 Prozent mehr Bandbreite, die nun 12 statt 8 Speicherkanäle sorgen für einen insgesamt gesehen deutlichen Schub.

Sierra Forest als neue E-Core-Lösung

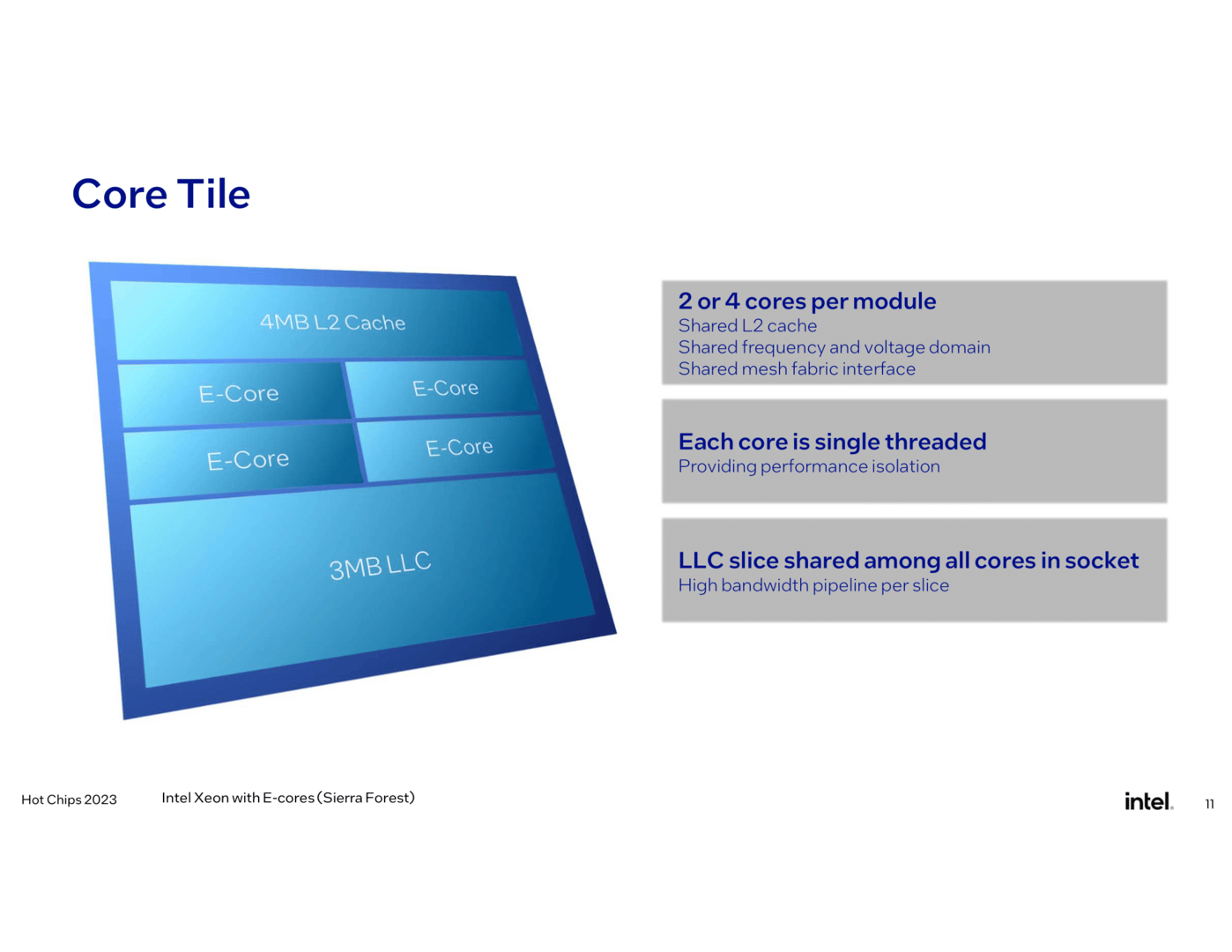

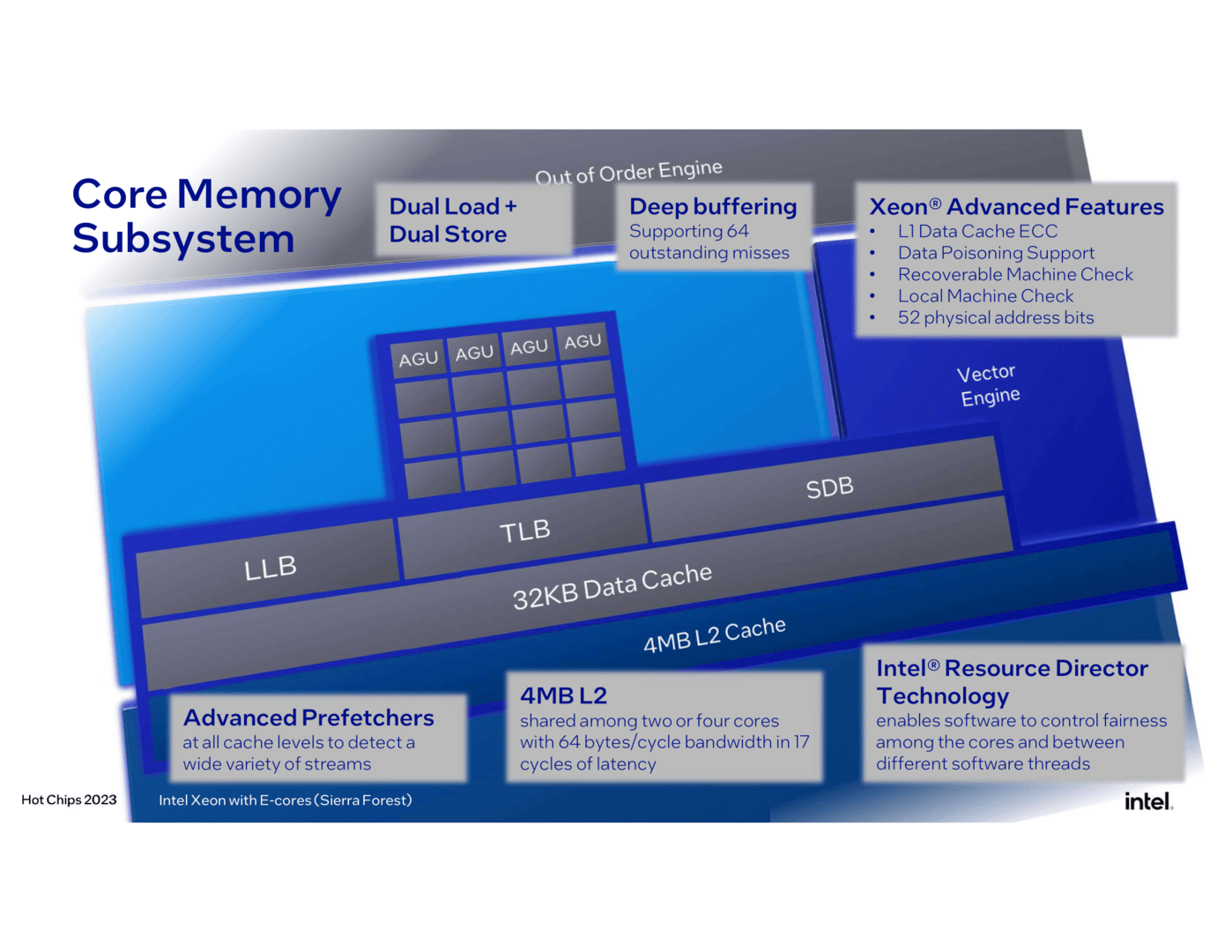

Die E-Cores, Codename Crestmont oder für dieses Segment angepasst auch Sierra Glen, werden im Produkt Sierra Forest gebündelt. Hier hatte Intel bereits einige Parameter bekannt gegeben. Die Cluster-Bildung, wie sie bereits in den letzten Consumer-Produkten genutzt wird, behält Intel hier im Prinzip bei, sodass auf zwei oder vier Kerne beispielsweise weiterhin ein 4 MB großer L2-Cache verteilt. Auch ein L3-Cache ist in einer Größe von 3 MByte nun dabei, pro Cluster je ein Slice, 144 Kerne haben 36 dieser Cluster.

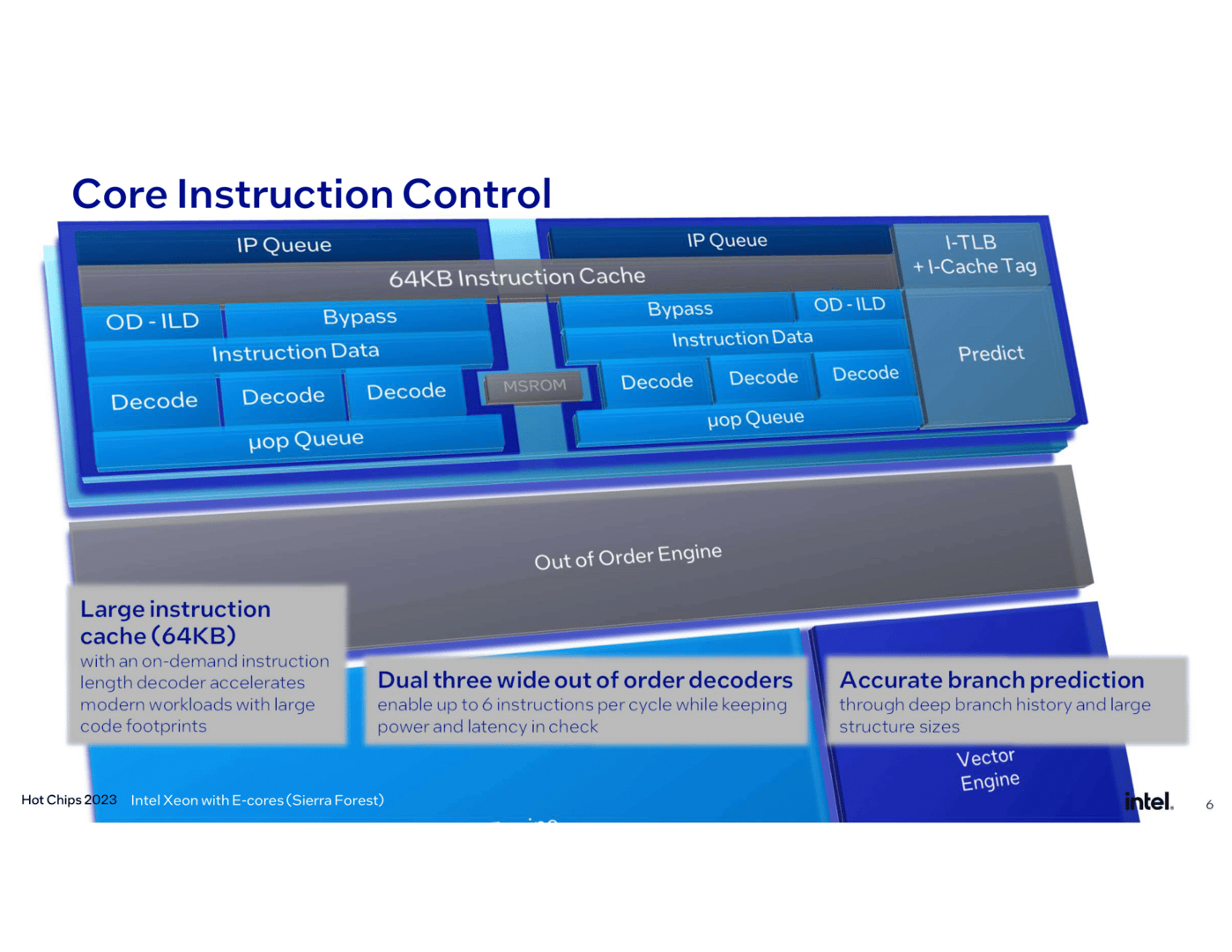

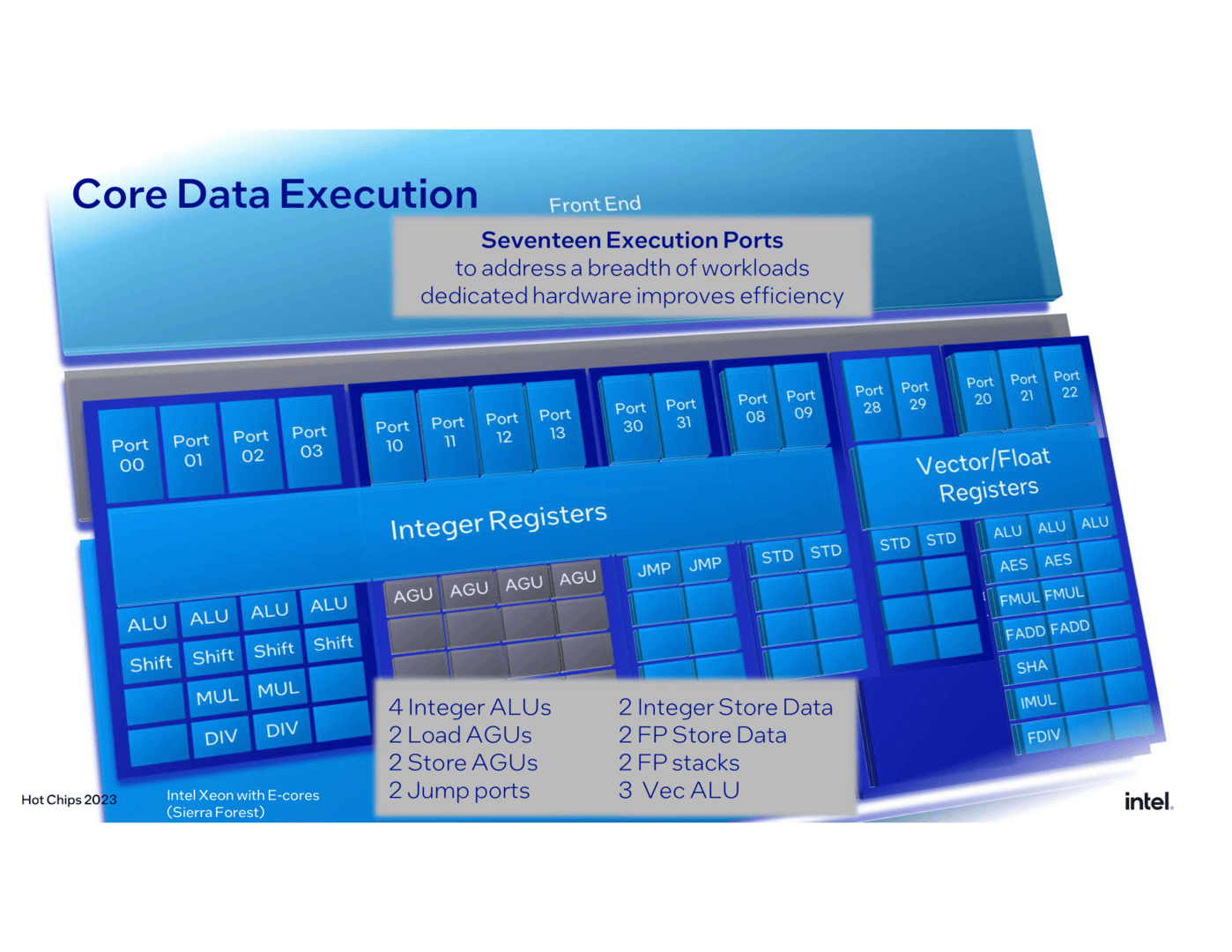

Ein Großteil der zuletzt bereits mit der E-Core-Architektur Grace Mont (Gracemont) eingeführten Design-Richtlinien wurden dabei übernommen und mitunter leicht angepasst und ausgebaut. Denn die Ziele haben sich nicht wirklich verändert, skalierbar und möglichst effizient soll es sein. Der beim letzten Mal eingeführte und auf 64 KByte aufgewertete L1-Instruction-Cache wird dabei ebenso mitgenommen wie der bereits bei Tremont eingebaute Out-of-Order-Decoder im 2 × 3-Design und die kuriose Anzahl der Execution Ports: es sind noch immer 17 Einheiten.

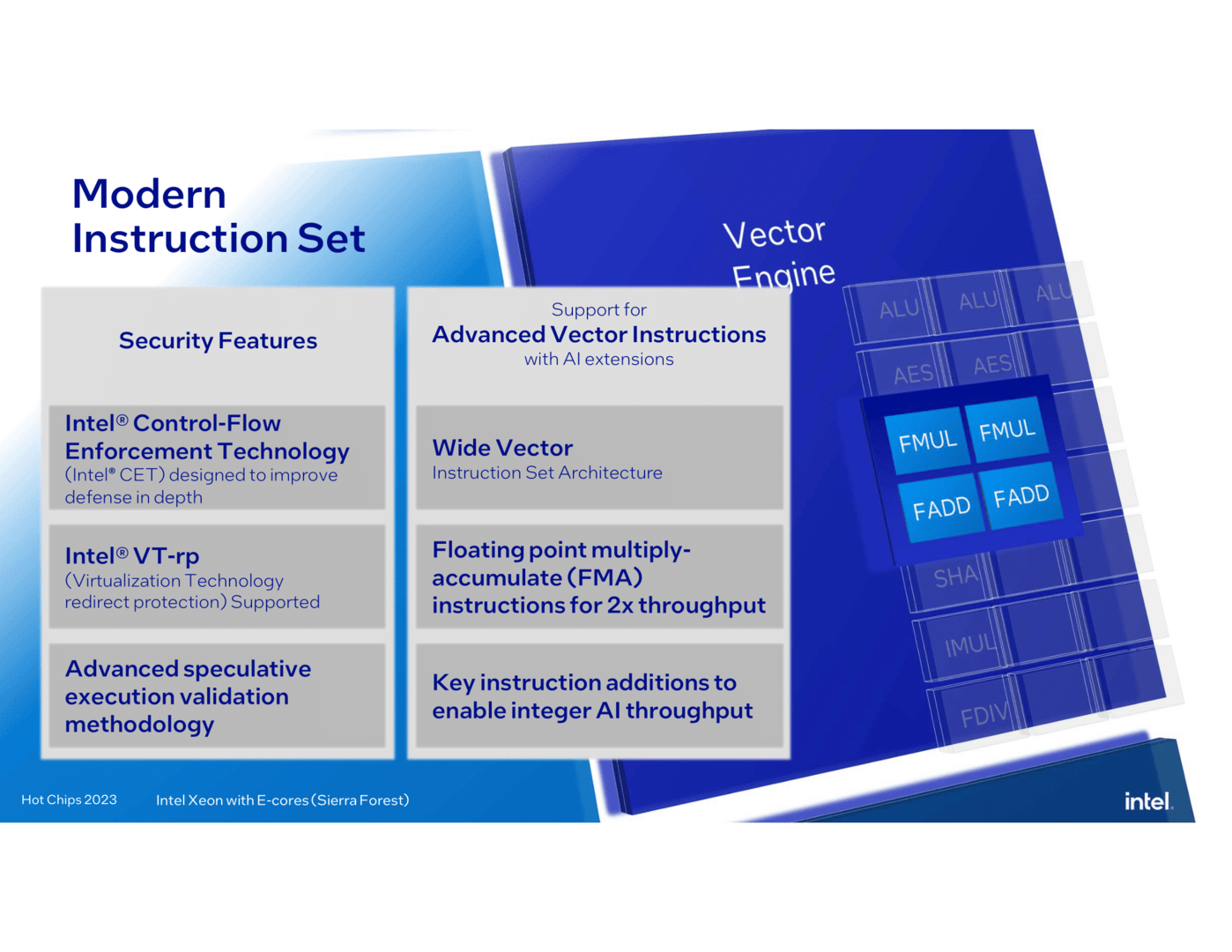

Features wie TSX oder mehr als AVX2 gibt es nicht, auch das neue und mit Granite Rapids verbesserte AMX ist lediglich für die P-Cores vorgesehen. In der Präsentation spricht Intel von einem effizienten Arbeiten, die TDP soll pro CPU bei maximal 205 Watt liegen. Im Dual-Sockel-System sind so demnach 288 Kerne bei 410 Watt möglich. Was die CPU kann, bleibt aber noch im Dunkeln verborgen, denn IPC-Hochrechnungen für die Kerne bringt Intel öffentlich nicht mit.

Eine Plattform mit gleichen I/O-Tiles sie alle zu verknüpfen

Das Interessante ist letztlich die Zusammensetzung auf dem Package. Zwei I/O-Tiles aus Intel-7-Fertigung verbinden je nach Modell mal ein, zwei oder auch drei CPU-Tiles mit ihren jeweiligen Speichercontrollern. Die Basis-Variante ist ein größerer Chip mit Acht-Kanal-Speicherinterface, ab der zweiten Variante wird auf eine Lösung mit CPU-Kernen zuzüglich vier Speichercontrollern gesetzt, die sich jedoch durch die Nutzung von drei dieser Tiles ebenso verdreifacht – 12 Speicherkanäle werden als Maximum geboten.

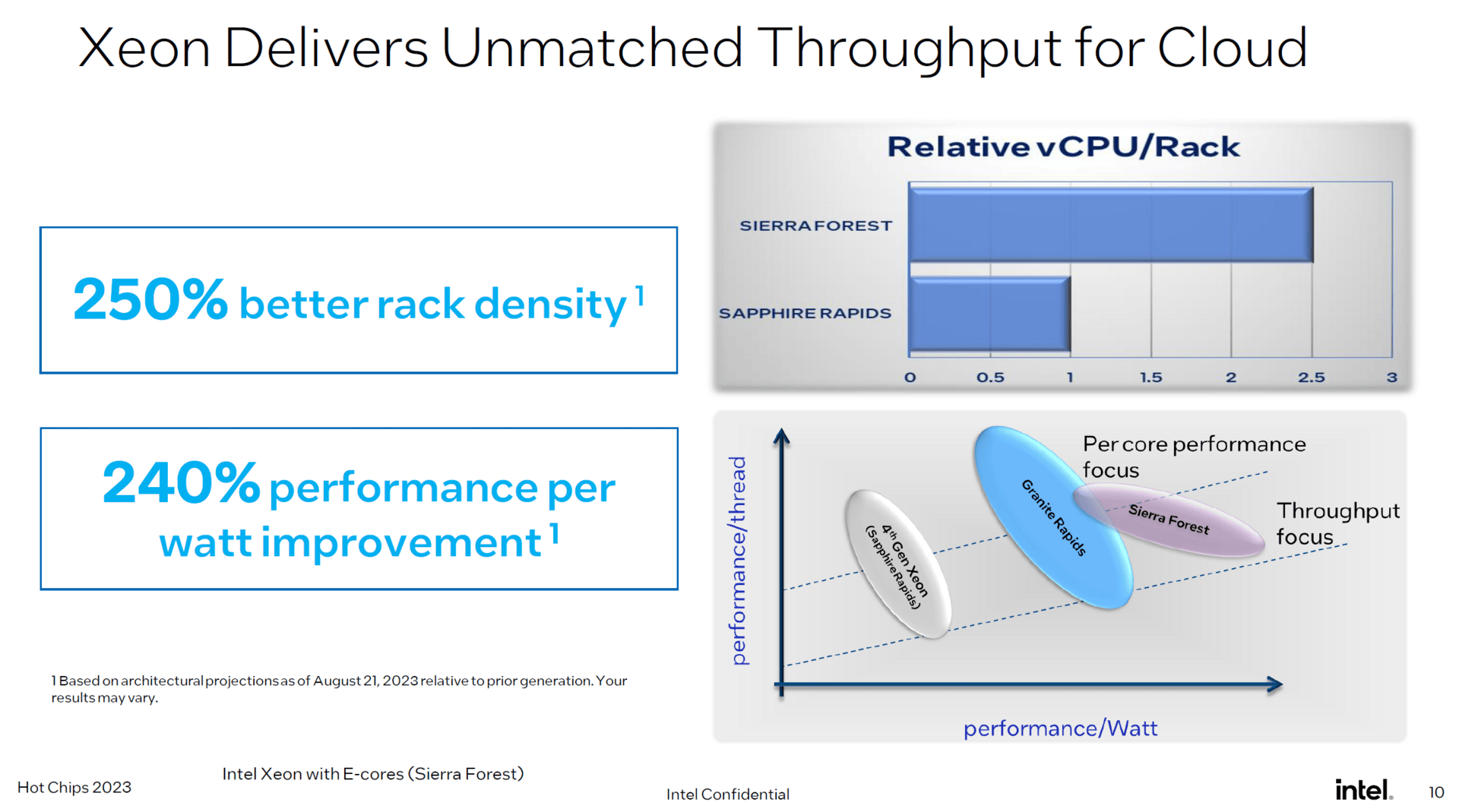

Sierra Forest soll dabei genau so behandelt werden wie Granite Rapids. Hier ließ Intel nun erstmals erkennen, dass dann mehr Kerne als die bisher offenbarten 144 zur Verfügung stehen können, nannte vorab jedoch keine exakte Zahl. Eine Folie, die um den Faktor 2,5 mehr vCPUs gegenüber Sapphire Rapids nennt, lässt nur bedingt Rückschlüsse zu, da vCPUs auch mit SMT-Threads arbeiten können, die Sierra Forest wiederum nicht hat. Der Faktor 2,5 von den nativen Kernen abgeleitet stimmt wiederum, denn die aktuellen Xeons bieten 56 bis 60 Kerne.

Das gilt auch für Granite Rapids. Hier erklärte Intel ebenfalls diplomatisch, dass es mehr Kerne seien als in vorangegangenen P-Core-Xeons. Gerüchte besagten einmal 40 Kerne in einer Mesh-Anordnung pro Compute-Tile, also maximal 120 mit drei Kacheln. Letzteres könnte durchaus passen, denn 4 MByte L3-Cache pro Kern würden bei 120 Kernen 480 MByte und damit das „rund halbe Gigabyte“, welches Intel benennt, bedeuten.

Die Aufteilung im Markt wird sich aber auch an der Zweiteilung zeigen: Birch Stream-SP und Birch Stream-AP. Nur in letzterem gibt es das Maximum aller zuvor genannten Eckdaten, die SP-Lösung ist eine Nummer kleiner aufgestellt, maximal acht Speicherkanäle und maximal zwei CPU-Tiles verbleiben – hier werden primär die E-Core-Varianten zu finden sein.

ComputerBase hat Informationen zu diesem Artikel von Intel unter NDA erhalten. Die einzige Vorgabe war der frühestmögliche Veröffentlichungszeitpunkt.

- Hot Chips 2023: AMD verrät wenig mehr über „Siena“ und verwirrt

- Intel-Xeon-Architektur: Granite Rapids und Sierra Forest mit 144 Kernen detailliert