Intel Emerald Rapids: Flotter Refresh überall sichtbar, aber doch noch nicht da

Der Show-Floor und die Sessions sind voll mit Informationen zu Intels nächster Xeon-Generation Emerald Rapids. Ein Überblick zum Neuen, der auf den ersten Blick unter der Haube doch aussieht wie ein Schritt zurück. Denn statt alles auf kleine Chiplets zu setzen, wird es wieder größer.

Emerald Rapids ist so etwas wie eine kleine Anomalie. Sapphire Rapids setzte schließlich in der großen Variante auf vier kleine CPU-Dies, die auf einem Package zusammengesetzt wurden – der Vorgeschmack auf das, was Intel mit Chiplets in Zukunft plant. Aber nun kommt Emerald Rapids: Aus vier Chips werden plötzlich wieder nur zwei, alle die zuvor genannten Vorteile von kleineren Chips für gute Yields und geringe Kosten sind passé. Nicht ganz, erklärt Intel.

Intel Sapphire Rapids hatte seine Probleme, viele davon, wie auch ComputerBase mehrfach beleuchtete. Mindestens ein Dutzend Steppings markierten einen Rekord, die Verspätung am Ende ebenfalls. Hinter den Kulissen wurde deshalb beim Refresh für die gleiche Plattform entschieden, ein wenig Komplexität aus der Geschichte zu nehmen, aber dennoch zu gewinnen. Heraus kommt Emerald Rapids mit nur noch zwei CPU-Dies.

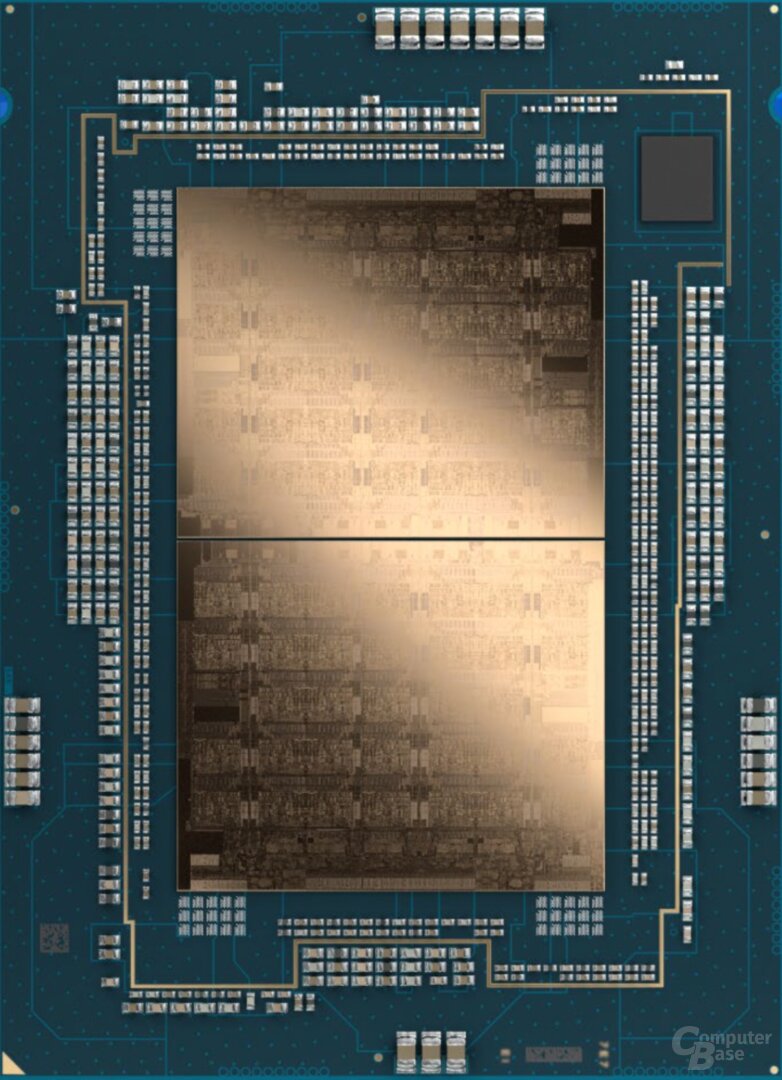

Emerald Rapids nutzt zwei große Dies

Auf der Intel Innovation 2023 erklärte der Hersteller, dass ein CPU-Die von Emerald Rapids mit seiner Größe in der Liga spielt, in der Sapphire Rapids-MCC unterwegs ist. Auch das ist eine monolithische Lösung, diese bietet auf dem Die 34 Kerne plus Cache, Speicherinterface und alles, was dazu gehört. Bei Emerald Rapids werden nun quasi zwei dieser Lösungen kombiniert, heraus kommt die neue XCC-Version – bei augenscheinlich 33 Kernen pro Die, wie das Bild darlegt.

Die Frage nach dem Warum erklärte Intel mit einer deutlich angestiegenen Yield-Kurve bei Intel 7 für große Chips aber auch dem Stromverbrauch der einzelnen Bauteile bei Sapphire Rapids. Zwischen den Kacheln von Sapphire Rapids Daten immer über EMIB zu transportieren, kostet viel Energie. Nur zwei große Dies über angeblich nur noch drei EMIB-Chips statt zuvor zehn zu verbinden, schlägt deshalb mehrere Fliegen mit einer Klappe: Mehr Kerne und Cache direkt vor Ort sparen Energie ein, weniger EMIB-Chips sparen ebenfalls Energie, das Gesamtkonstrukt profitiert zudem von verbesserten Latenzen.

Wo Intel die bis zu 320 MByte L3-Cache unterbringt, wird aus den Details noch nicht ganz ersichtlich. Ein MCC-Die von Sapphire Rapids hatte nur 60 MByte, ein verdoppelter also theoretisch 120 MByte, reguläre XCC-Lösungen hatten 105 MByte. Das ist ein Detail, welches Intel sich für den bevorstehenden Serverworkshop vor dem Start aufgehoben hat.

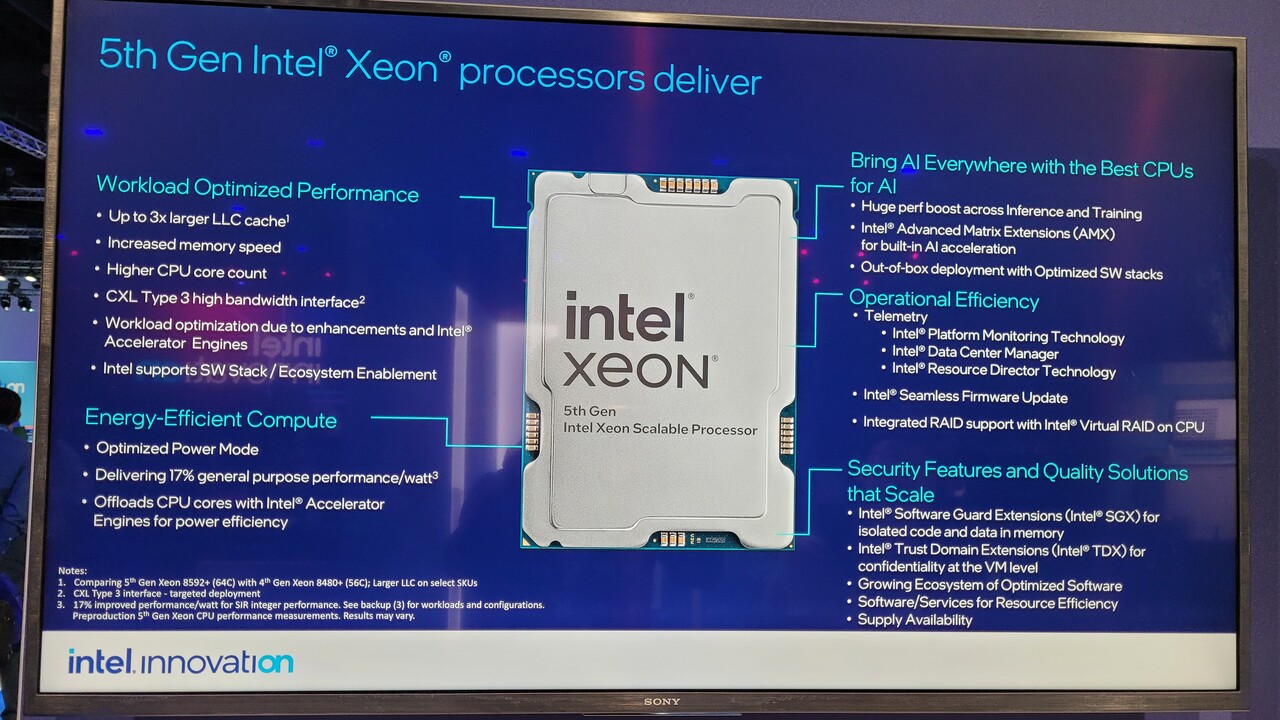

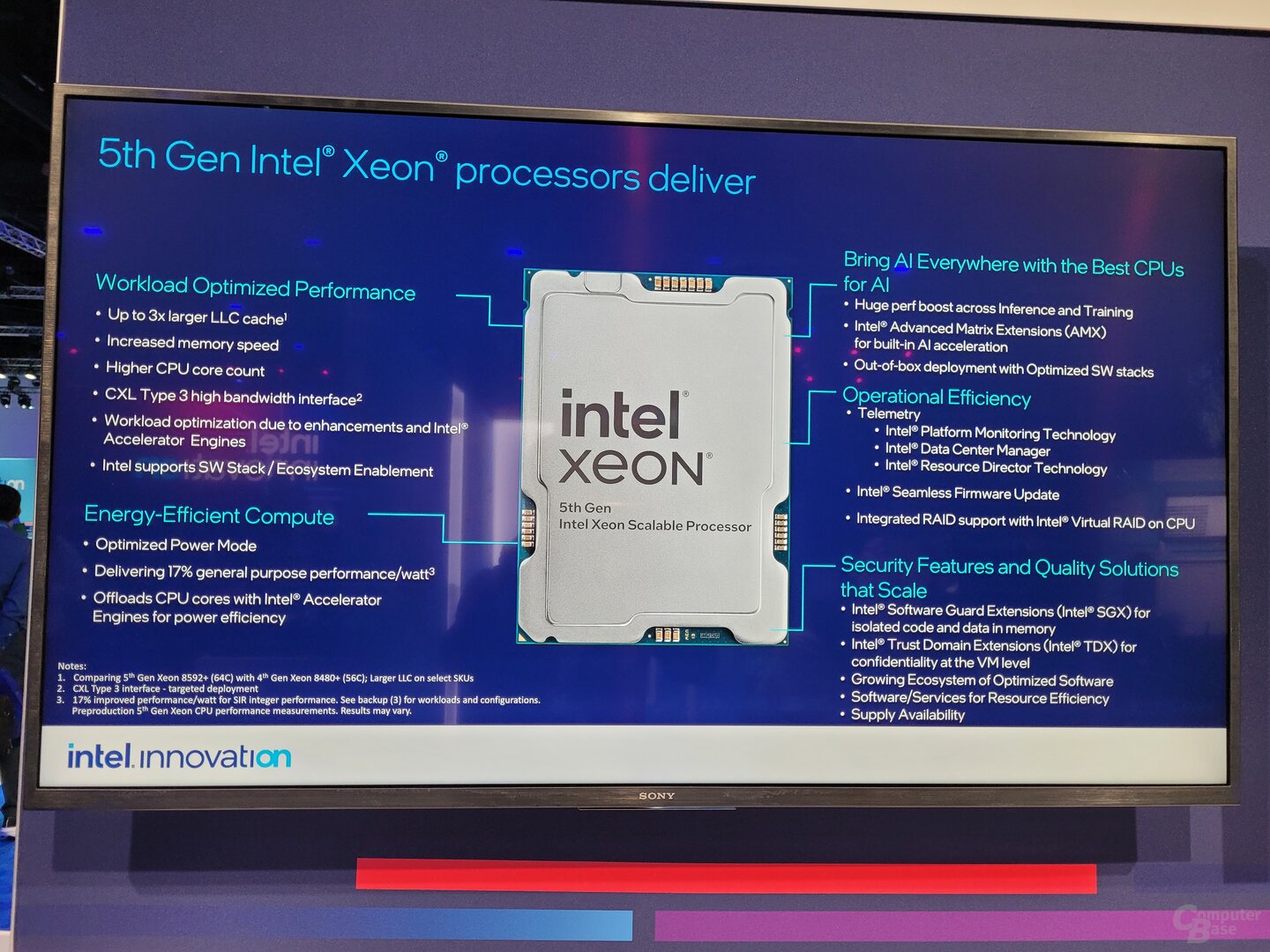

Deutlicher Leistungsgewinn

In seiner Keynote erklärte Pat Gelsinger bereits, dass durch die Optimierungen am Design Emerald Rapids in gewissen Szenarien um bis zu 40 Prozent schneller sein kann als Sapphire Rapids – und das ist noch nicht das Maximum, hieß es auf dem Show-Floor im Nachgang. Der üppige L3-Cache hilft hierbei natürlich, aber auch so scheint die Optimierung dann doch ein deutlich runderes Produkt auszumachen.

Elf Monate nach dem Start von Sapphire Rapids wird Intel Emerald Rapids in den Markt schicken. Vor Ort versucht man, Sapphire Rapids dennoch als Erfolg zu verkaufen, die angepeilte Marke von über 2 Millionen verkauften Einheiten bis zum Jahresende wird früher erreicht als bisher anvisiert, heißt es.

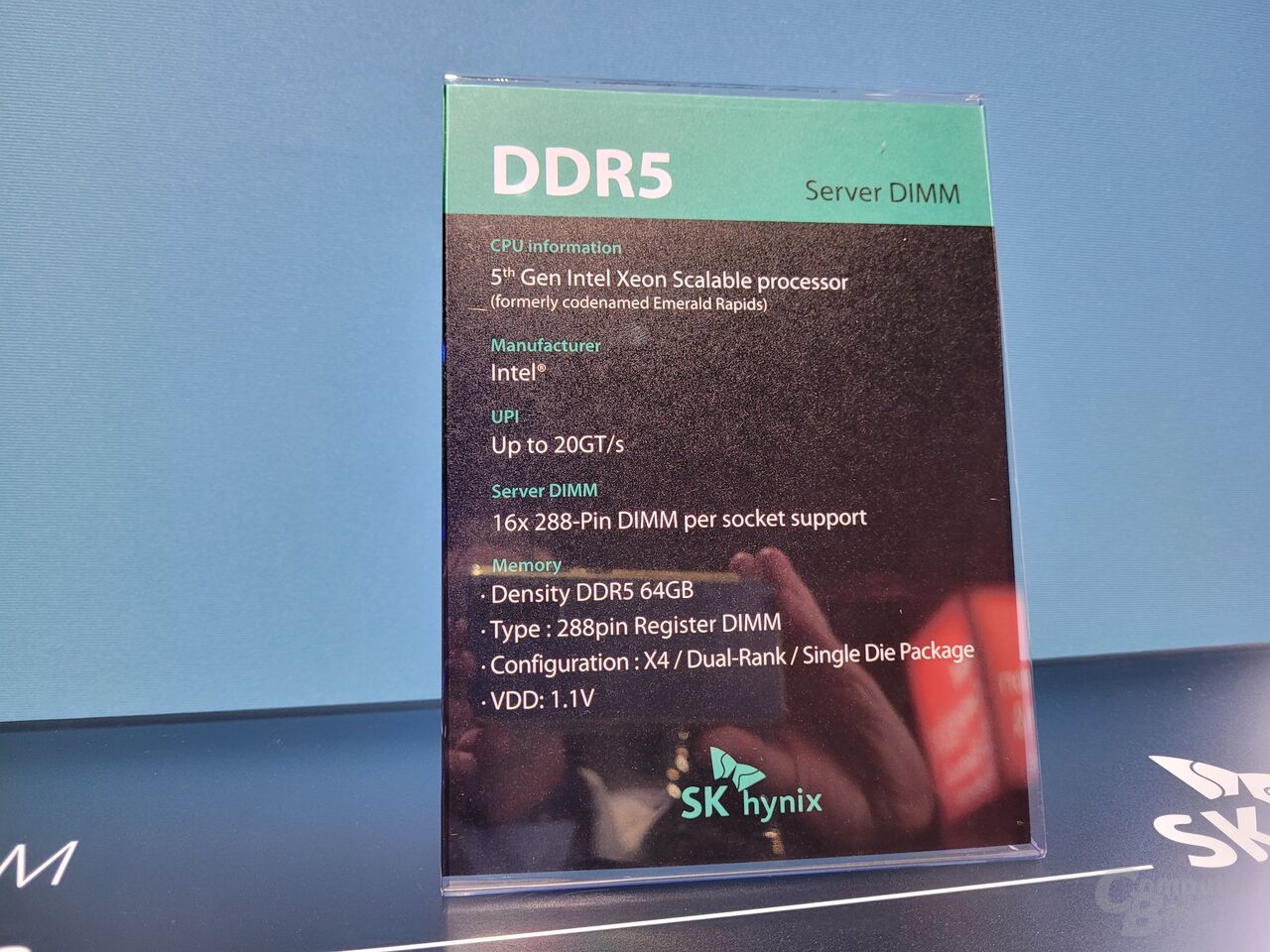

Das Ökosystem ist derweil schon längst bereit für den Nachfolger. Speicherhersteller zeigen ihre Systeme, bestückt mit flottem DDR5-RAM. Und der wird in allen Größen erscheinen, bis zu 256 GByte DDR5-5600 pro Modul. In ein Dual-Sockel-System passen 32 Bänke und Module – 8 TByte RAM sind kein Probleme, außer vielleicht des Geldes.

- Für Notebooks & AIOs: Intel Meteor Lake kommt nicht für „klassische Desktop-PCs“

- Moore's Law lebt: Das „Grundgesetz“ wird mit neuen Technologien am Leben gehalten

- 576 E-Cores im Server: „Pro Kern will die Lizenz eher niemand bezahlen“

- +27 weitere News