High Bandwidth Memory (HBM): Samsung bemustert HBM3E in Kürze, bis 2025 kommt HBM4

High Bandwidth Memory (HBM) erlebt derzeit einen Höhenflug, denn in der beginnenden KI-Ära wächst der Bedarf an Rechenbeschleunigern mit durchsatzstarkem Speicher. Daher wundert es nicht, dass Samsung jetzt auf die Neuentwicklungen hinweist. In Kürze soll HBM3E bemustert werden. Bis 2025 soll dann bereits HBM4 bereitstehen.

Samsung über HBM3E und HBM4

Wie SangJoon Hwang, der Leiter des DRAM-Technik-Teams bei Samsung, in einem Blogpost erklärt, ist HBM „ein wesentlicher Bestandteil der KI-Ära“. HBM2E und HBM3 werden bei Samsung bereits in Serie gefertigt. In Kürze soll aber HBM3E mit 9,8 Gbit/s pro Pin als Muster zur Verfügung stehen, was noch etwas schneller als HBM3E bei SK Hynix oder der HBM3E Gen2 vom Späteinsteiger Micron ist.

| max. Durchsatz pro Pin | max. Durchsatz pro Stack | max. Kapazität pro Stack | |

|---|---|---|---|

| HBM1 | 1,0 Gb/s | 128 GB/s | 1 GB |

| HBM2 | 2,0 Gb/s | 256 GB/s | 8 GB |

| HBM2E | 3,6 Gb/s | 461 GB/s | 16 GB |

| HBM3 | 6,4 Gb/s | 819 GB/s | 24 GB |

| HBM3E (SK Hynix) | 9,0 Gb/s | 1.152 GB/s | 24 GB |

| HBM3 Gen2 (Micron) | 9,2 Gb/s | 1.178 GB/s | 36 GB |

| HBM3E (Samsung) | 9,8 Gb/s | 1.254 GB/s | ? |

| HBM4 | ? | ? | ? |

Die Einführung von HBM4 wird laut Hwang bis 2025 erwartet. Dann sollen Techniken wie „non-conductive film“ (NCF) und „hybrid copper bonding“ (HCB) zum Einsatz kommen. Zu Durchsatz oder Speicherkapazitäten macht er aber noch keine Angaben.

Later on, Samsung mass-produced HBM2E and HBM3, and has developed 9.8 gigabits-per-second (Gbps) HBM3E, which we’ll soon start sampling to customers in our drive to enrich the HPC/AI ecosystem.

Looking ahead, HBM4 is expected to be introduced by 2025 with technologies optimized for high thermal properties in development, such as non-conductive film (NCF)1 assembly and hybrid copper bonding (HCB)2.

1 NCF (non-conductive film): A polymer layer that protects solder joints from insulation and mechanical shock between stacked chips.

2 HCB (hybrid copper bonding): A next-generation bonding technology that uses copper (conductor) and oxide film (insulator) instead of conventional solder.

Doppelte Bus-Breite bei HBM4?

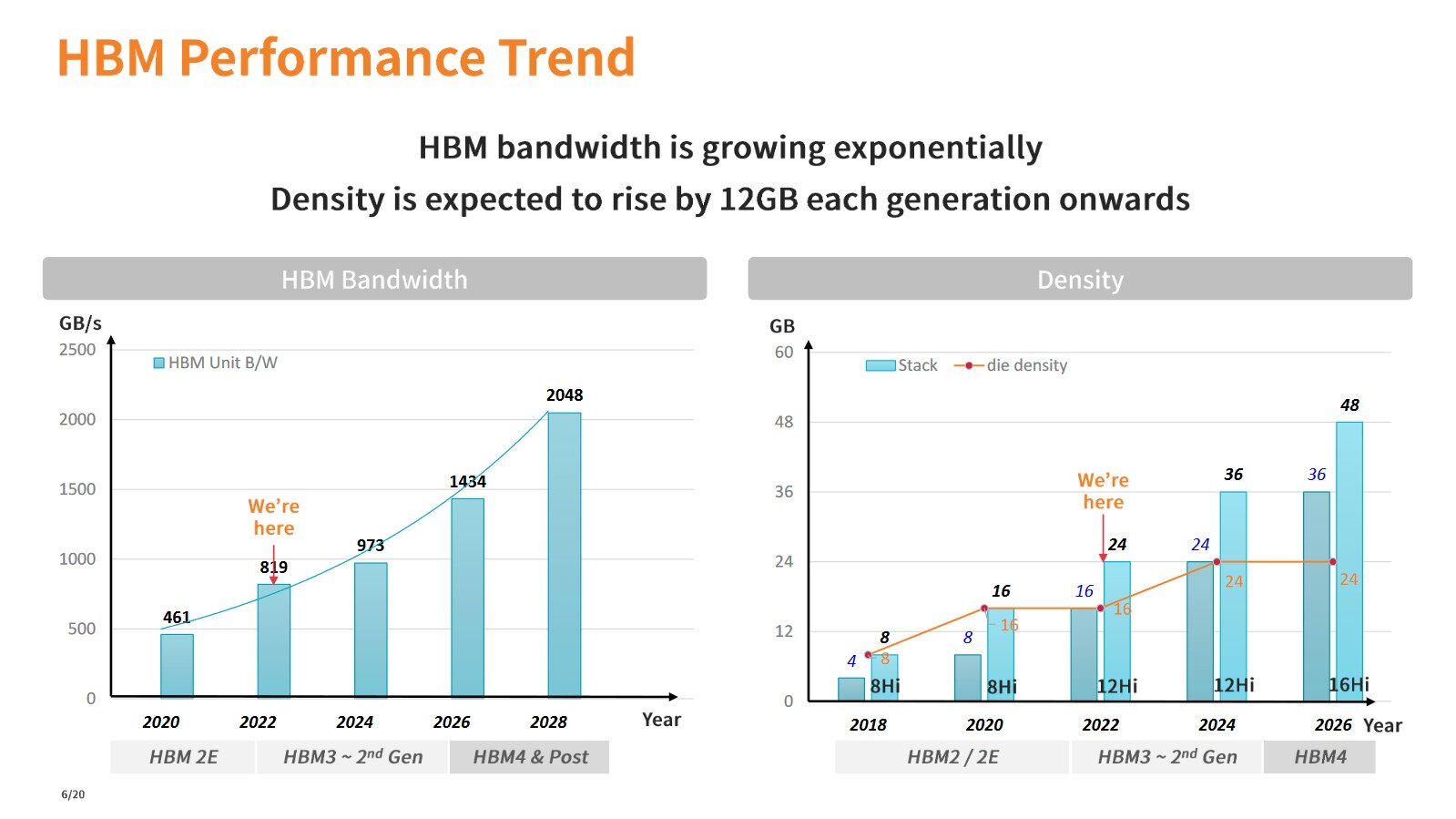

Alle bisherigen HBM-Standards haben eines gemein: Ein 1.024 Bit breites Speicherinterface, das trotz vergleichsweise geringer Taktfrequenzen einen sehr hohen Durchsatz ermöglicht. Mit HBM4 könnte dieser Speicherbus deutlich verbreitert werden, genau genommen sogar verdoppelt. Wie AnandTech berichtet, habe ein leitender Angestellter des Auftragsfertigers TSMC nämlich genau das für HBM4 in Aussicht gestellt. „Statt die Geschwindigkeit zu verdoppeln, haben sie die Pins verdoppelt“, wird dieser in einer Aussage zu HBM4 zitiert.

Das würde wiederum eine Verdoppelung auf 2.048 Bit bedeuten. Bei gleicher Speicherfrequenz würde damit der Durchsatz verdoppelt. Allerdings führt dies auch zu komplexeren Chips.

Die Pläne der Konkurrenz

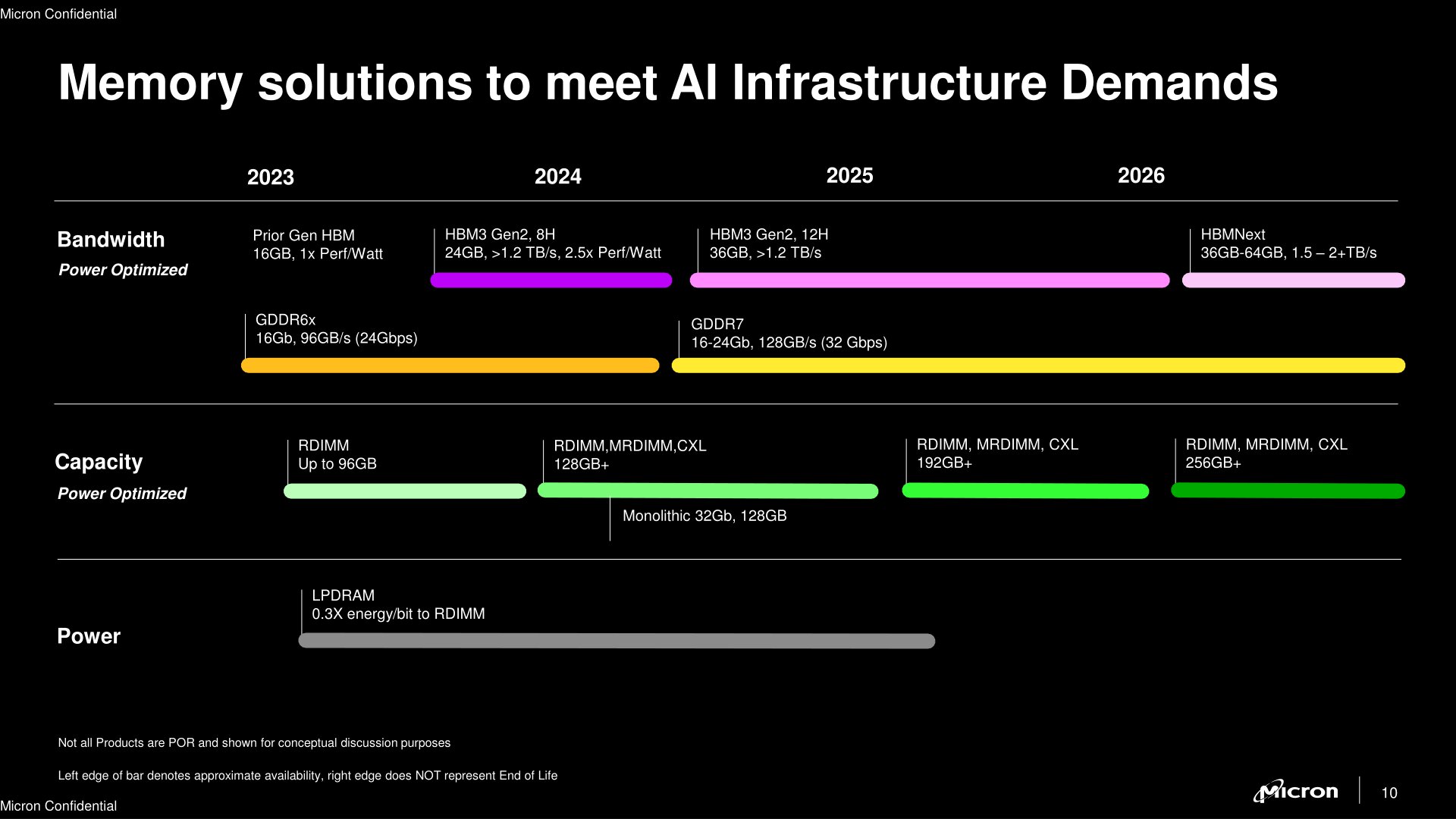

Micron hat in einer Roadmap von „HBMNext“ mit 1,5 TB/s bis über 2 TB/s pro Stack ab dem Jahr 2026 gesprochen.

Auch SK Hynix sah bisher eher das Jahr 2026 für die Einführung von HBM4 als wahrscheinlich an. Auf einer Roadmap aus dem Frühjahr 2022 hatte SK Hynix zunächst rund 1,4 TB/s und erst für Jahre später 2 TB/s in Aussicht gestellt. Da die Konkurrenz aber nun stärker beschleunigt, dürfte auch SK Hynix bestrebt sein, solche Geschwindigkeiten schneller zu erreichen.

Wie Business Korea berichtet, werden Prototypen von Samsungs HBM3E zu Testzwecken ausgeliefert. Die Chips tragen den Codenamen Shinebolt und sollen einen 50 Prozent höheren Durchsatz als HBM3 bieten. Das würde 9,6 Gbit/s statt 6,4 Gbit/s pro Pin oder 1,228 TB/s statt 0,819 TB/s pro Stack bedeuten. Die von Samsung angepeilten 9,8 Gbit/s würden also noch nicht ganz erreicht.

Der Prototyp soll acht Dies zu je 24 Gbit (3 GByte) stapeln, besitzt also eine Speicherkapazität von 24 GByte. Samsung werde aber bald auch eine Variante mit 36 GByte (12 Layer) fertigstellen.