28,5 Gbit/mm²: Samsungs 280-Layer-NAND schlägt bei Flächendichte alles

In rund drei Wochen steht die alljährliche International Solid-State Circuits Conference (ISSCC) an. Zahlreiche Unternehmen der Halbleiterbranche werden wieder daran teilnehmen und über aktuelle wie kommende Technikneuheiten berichten. Samsung will neuen NAND-Flash mit der bisher größten Datendichte vorstellen.

Für den 20. Februar um 17 Uhr (MEZ) ist die Session „A 280-Layer 1Tb 4b/cell 3D-NAND Flash Memory with a 28.5Gb/mm² Areal Density and a 3.2GB/s High-Speed IO Rate“ angesetzt, die von Vertretern vom führenden Speicherhersteller Samsung bestritten wird.

Die Überschrift sagt schon alles: Samsung hat also eine neue Generation QLC-NAND-Flash mit 4 Bit pro Zelle entwickelt, die eine extrem hohe Flächendichte von 28,5 Gigabit pro Quadratmillimeter aufweisen soll. Das würde den in diesem Punkt amtierenden Spitzenreiter YMTC mit 19,8 Gbit/mm² bei seinem 232-Layer-QLC-NAND mehr als deutlich vom Thron stoßen. Selbst den hochdichten TLC-NAND mit über 300 Layern und 20,0 Gbit/mm², den SK Hynix angekündigt hatte sowie den ersten PLC-NAND von Intel mit 5 Bit pro Zelle und 23,3 Gbit/mm² würde Samsungs neuer Speicher bei der Flächendichte weit übertrumpfen.

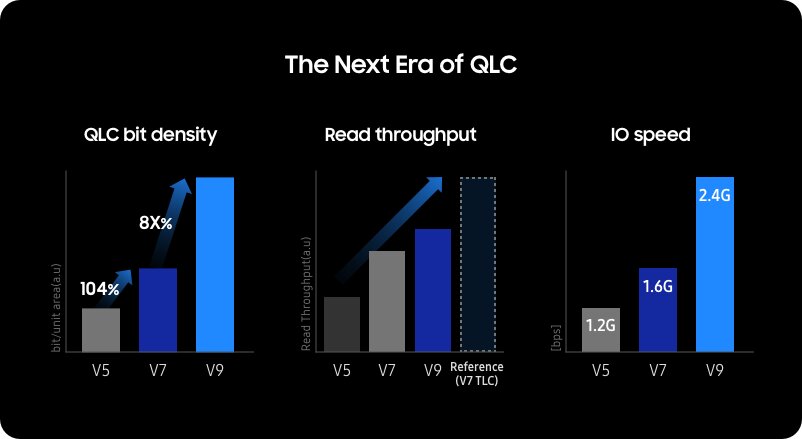

Der QLC-NAND von Samsung soll über 280 Zellschichten (Layer) verfügen, dürfte also bereits zur V9-Generation gehören, denn der V8-NAND liegt bei 238 Layern. Den V9 QLC NAND hatte Samsung zudem schon einmal mit einem anvisierten Produktionsstart im Jahr 2024 angekündigt. Seinerzeit war von einer Steigerung der Flächendichte um über 80 Prozent sowie einer I/O-Schnittstelle mit 2,4 Gbit/s die Rede. Letzteres wird mit den jetzt genannten 3,2 Gbit/s aber übertroffen. Samsung will nicht kleckern, sondern klotzen. Genau dies muss der Hersteller aber auch, denn allmählich gerät er in vielen Punkten ins Hintertreffen gegen Konkurrenten aus den USA (Micron) und China (YMTC).

In den letzten Jahren hatte Samsung immer wieder betont, dass QLC-NAND hier ist um zu bleiben. Bisher ist vor allem die niedrige Schreibgeschwindigkeit eine Achillesferse, doch soll es auch dort Fortschritte geben. Die hohe Flächendichte sorgt vor allem für eines: Geringere Herstellungskosten, denn je mehr Bit auf einen Wafer passen, umso besser.

Micron spricht über TLC-Flash

Auch Micron wird auf der ISSCC 2024 vertreten sein und am gleichen Tag die Session „A 1Tb Density 3b/Cell 3D-NAND Flash on a 2YY Tier Technology with a 300MB/s Write Throughput“ abhalten. Hier bleibt abzuwarten, ob es sich um neuen Speicher oder aber die aktuelle 232-Layer-Generation handelt, welche eben auch bereits 1 Terabit Speicherkapazität als TLC-Version bietet und aktuell die schnellsten PCIe-5.0-SSDs für Verbraucher bedient.