Clearwater Forest: Intel stapelt 17 Chips, auch auf einem Intel-3-T-Base-Tile

Erst nur durch die Blume, nun aber auch in einem umfangreichen Dokument, hat Intel viele Details zur kommenden E-Core-Xeon-CPU verraten. Das ist spannender, als es zunächst klingt, denn erstmals setzt Intel Errungenschaften, die es bisher primär auf dem Papier gab, in die Tat um. Dazu zählen auch viele neue Fertigungsschritte.

Alles neu auf bekannter Plattform

In dem ziemlich technischen Dokument (PDF) bringt es der letzte Satz auf den Punkt, welchen Meilenstein die Plattform für Intel bedeuten soll und könnte:

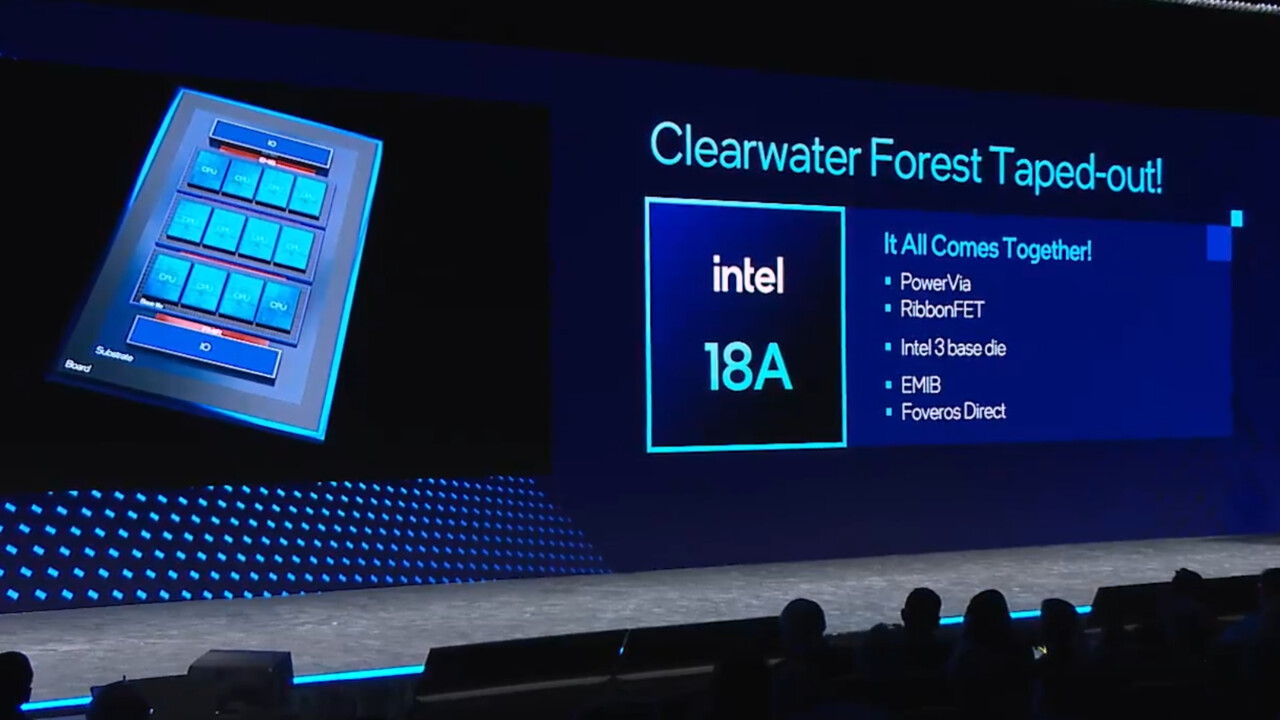

Intel 18A, Foveros Direct 3D and EMIB 3.5D are ready for design by Intel Foundry customers and will debut in the market in 2025 in a future Intel Xeon processor, codenamed Clearwater Forest.

Intel

Intel Clearwater Forest ist der Nachfolger von Intel Sierra Forest. Letzterer debütiert in diesem Jahr mit als erster reiner E-Cores-Xeon, dafür aber bis zu 288 Stück auf einem Package. Mit Clearwater Forest wird die Idee weitergetragen, aber in nahezu jedem Punkt überarbeitet und verbessert. Das schließt explizit die gesamte Bauweise und zugrundeliegende Technologien mit ein. Einige davon hat Intel im Rahmen des Foundry-Events erst in dieser Woche offiziell bestätigt.

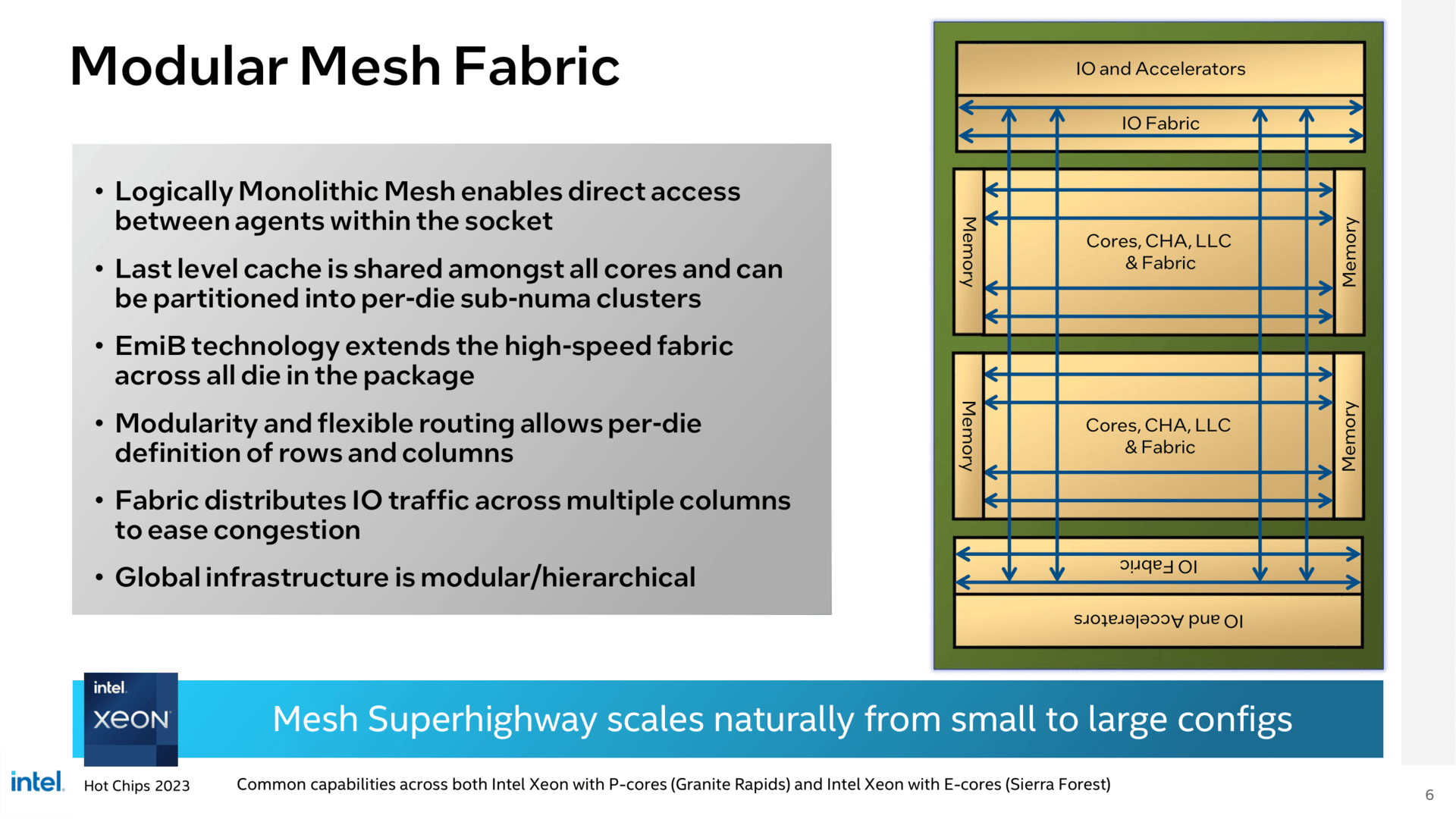

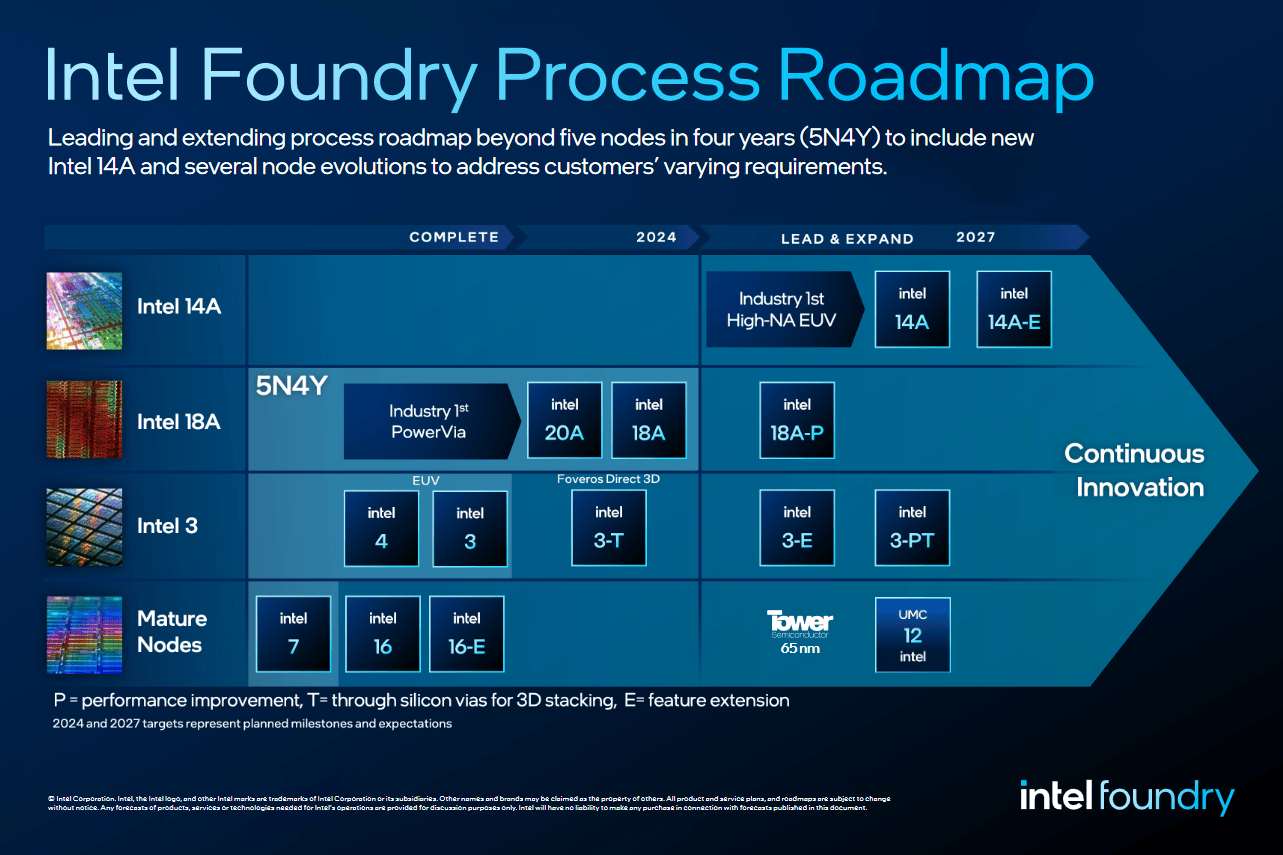

Im Dokument bestätigt Intel, dass die zweite Generation der Fertigung mit Gate all around (GAA) inklusive Backside Power Delivery (BSPD) alias Intel 18A für Clearwater Forest genutzt wird, explizit spricht der Hersteller dabei von den CPU-Kacheln. Die Base-Tiles, auf denen die CPU-Chips dann sitzen, werden in Intel 3-T gefertigt. Diese neue Technologiestufe hatte Intel in dieser Woche enthüllt, es ist ein Intel-3-Prozess, der jedoch explizit auf die Nutzung von Through Silicon Vias (TSV) abzielt. Diese kleinen Durchkontaktierungen sind für das Stacking übereinander nötig – Foveros Direct 3D, wie es bei Intel heißt, kommt dann ins Spiel.

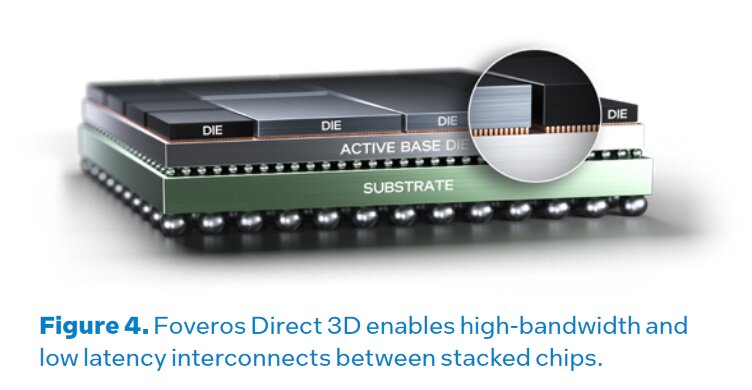

Was Intel bei Clearwater Forest nutzt, ist EMIB 3.5D. Dahinter steckt die Mischung aus der Embedded Multi-die Integrated Bridge (EMIB), als die Verbindung von zwei Chips in der Ebene, mit Foveros, dem Stapeln in der Höhe. Foveros Direct 3D nutzt Hybrid Bonding, welches von TSMC bereits bekannt ist. Die Chips werden nun auch bei Intel via „thermocompression bonding of copper vias“ direkt aufeinander gesetzt, wahlweise „Face-to-Face“ oder auch „Face-to-Back“.

Die auf dem Base-Tiles mit Foverors gestapelten Chips werden mittels EMIB dann mit dem nächsten gestapelten Chip verbunden. Da kann ein weiterer Compute-Tile sein, oder auch etwas anderes wie ein I/O-Die.

Das könnte Clearwater Forest sein

Aktuell wird davon ausgegangen, dass Clearwater Forest in der Spitze mit mindestens 288 Kernen angeboten werden dürfte. Legt man das Schaubild zugrunde, ergibt sich daraus für jede der 12 CPU-Tiles eine Anzahl von 24 Kernen. Jeweils vier dieser CPU-Tiles sitzen auf einem aktiven Base-Tile, dieses wiederum ist dann mit dem nächsten Base-Tile verbunden. Interessant sind in dem Zusammenhang die Aussagen von Intel zum besagten aktiven Base-Die, der beispielsweise den Cache enthalten kann.

This unit of CPU chiplets sitting atop a large “local” cache becomes a complete compute module, which can then be replicated to scale up compute capability and create a SKU stack based on core count and cache requirements.

Intel

Die Anzahl der Kerne bleibt deshalb Spekulation, weil Intel explizit auch die Skalierung beschreibt, die je nach Modell, Markt und Anforderungen angepasst werden kann. Bei Sierra Forest kam Intel auch erst „in der letzten Minute“ mit einem 288-Kerner um die Ecke, zuvor war von lediglich 144 Kernen ausgegangen worden.

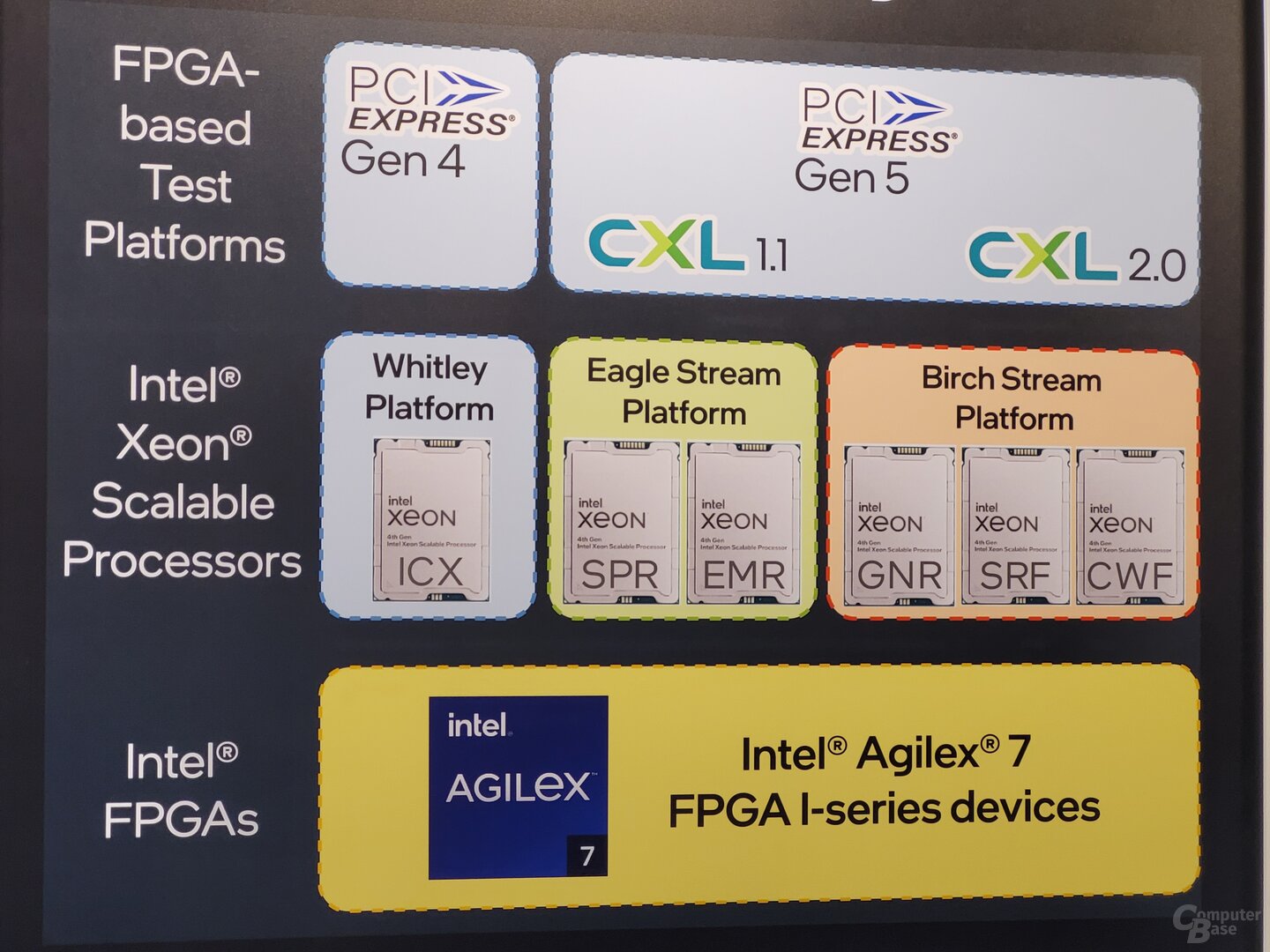

Nördlich und südlich der Compute-Cluster dürften erneut die I/O-Tiles zu finden sein. Dass die I/O-Dies hier in die Richtung von Sierra Forest und Granite Rapids gehen dürften, ist anzunehmen, denn Clearwater Forest soll noch einmal in exakt dem gleichen Birch-Stream-AP-Sockel seinen Platz finden wie die beiden anderen Xeon-Prozessoren.

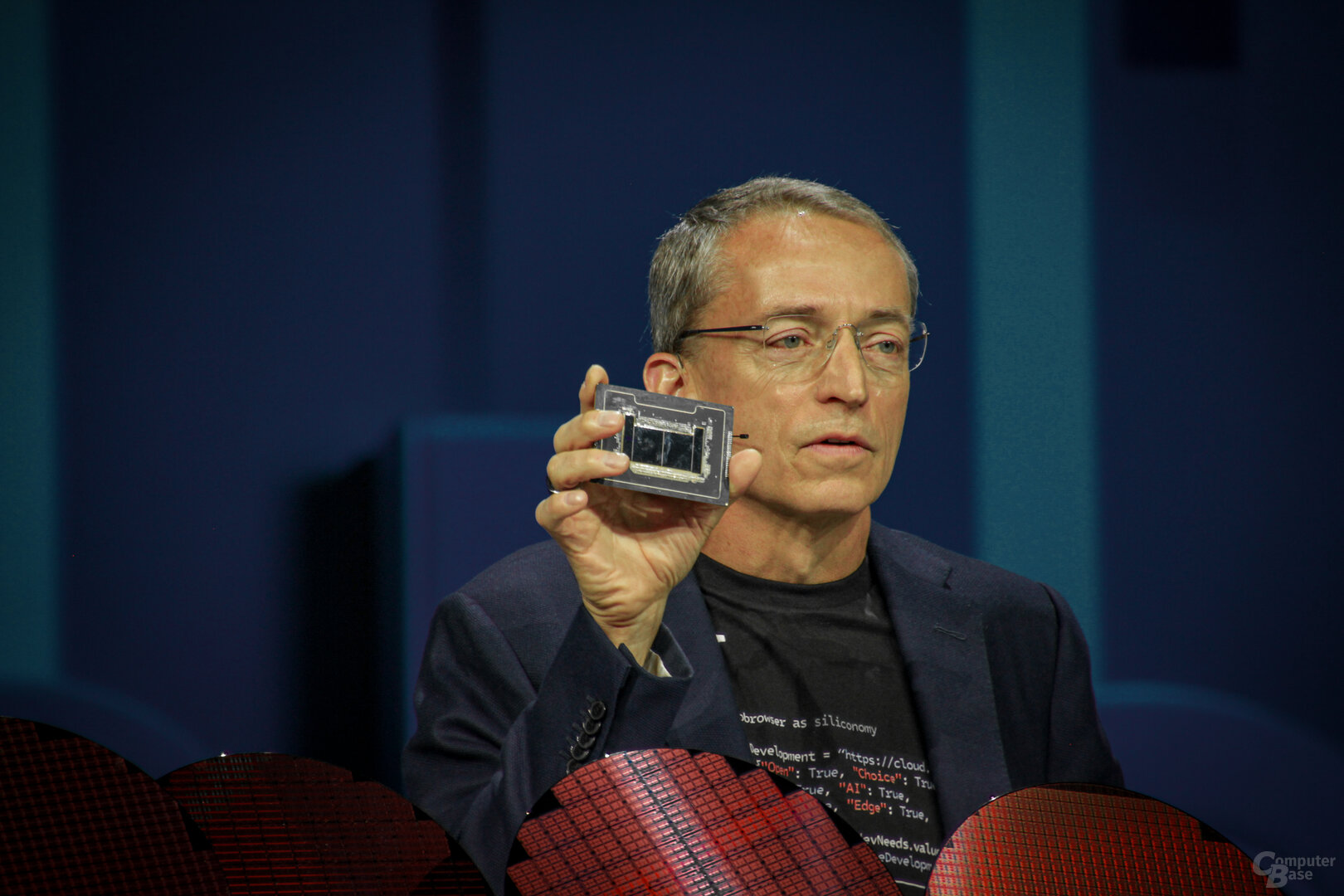

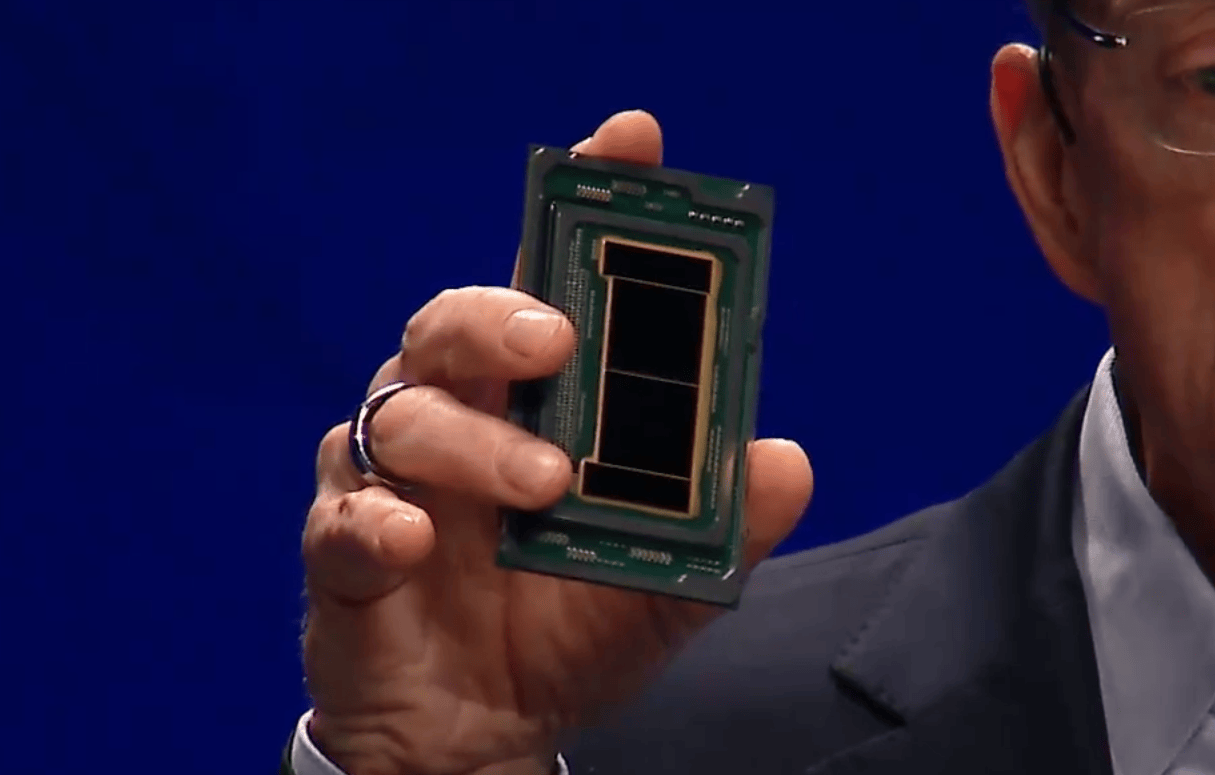

Der Testchip von Clearwater Forest, den Intel-CEO Pat Gelsinger im Rahmen des Events Intel IFS 2024 in den Finger hielt, ähnelt letztlich sehr stark dem, was im letzten Herbst als Sierra Forest-AP gezeigt wurde. Inwiefern die doch ziemlich anders aussehenden Schaubilder in den Präsentationen und die Wirklichkeit am Ende übereinstimmen, ist aktuell schwer abzuschätzen. Im Laufe des Jahres dürfte es jedoch noch die eine oder andere Information dazu geben.