Berichte aus Korea: Samsung soll bei 3D-NAND in Kürze auf 290 Layer erhöhen

Laut Medienberichten aus Südkorea wird Samsung noch diesen Monat mit der Serienfertigung seiner 9. Generation 3D-NAND alias V-NAND V9 beginnen. Der Flash-Speicher besitzt angeblich 290 Lagen, was branchenweit bis dato die höchste Anzahl ist. Nächstes Jahr wolle Samsung direkt auf 430 Layer erhöhen.

Vorerst die meisten Schichten

Wie der Journalist Hwang Jeong-su in mehreren Artikeln berichtet, werde Samsung noch im April mit der Massenproduktion des V-NAND V9 beginnen. Dabei beruft sich der Autor auf Quellen aus der Halbleiterbranche. In den offiziellen News-Portalen von Samsung Semiconductor findet sich noch keine entsprechende Mitteilung, die aber nicht mehr lange auf sich warten lassen dürfte, sofern die Informationen stimmen.

Die Rede ist von einem nicht näher beschriebenen Flash-Speicher, der über 290 Layer verfüge, die sich auf zwei Layer-Türme (Double Stack) aufteilen. Samsung hatte zur Fachkonferenz ISSCC im Februar einen 280-Layer-Chip mit 4 Bit pro Zelle (QLC) und der mit Abstand bisher höchsten Speicherdichte von 28,5 Gbit/s vorgestellt. Es ist davon auszugehen, dass dieser ebenfalls zur Generation V9 zählt.

Dass die Layer-Zahl mit den neuen Berichten nicht exakt übereinstimmt, könnte daran liegen, dass je nach Angabe die Schichten für die Logikschaltkreise entweder mitgerechnet oder eben nicht mitgerechnet werden. Beim BiCS-5-Flash von Kioxia war beispielsweise im Vorfeld von 128 Layern berichtet worden, während zur Veröffentlichung stets 112 Layer genannt wurden.

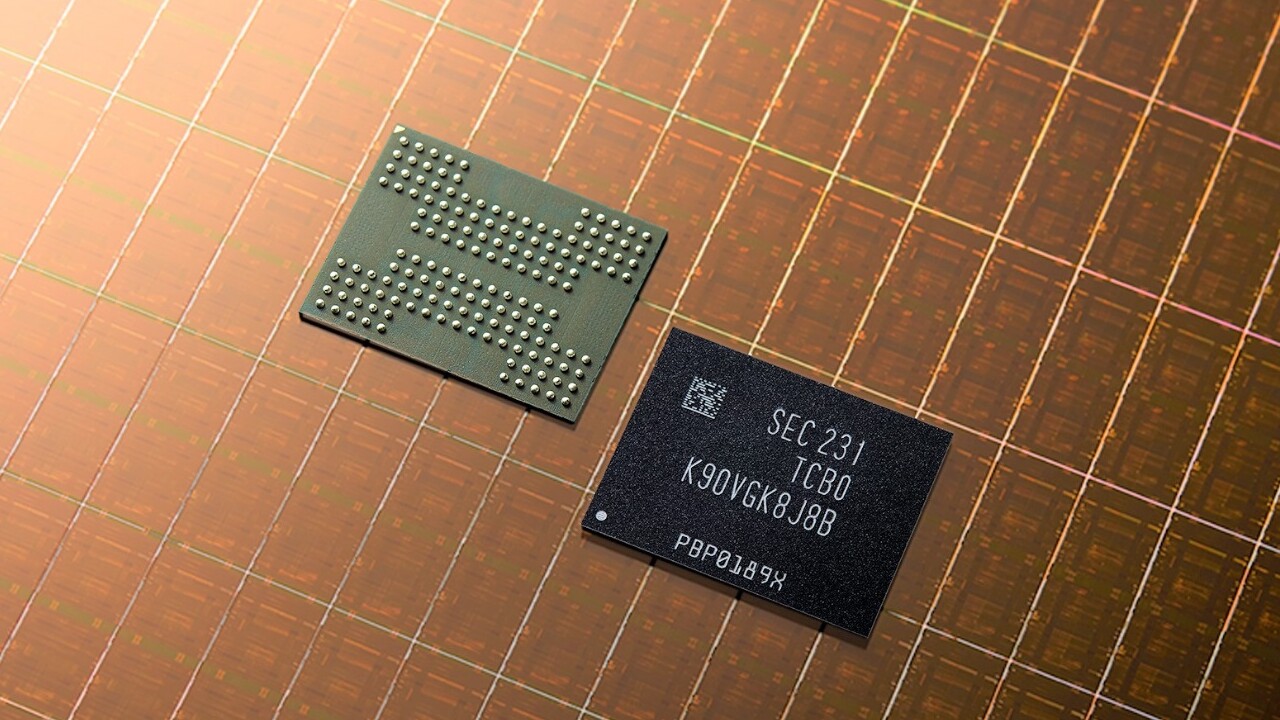

Ob nun 280 Layer oder 290 Layer ist auch gar nicht so wichtig. Zur Stunde wäre es so oder so die höchste Anzahl an Speicherschichten für marktreifen 3D-NAND. Samsungs V8 (Titelbild) bot bisher 236 Layer, erreicht aber nicht die Speicherdichte wie Micron und YMTC mit ihrem 232-Layer-NAND. Ob Samsung jetzt nur den erwähnten QLC-Speicher oder aber (auch) TLC-Varianten mit 3 Bit pro Zelle und somit weniger Speicherkapazität fertigen wird, bleibt abzuwarten.

V-NAND V10 mit 430 Layern schon 2025?

Weiter wird berichtet, dass Samsung bereits im kommenden Jahr die 10. Generation (V10) folgen lassen könnte. Diese soll dann auf Basis eines Triple-Stack-Design gleich 430 Layer aufweisen. Die Vorstellung wird für das zweite Halbjahr 2025 erwartet. Dazu gab es schon im vergangenen Jahr Gerüchte.

Auch wenn die Anzahl der Layer allein nur wenig über Leistung und Speicherdichte und die damit verbundenen Kosten aussagt, wird gerne untereinander verglichen. SK Hynix hatte zum Flash Memory Summit 2023 die Entwicklung von TLC-NAND mit 321 Layern verkündet, der nach damaligem Zeitplan im ersten Halbjahr 2025 in die Massenfertigung gelangen soll. Bei YMTC wird ein „300 Layer“ Chip für dieses Jahr erwartet, der im zweiten Halbjahr reif für die Serienfertigung sein könne.