Strix Point (Halo): AMD-Dokument bestätigt Eckdaten der Zen-5-APUs

Der Auszug aus einem mutmaßlichen AMD-Dokument nennt Spezifikationen für die ersten Zen-5-APUs von AMD. Die Angaben bestätigen die bisherigen Gerüchte um Strix Point mit bis zu 12 Kernen und Strix Halo mit sogar 16 Kernen und besonders starker Grafikeinheit.

Über den angeblichen Leak eines 144 Seiten umfassenden AMD-Dokuments berichtet die Website HKEPC und verweist auf ein Posting bei X, das inzwischen aber nicht mehr erreichbar ist. Ein Screenshot liefert aber Eckdaten zu Strix Point (STX) und Strix Halo (STX Halo).

Spezifikationen von AMD Strix Point

Zen 5 mit 1 MB L2-Cache pro Kern

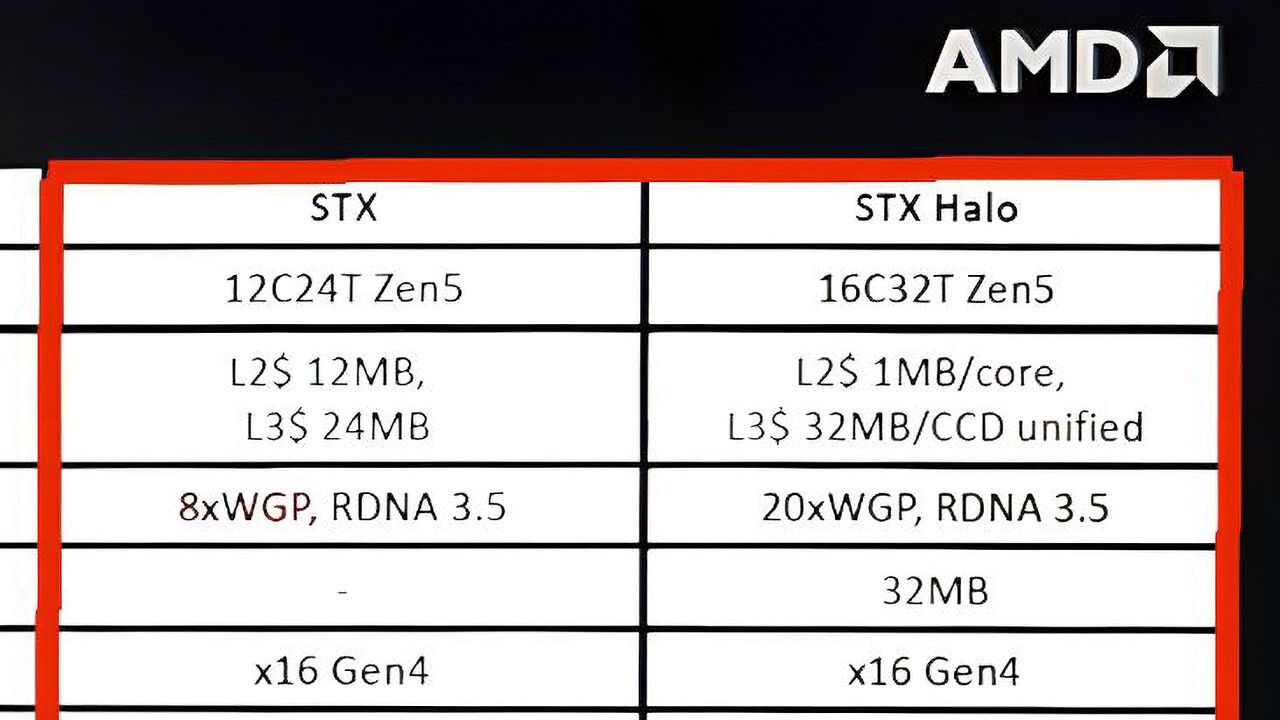

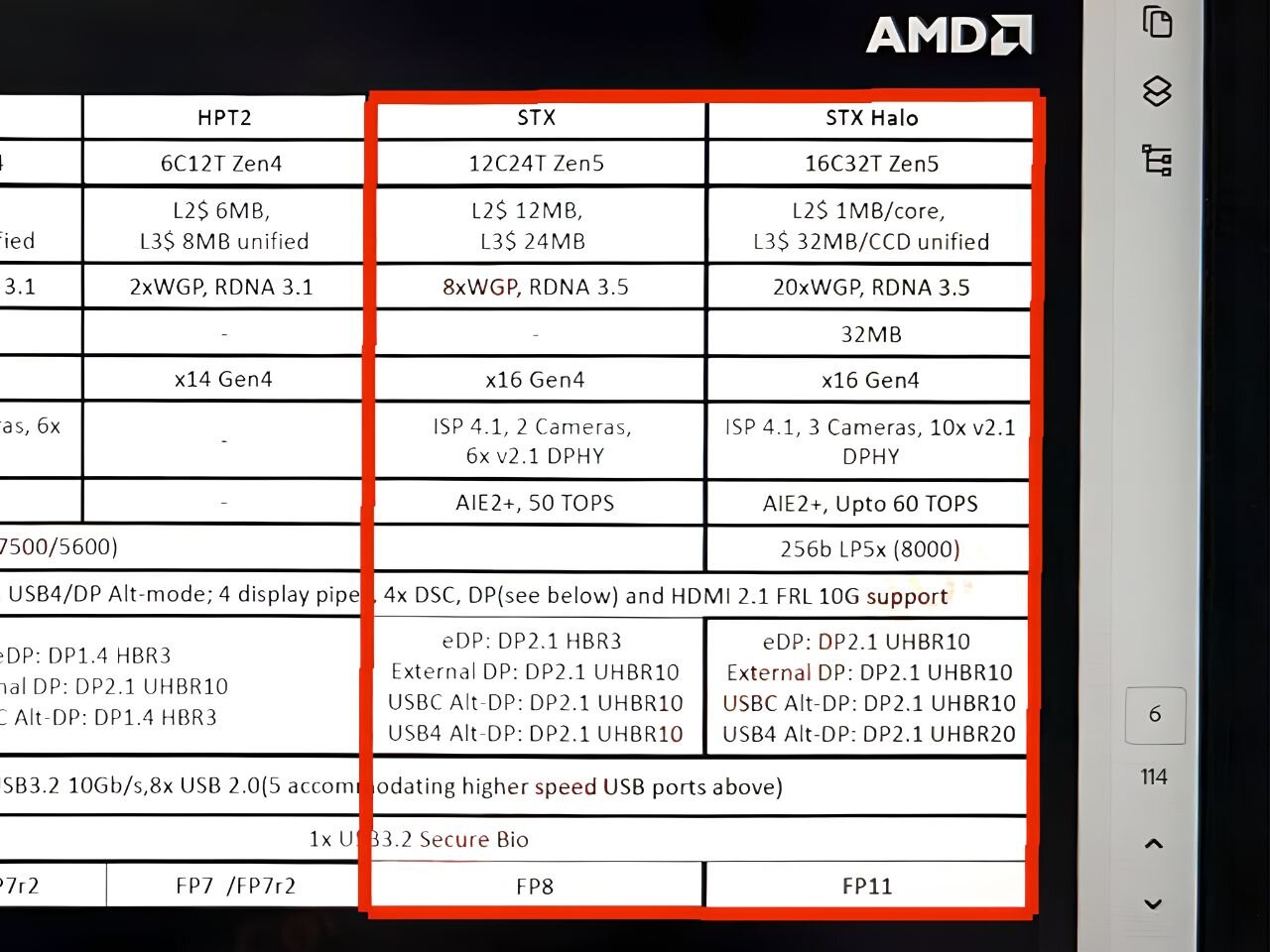

Wie erwartet soll Strix Point in der Spitze über 12 Kerne und 24 Threads verfügen. Es wird von einem monolithischen Chip mit Hybrid-Bestückung aus vier Zen-5-Kernen und acht kompakteren Zen-5c-Kernen ausgegangen, was an dieser Stelle aber nicht bestätigt wird. Jedem CPU-Kern steht demnach 1 MB L2-Cache zur Seite, was also 12 MB bedeutet. Der L3-Cache ist mit 24 MB doppelt so groß.

RDNA 3.5 mit 16 CUs

Bei der integrierten GPU ist einmal mehr von RDNA 3.5 die Rede, was RDNA 3 als Basis und erste Neuerungen von RDNA 4 vermuten lässt. Die kommende PlayStation 5 Pro soll nämlich eine RDNA-3-GPU mit neuen Raytracing-Einheiten von RDNA 4 kombinieren.

Die Angabe von 8 WGP (Work Group Processors) ergibt nach bisherigem Schema 16 Compute Units (CU). Gegenüber Hawk Point (Ryzen 8x4x mit 8 Kernen mit 12 CUs) wird es demnach also sowohl mehr CPU-Kerne als auch mehr GPU-Einheiten geben.

XDNA2-NPU mit 50 TOPS

Eine weitere Neuerung ist die NPU, die AMD bereits als XDNA2 angekündigt hatte, an dieser Stelle aber „AIE2+“ (AI Engine?) genannt wird. Die neue NPU soll KI-Berechnungen mit 50 TOPS ermöglichen, beim Vorgänger sind es bisher nur 16 TOPS.

All dies deckt sich mit den bisherigen Gerüchten. Neu sind die Angaben zu den I/O-Schnittstellen von Strix Point. Von 16 PCIe-4.0-Lanes ist die Rede, PCIe 5.0 wird an dieser Stelle nicht genannt. Letzteres bietet der Vorgänger Hawk Point aber ebenso wenig im Notebook.

Letztlich wird das neue FP8-Package und die Unterstützung von USB4 und DisplayPort 2.1 mit UHBR10 bestätigt.

Kürzlich tauchte ein Engineering Sample von Strix Point in der Geekbench-Datenbank auf.

Strix Halo

Chiplet-APU mit satten 40 CUs und 60 TOPS

Bei Strix Halo wird bisher von der ersten APU im Chiplet-Design ausgegangen. Diese soll über insgesamt 16 vollwertige Zen-5-Kerne (8 pro CCD) sowie die stärkste integrierte Grafikeinheit aller Zeiten verfügen. Ganze 20 WGP deuten auf 40 CUs hin, was mehr als bei einer dedizierten Radeon RX 7600 XT wäre. Hierzu wurden jüngst auch Benchmarks veröffentlicht, laut denen Strix Halo eine GeForce RTX 4060M schlagen kann. Ob dem wirklich so ist, bleibt abzuwarten. Zumindest werden die zuvor genannten Eckdaten jetzt noch einmal bestätigt.

Die NPU soll mit bis zu 60 TOPS noch leistungsfähiger als bei Strix Point sein, was die bisherigen Erwartungen von 45 – 50 TOPS deutlich übertrifft.

Schneller LPDDR5X, aber kein PCIe 5.0

In puncto Speicherunterstützung nennt das neue Dokument LPDDR5X-8000 und 256 Bit für Strix Halo. Die „32 MB“ dürften für den sogenannten MALL-Cache gelten, der vermutlich ähnlich wie der bisherige Infinity Cache arbeitet. PCIe 4.0 x16 ist für die große Chiplet-APU demnach ebenso gesetzt, während bei den Desktop-Prozessoren (Granite Ridge) erneut PCIe 5.0 zu erwarten ist. Für USB4 wird hier der DisplayPort-Alternate-Mode mit bis zu 20 Gbit/s (UHBR20) pro Lane genannt.

HKEPC schreibt von offiziell 70 Watt TDP bei Strix Halo, doch sollen OEMs die Möglichkeit haben, die TDP auf bis zu 130 Watt anzuheben, was mehr Luft nach oben bei Takt und Leistung bedeutet, sofern das Kühlsystem auch mitspielt.

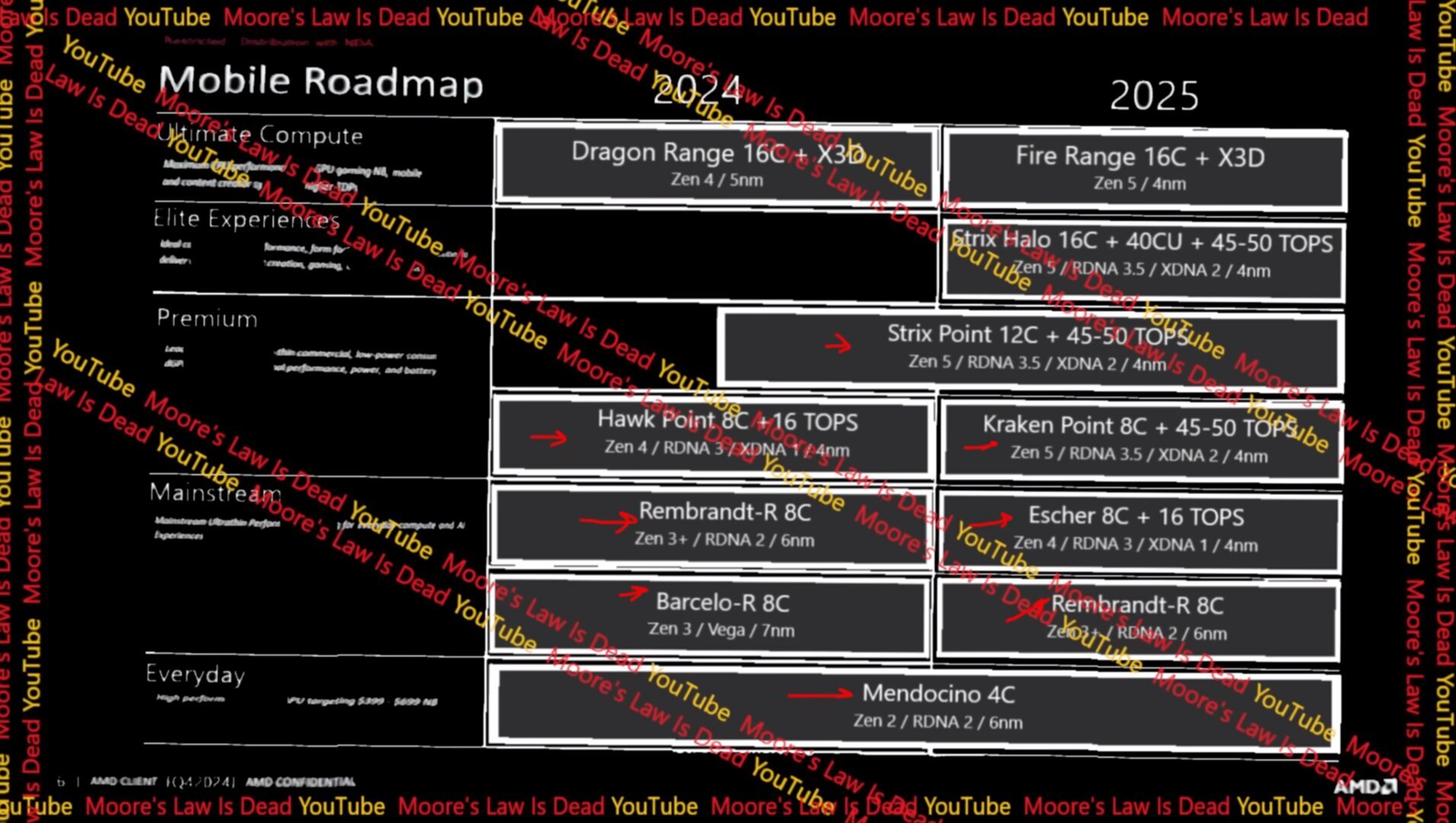

Im 2. Halbjahr startet Ryzen 9000

Als Ryzen 9xxx werden Strix Point, Strix Halo und Fire Range als Pendant für Granite Ridge im Notebook erwartet. Zumindest Strix Point soll zu den ersten Zen-5-Prozessoren im zweiten Halbjahr 2024 zählen. Strix Halo und Fire Range werden erst für 2025 erwartet.

| Codename | Sound Wave | Fire Range | Strix Halo (Sarlak?) | Strix Point | Kraken Point | Escher |

|---|---|---|---|---|---|---|

| Fertigung | ? | 4 nm | ||||

| CPU | ? | 16 Kerne, Zen 5 | 12 Kerne, Zen 5/Zen 5c | 8 Kerne, Zen 5/Zen 5c | 8 Kerne, Zen 4 | |

| 3D V-Cache | ? | ✓ | – | |||

| GPU | ? | ? | RDNA 3.5, 40 CUs | RDNA 3.5, 16 CUs | RDNA 3.5, 8 CUs | RDNA 3, ? CUs |

| KI-Beschleuniger | ? | ? | XDNA 2, 60 TOPS | XDNA 2, 50 TOPS | XDNA 1, 16 TOPS | |

| Release | 2026? | 2025 | H2 2024 | 2025 | 2025 | |