Neue CPU-Kerne: Arm Cortex-X925, A725, A520 Refresh greifen nach IPC-Krone

Arm Cortex-X925, Cortex-A725 und Cortex-A520 Refresh bilden die neue Generation von CPU-Kernen für Smartphones und mobile Endgeräte. Mit dem Cortex-X925 greifen die Entwickler nach der IPC-Krone, der Cortex-A725 soll viel Leistung mit hoher Effizienz verbinden und für den Cortex-A520 gibt es einen Refresh für die 3-nm-Fertigung.

Wenn Arm nach Texas lädt, dann weiß man, dass Großes bevorsteht. Denn am Standort in Austin entwickelt das Unternehmen die größten X-Kerne, also die Prime-Kerne, zuletzt den Cortex-X4. Der A7xx stammt übrigens aus dem französischen Technologiepark Sophia Antipolis, während der A5xx am ältesten Standort in Cambridge entwickelt wird.

Cortex-X925 statt Cortex-X5

Für die neueste Generation von CPU-Kernen, deren Designs Arm an Anbieter wie unter anderem MediaTek, Qualcomm und Samsung lizenziert, damit sie darauf basierend ihre eigenen SoC bauen können, hat Arm das Namensschema des Prime-Cores an das der anderen Kerne angepasst, sodass die neueste Lösung nicht Cortex-X5, sondern Cortex-X925 heißt.

Arm strebt nach höchster IPC-Leistung

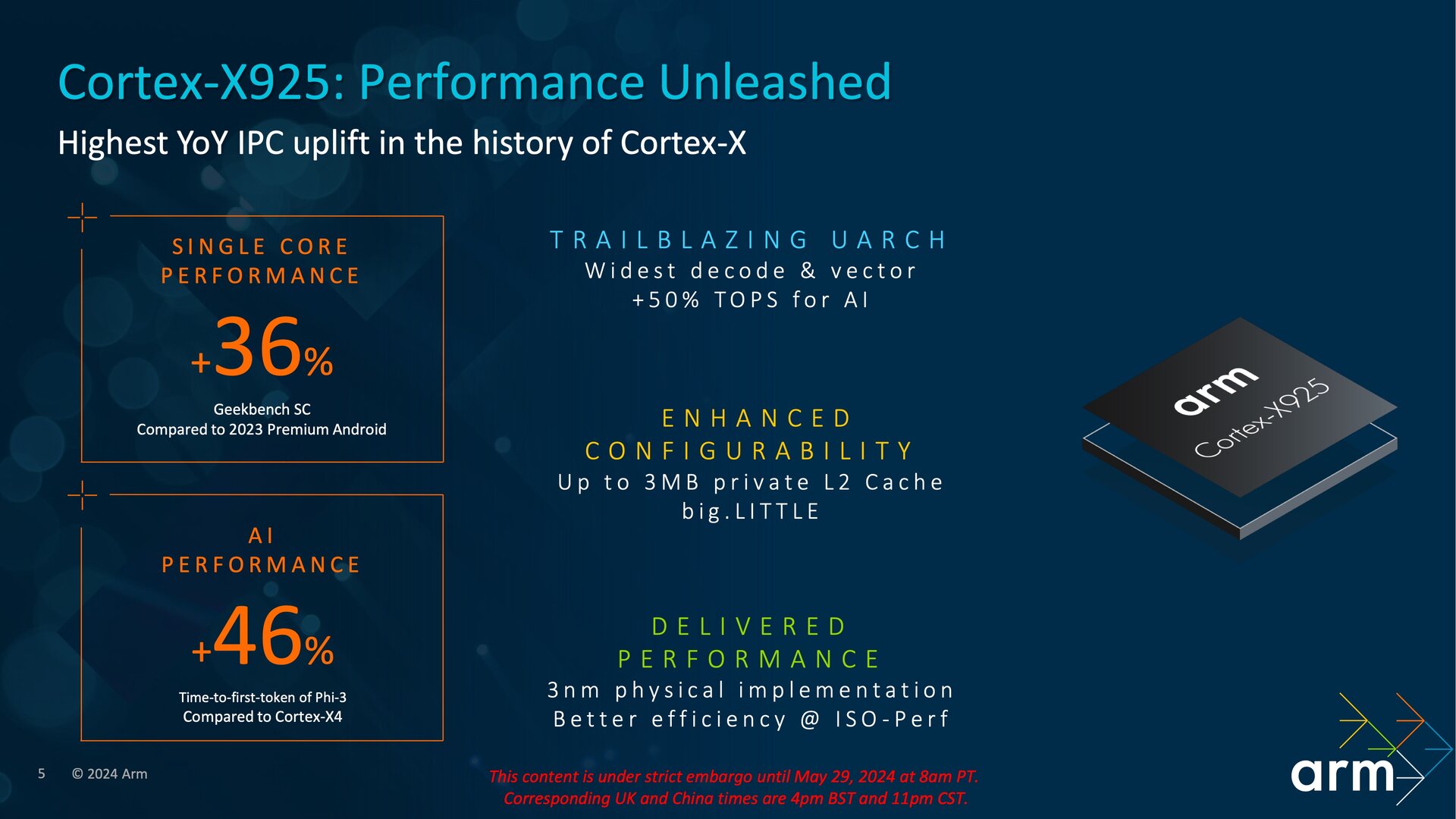

Dahinter stecke laut Arm nichts weniger als der CPU-Kern mit der höchsten IPC-Leistung aller aktuellen Kerne in Smartphone-Prozessoren – für Android und iOS. Wie viel besser Arm mit dem neuen Cortex-X925 gegenüber anderen großen Kernen in Sachen IPC („Instructions per Cycle“), also der Anzahl der von einem Prozessor in einem Taktzyklus ausgeführten Befehle, gegenüber eigenen und Lösungen der Konkurrenz abschneidet, verrät das Unternehmen allerdings nur anhand von Balkendiagrammen, die nicht immer von genauen Zahlen begleitet werden.

Im ISO-Vergleich bei gleicher Taktrate und gleichen Speicherkonditionen fährt der Cortex-X925 zum Cortex-X4 in den drei spezifisch von Arm ausgewählten Anwendungsbeispielen Geekbench 6.2, der Geschwindigkeit von App-Starts und Speedometer 2 ein Plus von jeweils rund 15 Prozent mit leichten Abweichungen nach oben und unten ein. Das ist aber kein allgemeingültiger Zugewinn, sondern das Ergebnis der Selektion durch Arm.

Apple soll mit dem Cortex-X925 geschlagen werden

In Geekbench 6.2 kann die Single-Core-Performance nämlich bestenfalls bis zu 36 Prozent höher als beim Cortex-X4 ausfallen. Doch woher stammt diese Diskrepanz? Arm vergleicht den neuen CPU-Kern mit einem namentlich nicht genannten Android-Flaggschiff aus dem letzten Jahr, dessen Chip mit Cortex-X4 bestenfalls auf 3,20 GHz (Samsung Exynos 2400), 3,25 GHz (MediaTek Dimensity 9300) oder 3,40 GHz (Qualcomm Snapdragon 8 Gen 3 for Galaxy) kam. Arm wiederum hat den Cortex-X925 für den Vergleich mit 3,80 GHz betrieben und System- und Software-Optimierungen speziell für den neuen Kern einfließen lassen, was letztlich in einem Plus von 36 Prozent im Geekbench 6.2 Single-Core resultiert. Ein Cortex-X925 mit 3,80 GHz ohne diese Optimierungen und ein „2023 Best-in-Class @ 3,8 GHz“, bei dem es sich vermutlich um den großen Kern im A17 Pro von Apple handelt, landen hinter der optimierten Cortex-X925-Implementierung.

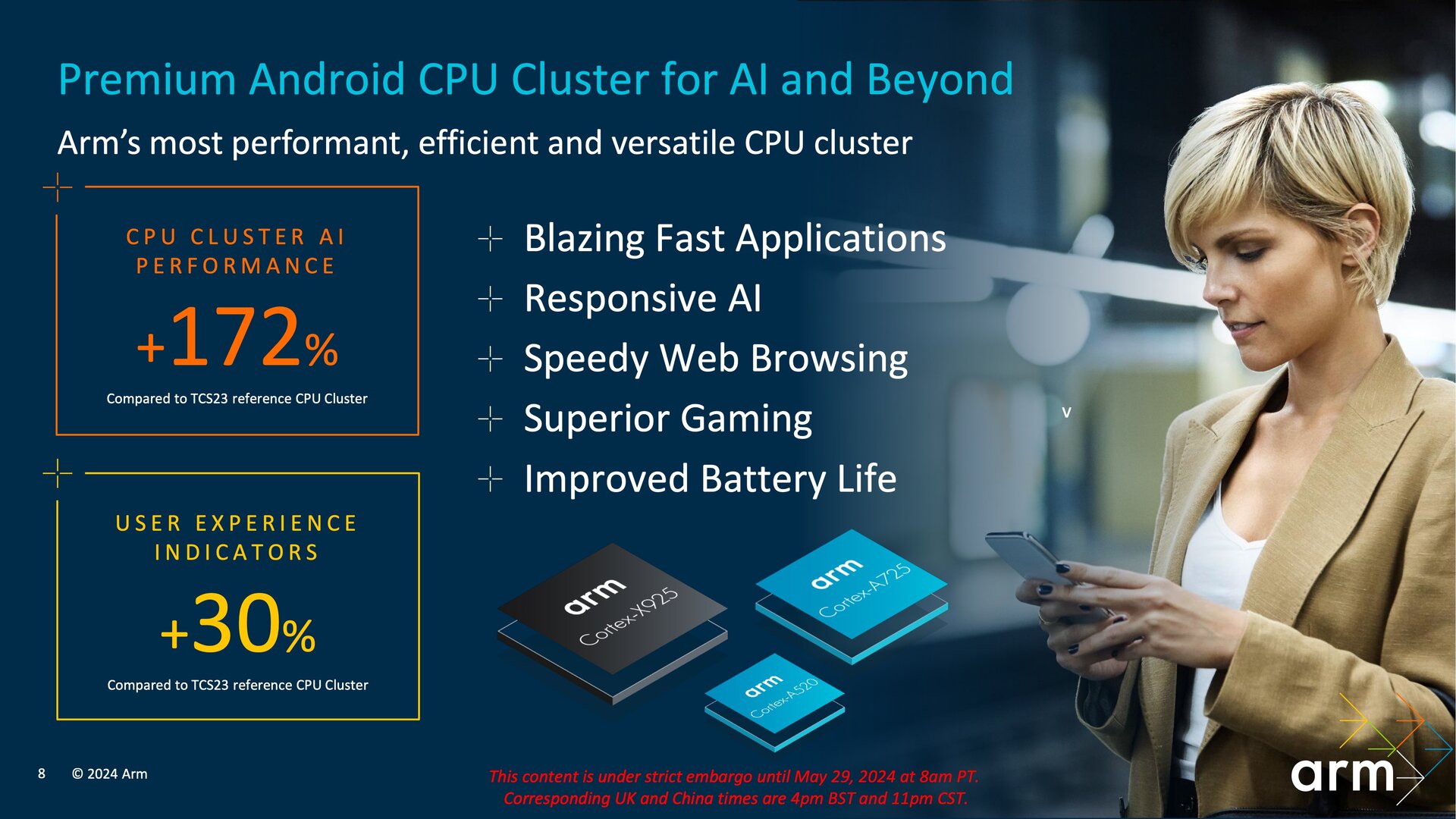

Die Leistung soll in der Praxis ankommen

Arm will aber nicht einfach nur in einzelnen Benchmarks besser abschneiden, indem speziell darauf optimiert wird, sondern die Leistung und Effizienz soll im Alltag tatsächlich beim Endverbraucher ankommen und zu spüren sein. Im Durchschnitt soll es über die Anwendungsbereiche Benchmarks, App-Starts, Web, Gaming, AI und Gen AI, Medien und Idle mit der Kombination aller drei neuen Kerne sowie deren Integration in die aktualisierte DSU-120 („DynamIQ Shared Unit“) eine Verbesserung um 30 Prozent für Leistung und Effizienz geben.

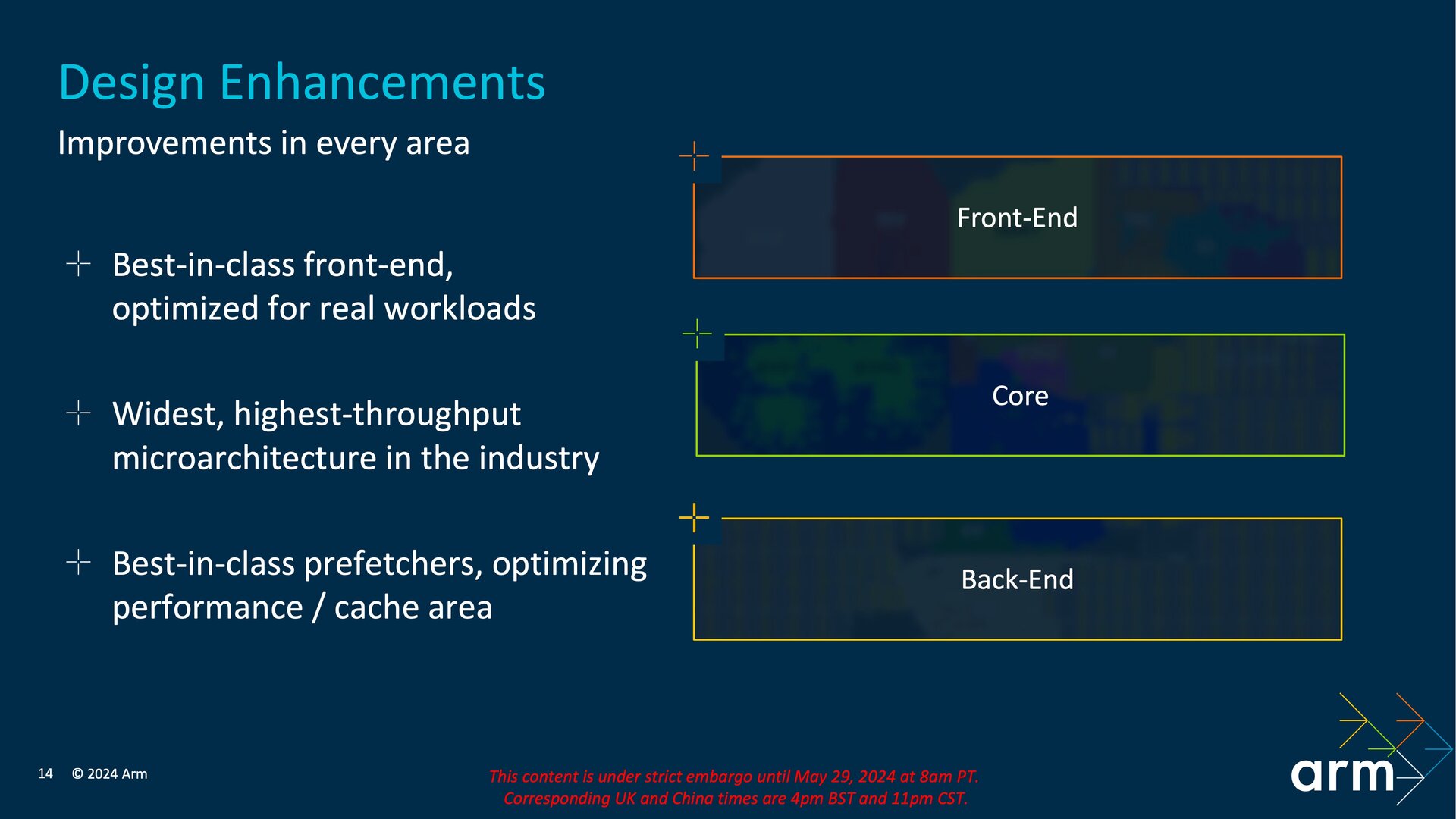

Das neue Front End des Cortex-X925

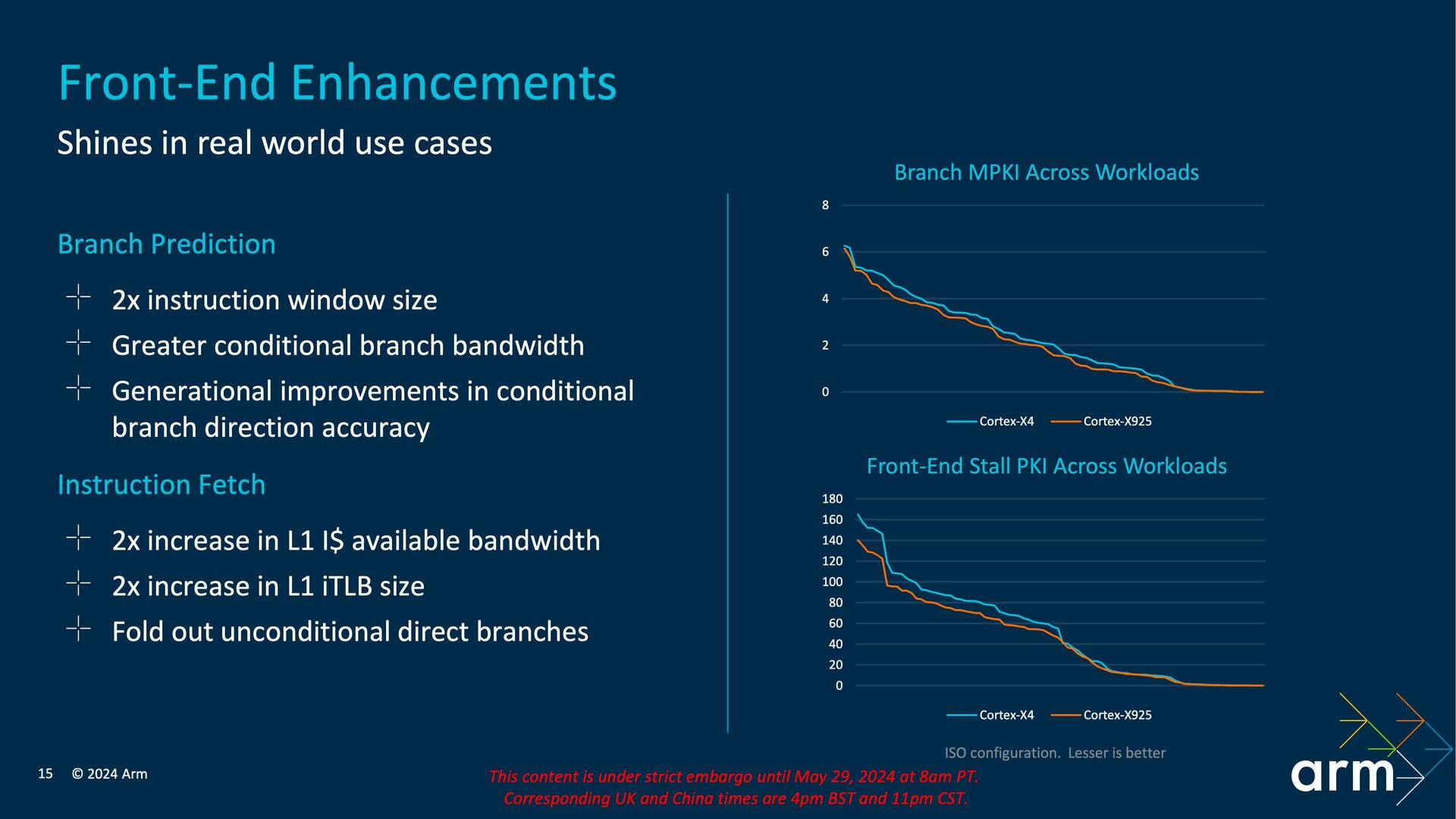

Für den Cortex-X925 hat sich Arm Spitzenleistung bei gleichzeitig reduziertem Energiebedarf unter Berücksichtigung der Optimierung für die 3-nm-Fertigung zum Ziel gesetzt. Überarbeitet hat das Unternehmen dafür wie in den letzten Jahren das Front End, den Core und das Back End des größten Kerns. Das Front End ist bei einem Prozessor für die Sprungvorhersage, das Fetching aus dem Speicher und das Decoding zuständig.

Dort können aufseiten der Sprungvorhersage jetzt doppelt so viele Instruktionen wie noch beim Cortex-X4 verarbeitet werden. Arm hat außerdem die Bandbreite für bedingte Branches erhöht, die in Abhängigkeit zu einer Kondition ausgeführt oder eben nicht ausgeführt werden. Für diese Art von Branches bei der Sprungvorhersage seien außerdem allgemeine Verbesserungen zwecks einer höheren Genauigkeit eingeflossen. Arm gibt für das Fetching eine Verdoppelung der Bandbreite für den L1-Instruction-Cache an, zudem falle der „L1 Instruction Translation Lookaside Buffer“ (L1 iTLB) mit der Neuauflage doppelt so groß aus.

Der Core bleibt ein 10-wide-Design

Für den Core bleibt es dieses Jahr wie zur Einführung des Cortex-X4 im letzten Jahr bei einem großen „10-wide“-Design, das jetzt aber effektiver genutzt werden könne. Die Ausführung von SIMD/FP („Single Instruction, Multiple Data/Floating Point“) erweitert Arm von 4x128b auf 6x128b und in den Integer-ALU-Pipelines können Operationen neben einem Taktzyklus jetzt auch über zwei Taktzyklen verarbeitet werden. Möglich sind mit dem Cortex-X925 auch doppelt so viele Ausführungen von Integer-Multiplikationen und Floating-Point-Vergleichen.

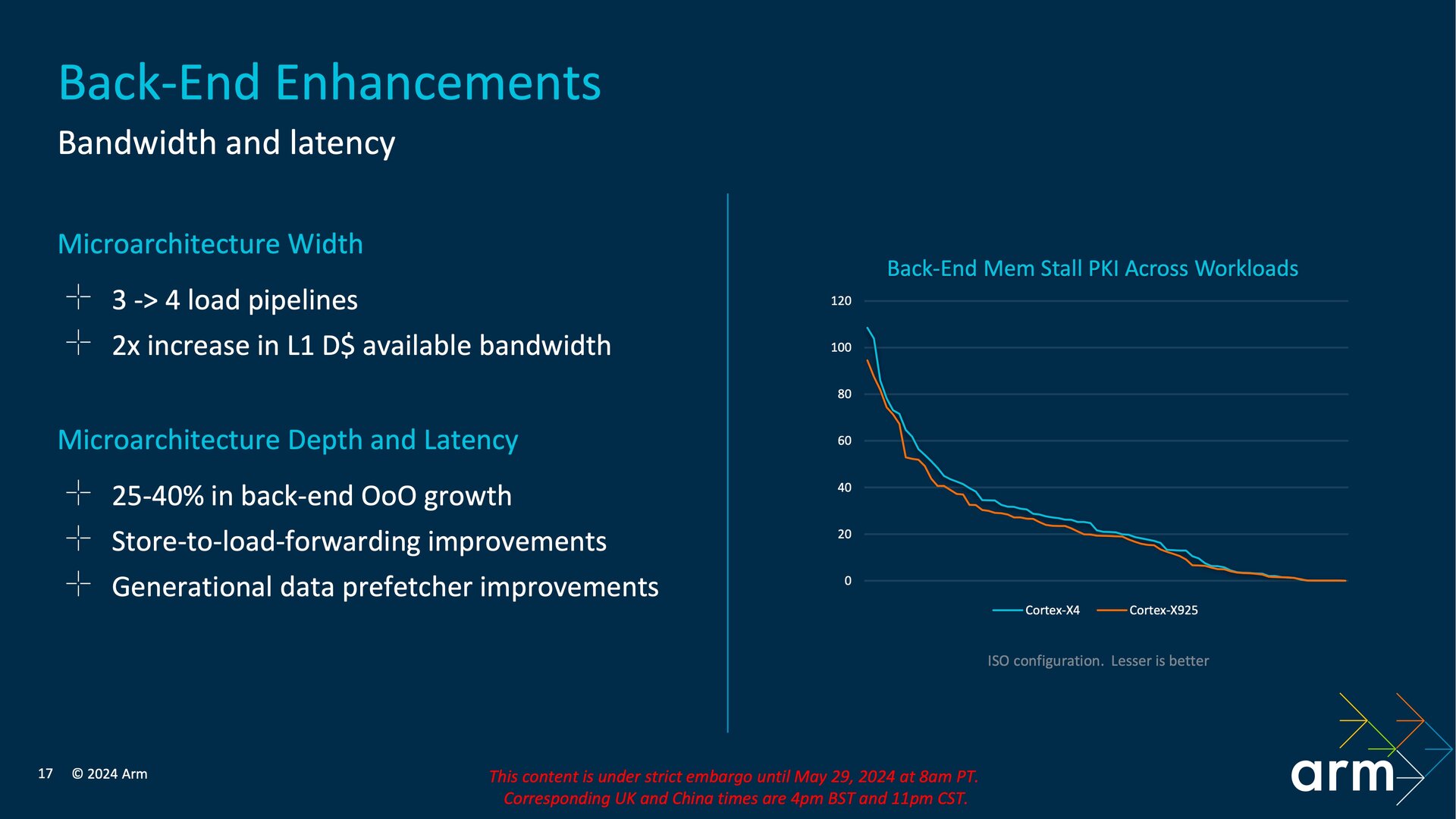

Back End erhält eine weitere Load-Pipeline

Im Back End des Kerns gibt es eine Umstellung der AGUs („Address Generation Units“) für Load/Store-Befehle. Mit dem Cortex-X4 hatte Arm davon eine vierte hinzugefügt und die AGUs auf insgesamt mehr dedizierte Einheiten ausgerichtet. Aus der bislang einen AGU für Load/Store-, den zwei AGUs nur für Load- und einer AGU nur für Store-Befehle wird bei letzterer im Back End des Cortex-X925 eine duale AGU für Load/Store-Befehle, sodass effektiv eine Load-Pipeline hinzugekommen ist. Die Bandbreite für den L1-Data-Cache fällt doppelt so groß aus.

Cortex-A725 für AI- und Gaming-Dauerlast

Abseits der Spitzenleistung des Cortex-X925 zielt Arm mit dem neuen Cortex-A725 auf eine anhaltend hohe Multi-Core-Leistung der großen Kerne unterhalb der größten Prime-Kerne. Dabei hat das Unternehmen vor allem eine hohe AI- und Gaming-Leistung unter Dauerlast bei gleichzeitig hoher Effizienz im Fokus. Optimierungen am Registerspeicher des Kerns, ein erweiterter Re-Order-Buffer und andere Maßnahmen sollen dem Cortex-A725 zu bis zu 35 Prozent mehr „Performance Efficiency“ verhelfen, wobei Arm hier Metriken für Leistung und Effizienz vermischt, ohne sie exakt zu benennen. Laut Diagramm bietet der Kern stets mehr Leistung und verbraucht weniger als der Vorgänger Cortex-A720.

Energieeffizienz um 25 Prozent verbessert

25 Prozent höher falle die Energieeffizienz laut Arm aus, wobei in diese Angabe auch die Optimierungen des Designs für die 3-nm-Fertigung einfließen. Die Angabe bezieht sich auf einen Vergleich mit dem Cortex-A720 aus 4-nm-Fertigung mit nur halb so großem L2-Cache (1 MB vs. 512 KB). Aufgrund der 3-nm-Fertigung erreiche Arm obgleich der neuen Option eines 1 MB statt 512 KB großen L2-Caches trotzdem „ISO-Area“, also die gleiche Flächengröße wie beim Vorgänger, sodass es in diesem Aspekt zu keiner Einbuße bzw. nicht zu höheren Kosten komme. Arm bietet für günstigere SoC ohne Prime-Kerne wieder eine flächenoptimierte Variante des Cortex-A720 mit kleinerem Cache an.

Cortex-A520 erhält einen Refresh

Den kleinsten Cortex-A5xx erneuert Arm alle zwei Jahre, dazwischen gibt es einen Refresh der bisherigen Mikroarchitektur. Der Cortex-A520 Refresh hat deshalb lediglich kleinere Optimierungen vor allem für die Fertigung in 3 nm erhalten, die den Energieverbrauch um 15 Prozent gegenüber dem Cortex-A520 reduzieren sollen.

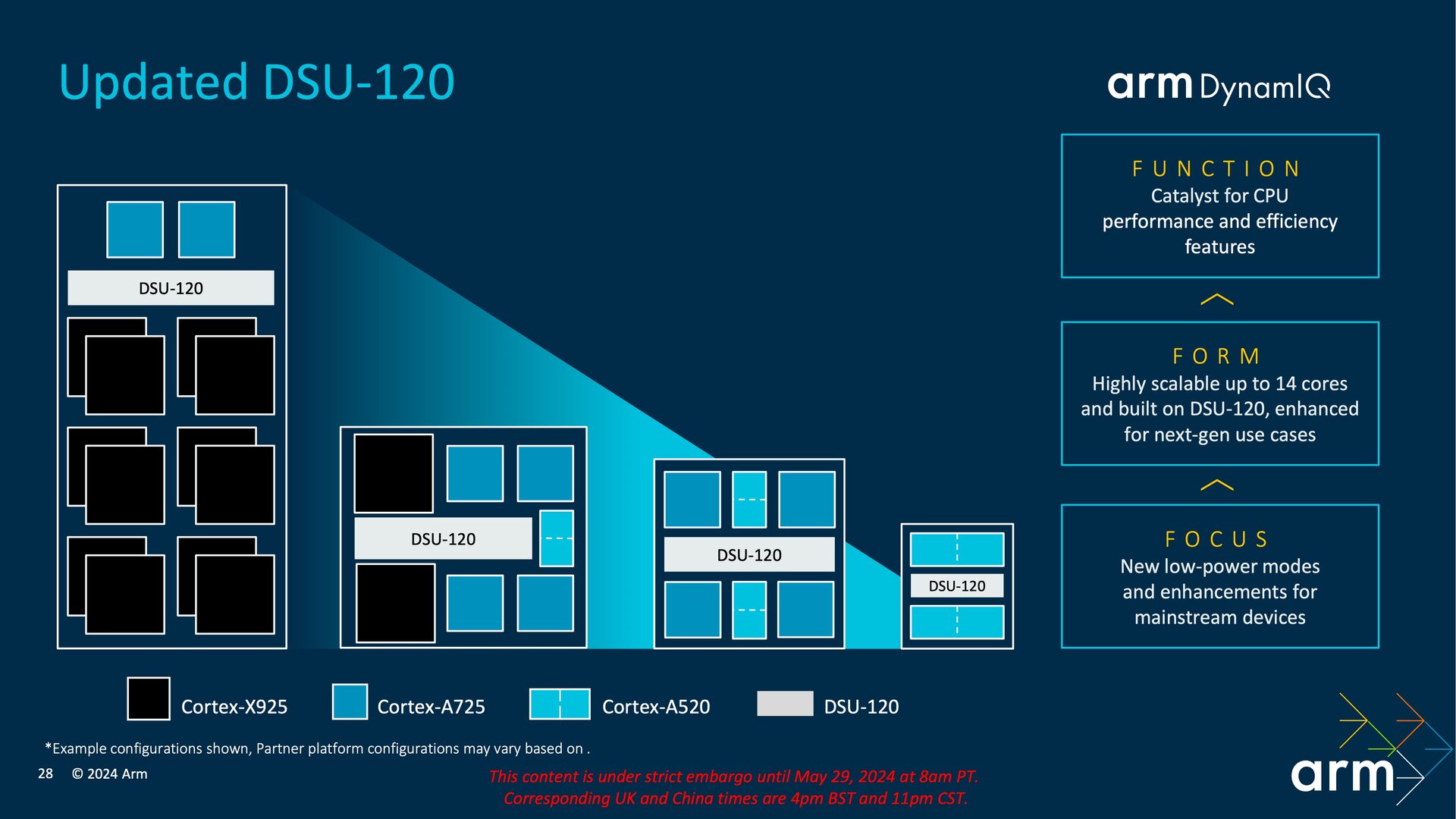

DSU-120 nimmt wieder bis zu 14 Kerne auf

Versammelt sind die CPU-Kerne abermals in der DSU-120 („DynamIQ Shared Unit“), die unter demselben Namen wie im Vorjahr läuft und weiterhin maximal 14 Kerne aufnehmen kann, deren Konfiguration sich je nach Endgerät und dessen anvisierter Preisklasse massiv unterscheiden kann. Bei Bedarf lassen sich mehrere DSU-120 betreiben, sofern mehr als 14 Kerne benötigt werden, was in der Praxis aber keine Rolle spielt.

2+4+2-Konfiguration für High-End-Smartphones

Arm erwartet, dass im späteren Verlauf dieses Jahres und im kommenden Jahr, wenn erste SoC auf Basis der neuen Kerne von den Partnern angekündigt werden dürften, bei Chips für Top-Smartphones ein neuer Aufbau mit 2+4+2 Kernen genutzt werde. Somit ist bei den Smartphones der nächsten Generation von zwei Cortex-X925, vier Cortex-A725 und zwei Cortex-A520 Refresh auszugehen. Im letzten Jahr hatte Arm für 2024 eine Umstellung von 1+3+4 auf 1+5+2 für High-End-Geräte prognostiziert, diesmal geht der Designer sogar auf 2+4+2.

Arm-Notebooks bekommen zwölf Cortex-X925

Bei den aktuell im Trend liegenden Notebooks mit Arm-Architektur ist von SoC mit einem 12+2-Aufbau, also zwölf Cortex-X925 und zwei Cortex-A725 auszugehen, während günstigere Smartphones und andere Geräte mit geringen Leistungsanforderungen auf 4+4 (A725/A520R) oder ausschließlich vier Cortex-A520 Refresh setzen könnten.

Arm optimiert Flächenbedarf der DSU

Völlig unangetastet lässt Arm die DSU-120 aber nicht, deshalb spricht der Designer für dieses Jahr auch von einer „Updated DSU-120“. Die DSU komme mit einem bei „typischen Workloads“ um 50 Prozent reduzierten Energieverbrauch, weil bei den drei Stellschrauben der PPA (Power-Performance-Area) unter anderem Optimierungen der Datenkanäle unter den verschiedenen Cores und die benötigte Fläche der günstigeren Designs für den Massenmarkt, sprich ohne Prime-Cores, weiter reduziert worden seien.

Half Slice Powerdown spart Energie

Arm kann in der aktualisierten DSU-120 aber auch die Leckströme durch einen neuen „Half Slice Powerdown“ der Slices mit den L3-Caches und Snoop-Filtern reduzieren. Innerhalb der DSU wird der bis zu 32 MB große L3-Cache auf bis zu acht Slices verteilt, die über ein bidirektionales Ringbussystem untereinander und mit den CPU-Kernen verbunden sind. Im letzten Jahr hatte Arm neu eingeführt, wie feingliedrig diese Slices, die darin enthaltenen Caches und die Logikschaltungen drum herum für einen möglichst effizienten Betrieb aktiviert und vor allem deaktiviert werden können. Zwischen dem bereits bekannten „Half RAM Powerdown“ mit jeweils zur Hälfe deaktivierten L3-Caches und dem „Slice 0 Only Mode“ mit nur einem einzigen aktiven Slice zieht dieses Jahr ein neuer „Half Slice Powerdown“ mit somit zur Hälfte aktivierten/deaktivierten Slices in die DSU-120 ein.

Quick-Nap-Mode für den L3-Cache

Vollständig neu ist der „L3 Quick Nap Mode“, über den sich die L3-Caches kurzzeitig schlafen legen lassen, was unabhängig von dem Betriebszustand der aktuell aktiven Slices erfolgen kann. Die einzige Ausnahme stellt das „Max Leakage Saving“ dar, bei dem ohnehin alle Slices bis auf einen deaktiviert werden, in dem dazu der L3-Cache bereits nicht mehr aktiv ist und nur noch der Snoop-Filter arbeitet. „L3 Quick Nap Mode“ bedeutet, dass der Cache-Inhalt gehalten werden kann, sich während dieses kurzzeitigen Energiesparmodus aber nicht mehr in den Cache schreiben oder daraus lesen lässt.

Praxisnahe Leistungs- und Effizienzsteigerungen

Zusammengefasst ist der Cortex-X925 vor allem für App-Starts, das Web und teils auch für AI-Workloads ausgelegt, der Cortex-A725 für AI und Gaming und der Cortex-A520 Refresh für Medien und Idle. High-End-Smartphones dürften dabei auf eine 2+4+2-Konfiguration setzen, Mainstream-Lösungen aber auf die Prime-Cores verzichten. Ziel aller neuen Lösungen sind praxisnahe Leistungs- und Effizienzsteigerungen.

ComputerBase hat Informationen zu diesem Artikel von Arm unter NDA im Rahmen einer Veranstaltung des Herstellers in Austin, Texas erhalten. Die Kosten für An-, Abreise und drei Hotelübernachtungen wurden von dem Unternehmen getragen. Eine Einflussnahme des Herstellers oder eine Verpflichtung zur Berichterstattung bestand nicht. Die einzige Vorgabe aus dem NDA war der frühestmögliche Veröffentlichungszeitpunkt.

Dieser Artikel war interessant, hilfreich oder beides? Die Redaktion freut sich über jede Unterstützung durch ComputerBase Pro und deaktivierte Werbeblocker. Mehr zum Thema Anzeigen auf ComputerBase.