Technology Symposium 2024: TSMC zu neuen Technologien, ASML, Intel und Deutschland

In dieser Woche hat TSMC in Europa das jährliche Technology Symposium abgehalten und über neue Technologien, ASML, Intel & Co gesprochen. Dabei lieferte der Branchenriese einmal mehr beeindruckende Zahlen und legte umfangreiche Pläne vor, die natürlich auch den deutschen Standort und das neu gegründete ESMC einschließen.

ESMC wird ab Q4/2024 gebaut

ESMC ist der Name für das strategische Konsortium aus Bosch, Infineon, NXP und TSMC, die zusammen in Dresden eine Fabrik bauen, in der Chips in den Fertigungsstufen N28 und N16 vor allem für die Automobilbranche, aber auch andere industrielle Bereiche gefertigt werden. Spatenstich für die Fabrik ist nach aktuellen Plänen im vierten Quartal dieses Jahres, die Serienproduktion soll 2027 starten, bestätigte TSMC in dieser Woche in Amsterdam.

Jedermanns Foundry mit achtsamem Blick zu Intel

Was TSMC im letzten Jahr geleistet hat, weiß in nackten Zahlen zu beeindrucken. Insgesamt 288 verschiedene Prozesstechnologien hat das Unternehmen bisher hervorgebracht und so im vergangenen Jahr 11.895 verschiedene Produkte für 528 Kunden gefertigt. Die Zahlen erinnern an das Vorjahr, als es 12.698 Produkte für 532 Kunden waren.

TSMC bekräftigt mit den Angaben einmal mehr den immer verfolgten Standpunkt, eine Foundry für jedermann zu sein. Darum beneiden die Mitbewerber TSMC natürlich, vor allem Intel würde als Herausforderer, dessen Auftragsfertigerumsatz zuletzt sogar wieder sank, hier gern einige Kunden für sich gewinnen. Aktuell ist es noch ein Vergleich David gegen Goliath: Während Intel durch große Investitionen Milliarden US-Dollar verbrennt, gewinnt TSMC jedes Quartal Milliarden.

Dennoch sieht sich TSMC Intel sehr genau an, unterschätzen sollte man einen Mitbewerber und Konkurrenten nie, das weiß auch TSMC. Schnell läuft es einmal selbst nicht rund und ein Jahr ist verloren. Beim aktuellen N3-Prozess erwischte es TSMC seit langer Zeit zum Beispiel mal wieder, der Prozess lieferte nicht das, was erwartet worden war. Und bei N2 plus, dem folgenden Prozess, ist der Ausgang ziemlich offen. Auf dem Papier und was die Investitionen in die Fertigung betrifft, holt Intel deutlich auf und versucht TSMC in einigen Bereichen sogar zuvorzukommen, weshalb TSMC ebenfalls reagiert. Das sieht man bei den Ausgaben im Bereich Forschung und Entwicklung (R&D) sowohl beim Geld als auch Personal.

High-NA EUV: „Ich mag die Technologie, aber nicht ihren Preis“

Das Thema High-NA EUV ist seit Wochen und Monaten auf der Bühne, vor allem durch Intel. Die Amerikaner sorgen medial für mächtig Krawall, wollen sie mit High-NA EUV doch mal wieder vorangehen und nicht wie bei dem bisherigen EUV zig Jahre zu spät dran sein. Die Einführung will Intel bei 14A forcieren, TSMC sagt zum Fertigungsschritt A16, dass es dort noch nicht benötigt wird, wird also eventuell den Schritt A14 dafür auswählen.

Kevin Zhang, TSMCs Chef in diesem Bereich, erklärte die Hintergründe ganz plakativ: Die Technologie ist super, der Preis aber nicht. Aktuell sieht TSMC die Balance zwischen der Technologie und der Ökonomie noch nicht gegeben. Deshalb will TSMC die A16-Chips noch mit klassischer EUV-Technologie fertigen.

Die Rhetorik erinnert dabei ein wenig an das, was Intel vor knapp zehn Jahren über EUV sagte. Verbissen blieb Intel damals bei der Immersionslithografie und fuhr damit aufs Abstellgleis, erst seit dem letzten Jahr wird nun auch bei Intel auf EUV gesetzt.

Intel versuchte zuletzt den hohen Anschaffungspreis von 350 bis 400 Millionen US-Dollar für eine High-NA-EUV-Maschine und damit rund doppelt so viel wie die bisherigen EUV-Systeme zu rechtfertigen (die neuesten Low-NA-EUV-Scanner sind laut ASML aber auch teurer als zuvor): Die Systeme werden viele Jahre im Einsatz sein, sind zudem in den vergangen Jahren so umfangreich aufrüstbar geworden, dass teilweise noch DUV-Scanner im Einsatz sind, die vor rund 20 Jahren gekauft wurden. Die Ausbeute bei den High-NA-Systemen soll zudem direkt zum Start so hoch sein wie bei aktuellen EUV-Maschinen – deren Start war ungleich komplizierter. Zudem werde sich am Preis kaum etwas tun. Eher im Gegenteil, die Maschinen dürften in den nächsten Jahren tendenziell noch teurer werden. Da die Systeme ohnehin nur für die kritischsten Lagen genutzt werden, die Wafer dann in andere Maschinen weiterziehen, bleiben die Argumente für die Systeme aktuell stark.

Wie dem auch sei: Die Investition in diese Technologie ist nur aufgeschoben, daran vorbei kommt TSMC nicht – das lässt auch Zhang mit seinem Kommentar schon durchblicken: Erste Tools sind auch bereits von TSMC bei ASML bestellt worden.

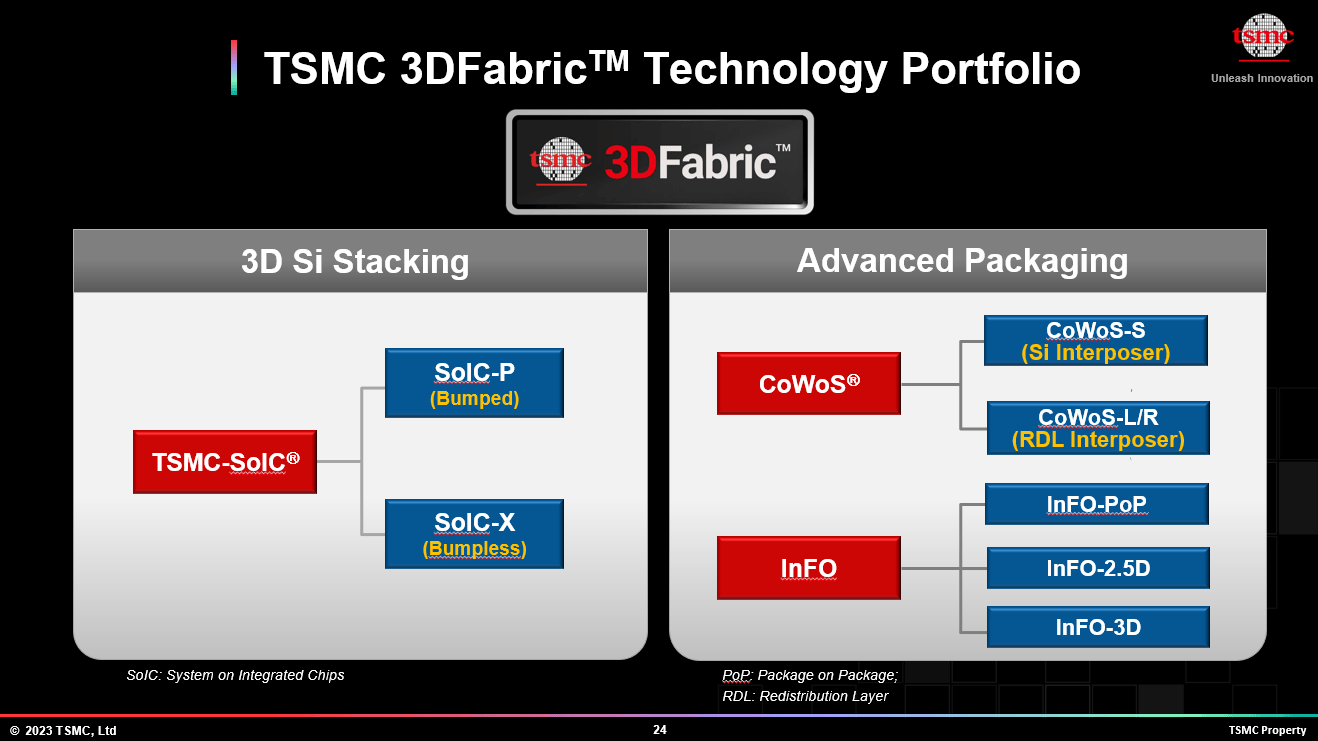

Packaging mit CoWoS als Zugpferd

Neben der Fertigung bleibt das Packaging eine der größten Stärken von TSMC. Die beginnt bei kleinen Lösungen für mobile Chips bis hin zum nun ebenfalls weithin bekannten CoWoS (Chips on Wafer on Substrat), welches Nvidias Chips nutzen. Der neue Blackwell-Chip ist der erste, der die Adaption CoWoS-L in Großserie nutzen wird und dabei zwei N4P-SoCs mit acht HBM-Chips verknüpft. Der Erfolg von CoWos in Zahlen ausgedrückt: 25 Kunden mit über 150 Produkten sollen in diesem Jahr beliefert werden.

SoIC als Lösung für das Stacking wie beispielsweise beim 3D-Cache der Ryzen-X3D-CPUs kocht mit geplanten 30 Tapeouts bis zum Jahr 2026 auf deutlich kleiner Flamme, gewinnt aber auch an Fahrt, betont TSMC. Dabei kann es in Zukunft auch zu einer Kombination kommen: Für das Jahr 2027 werden modernste A16-Chips mit SoIC-Technologie flankiert von 12 HBM-Chips als CoWoS-Produkt geplant.

Wird die Technologie InFO bereits heute auf Wafer-Größe (System on Wafer, SoW) umgesetzt, soll sie bis zum Jahr 2027 auch bei CoWoS entstehen. Dabei sollen die Erfahrungen von InFO-SoW, wie sie aktuell gemacht werden, direkt in die Produktionspläne einfließen und so die nächste Generation aus Supercomputer-Chips hervorbringen können.

Für all diese Fälle muss und wird TSMC aber weiterhin Packaging-Kapazität ausbauen. Denn in Zukunft wird auch das Automotive-Segment neue Chips erhalten, die auf InFO-OS und CoWoS-R setzen.