AI-Chips-Boom: Neben HBM-Chips fürs Packaging werden Interposer knapp

Auch ohne Interposer geht bei den aktuellen AI-Beschleuniger-Chips nichts. Nun werden sie ebenfalls zu einem knappen Gut, denn die größten ihrer Art werden in riesiger Menge benötigt. Bei den Interposern greift TSMC unter anderem auf UMCs Fertigung zurück, die jetzt expandieren soll.

Interposer stecken in fast jedem AI-Beschleuniger

Die Entwicklung hin zu Multi-Chip-Lösungen, die auf einem Package sitzen, hat die Packaging-Industrie überrannt. Den größten Anteil daran hat der AI-Boom, denn die dafür aufgelegten Produkte werden bei stark steigender Leistung größer und größer und immer komplexer. Die Zeiten, in denen eine GPU auf einem PCB mit Speicherchips verbunden war, sind vorbei.

GPU und HBM-Speicher sitzen schon länger zusammen auf einem Package und statt einem GPU-Die nebst vier HBM-Chips sind nun zwei plus sechs oder acht die Regel, eine Variante mit vier GPUs/CPUs und bis zwölf HBM-Chips ist der nächste Schritt. Um diese einzelnen Bauteile performant miteinander zu verbinden, kommt ein elektrisches Interface namens Interposer zum Einsatz.

TSMCs CoWoS ist die Technologie der Wahl

Im Fokus für die Fertigung steht dabei aktuell noch nahezu ausschließlich TSMC mit CoWoS, Chips on Wafer on Substrat. CoWoS umfasst die Schritte, die in der Packaging-Fab gegangen werden.

Die GPUs und HBM-Chips kommen dabei von externen Zulieferern (bei den GPUs ist dies meist einfach eine andere TSMC-Fab) und werden auf dem Interposer auf dem Package vereint. Doch selbst wenn es GPUs, HBM und freie Kapazitäten in der Fab gibt, heißt das nicht, dass CoWoS auch durchgeführt werden kann: Immer häufiger fehlt es am Interposer, dem „W“ in CoWoS.

Schon zuletzt habe TSMC sich daher Hilfe ins Boot geholt, schrieb TrendForce bereits 2023. UMC übernimmt demnach den CoW-Anteil, Amkor und SPLI nehmen dann diese Wafer und packen sie auf ein Substrat (WoS). Wie exakt im Detail das aussieht, darüber gibt es aber keine Informationen.

Fünf bis zehn Interposer pro Wafer

UMC hat jedoch eine kaum ausreichende Kapazität, vor allem die steigende Größe der Interposer ist ein Problem. Heute sind diese 2.500 bis 2.800 mm² groß, pro Wafer gibt es deshalb nicht einmal ein Dutzend. Sollten dann am Ende noch ein oder zwei nicht vollständig funktionieren beziehungsweise in weiteren Arbeitsschritten herausfallen, bleiben am Ende vielleicht sieben Stück pro Wafer übrig, rechnet The Elec vor.

Bis zum letzten Jahr hatte UMC gerade einmal eine Kapazität von 3.000 Wafern im Monat für Silicon Interposer in 40-nm-Fertigung. Diese sollte zu Beginn dieses Jahres auf 6.000 Stück verdoppelt werden, anvisiert werden bis Jahresende nun rund 10.000 Wafer pro Monat. Dann steht aber auch die nächste Generation an Interposern an, die bis zu 3.400 mm² groß sind, noch weiter hinaus geht es dann spätestens ab 2026/2027. Realistisch gesehen kommen dann noch höchsten fünf Interposer von einem 300-mm-Wafer – bei 100 Prozent Yield.

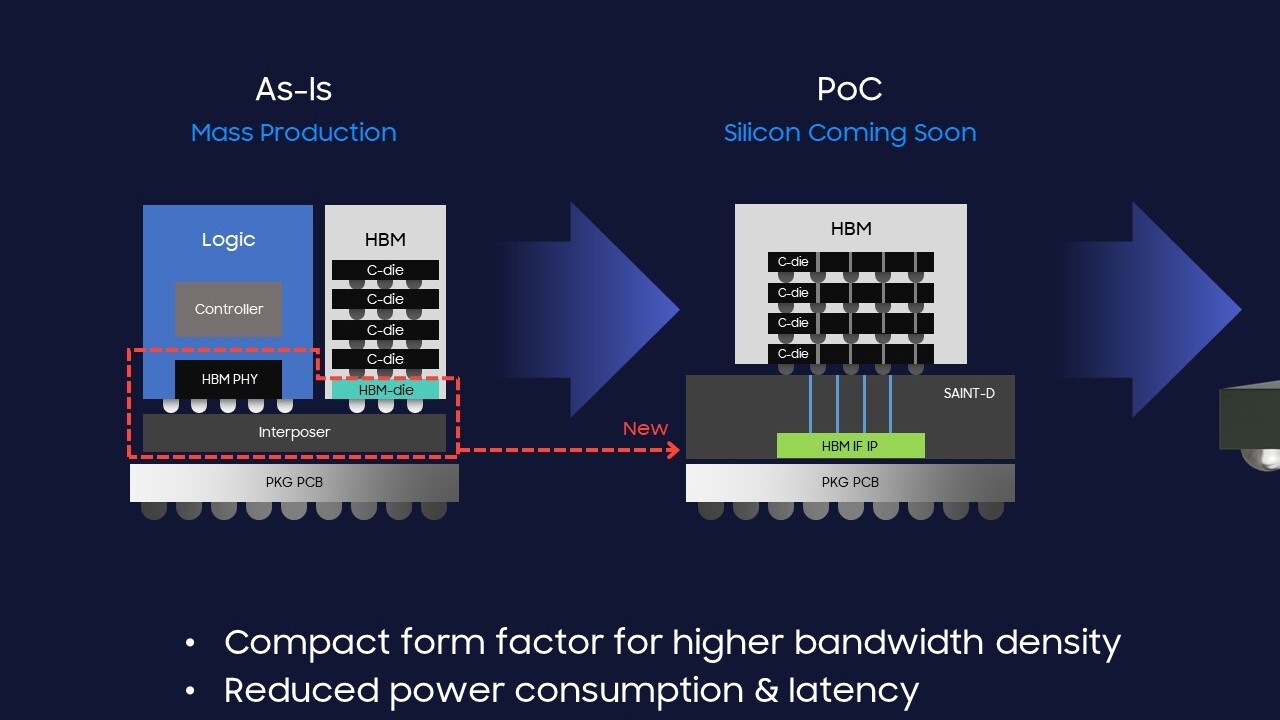

An irgendeiner Stelle scheint es letztlich immer zu haken. Nvidias Chef Jensen Huang hatte zuletzt bereits erklärt, dass die AI-Beschleuniger bis ins kommenden Jahr 2025 knapp bleiben – Packaging bei TSMC sei das Nadelöhr. Mitbewerber Samsung versucht aus dieser Lage ebenfalls einen Nutzen zu ziehen. Auf dem Foundry Forum erklärten die Südkoreaner zuletzt, dass sie doch die einzigen sind, bei denen alles aus einer Fab kommen kann, also HBM und auch eigene Interposer. Dies könnte in Zukunft eine Option für bestimmte Produkte sein, aktuell ist es sie aber noch nicht. Samsung arbeitet darüber hinaus auch an Nachfolgeideen, auch hier sind am Ende aber stets multiple Chips im Einsatz und müssen so ebenfalls erst einmal gefertigt werden.