Fertigungstechnologie: Intel 3 macht großen Sprung gegenüber Intel 4

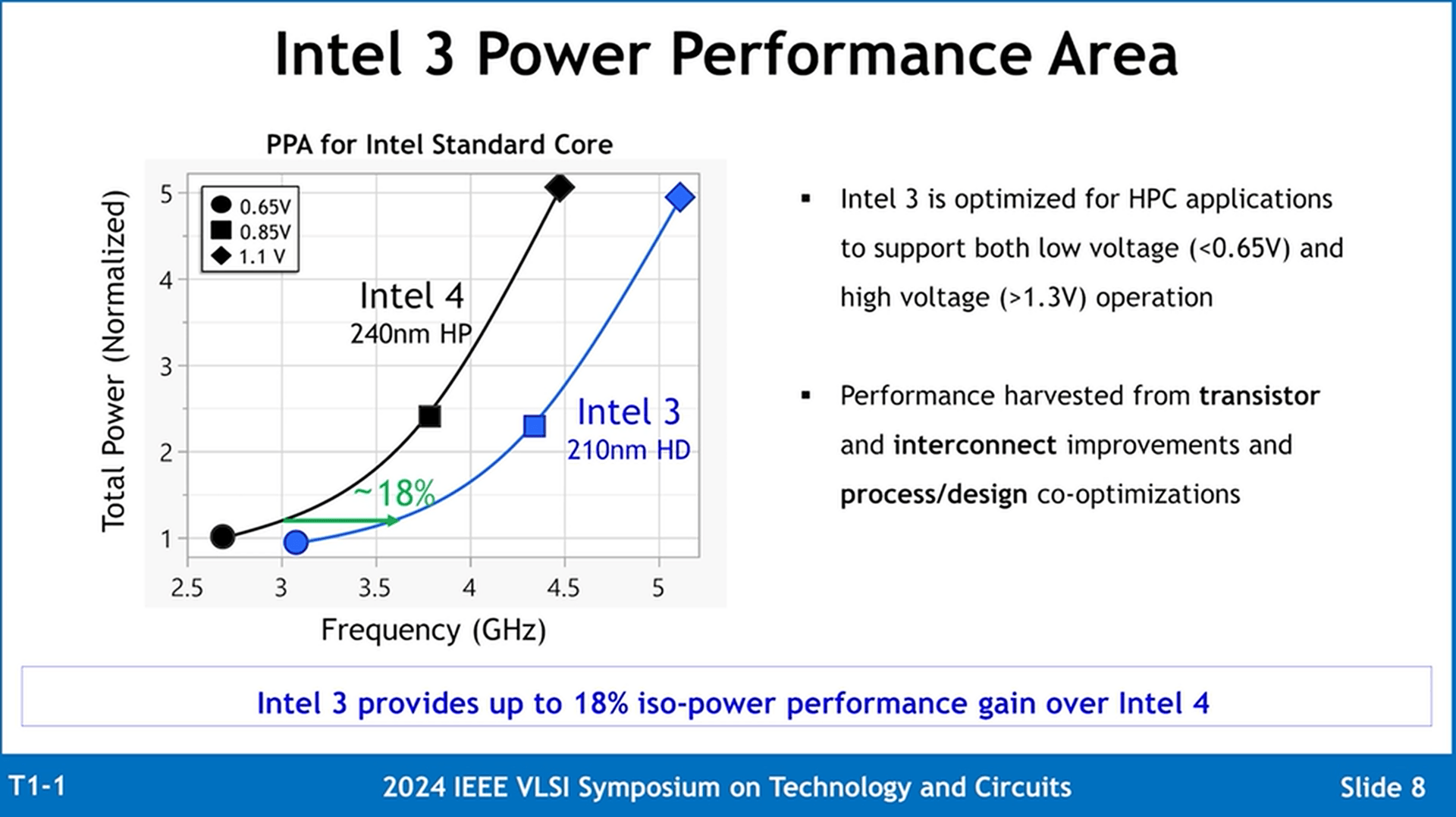

Auf die Fertigungsstufe Intel 4 folgt Intel 3, das ist schon lange klar. Dass dabei jedoch ziemlich viel passiert, zeigt Intel erst heute im Rahmen des VLSI mal auf der großen Bühne. Möglich werden durch viele Anpassungen nun nämlich 18 Prozent mehr Leistung bei gleicher Leistungsaufnahme wie mit Intel 4.

Am heutigen Tag stellt Intel beim VLSI Symposium auf Hawaii zu dieser Stunde unter dem Titel „An Intel 3 Advanced FinFET Platform Technology for High Performance Computing and SOC Product Applications“ die aktuellen Errungenschaften des gerade eingeführten Fertigungsprozesses dar. Intel 3 ist dabei nicht nur ein etwas optimierter Ableger von Intel 4, mit dem das Unternehmen die EUV-Belichtung einführte. Intel 3 soll als ultimativer FinFET-Fertigungsprozess, sprich in dem Fall als letzter seiner Art, auch die Grundlage für das Packaging und damit Foveros und EMIB sein und wird deshalb für viele Jahre Relevanz behalten. Parallel zum Event gibt es bei Intel auch einen umfangreichen Community-Blogpost inklusive 16 Minuten langem Video.

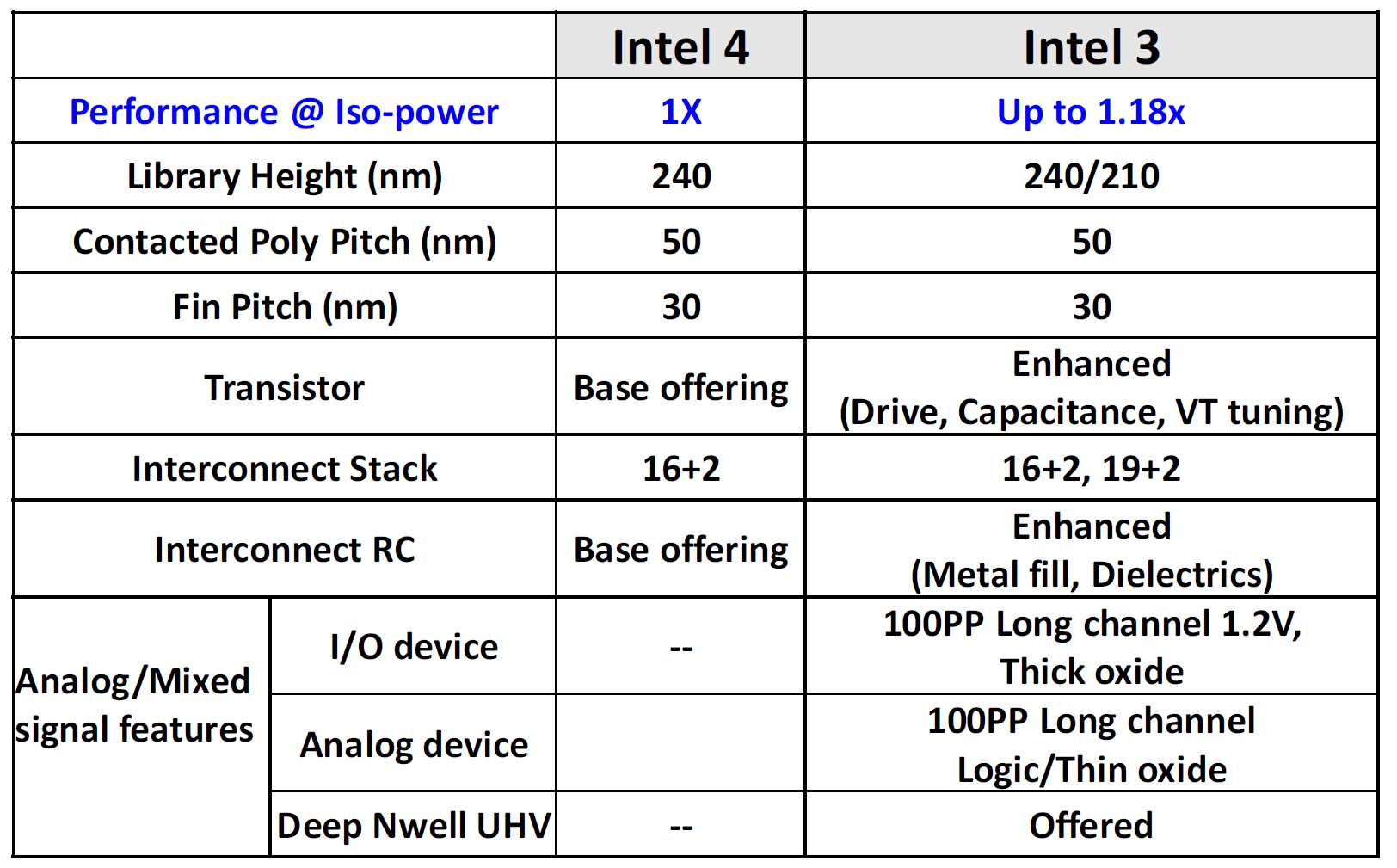

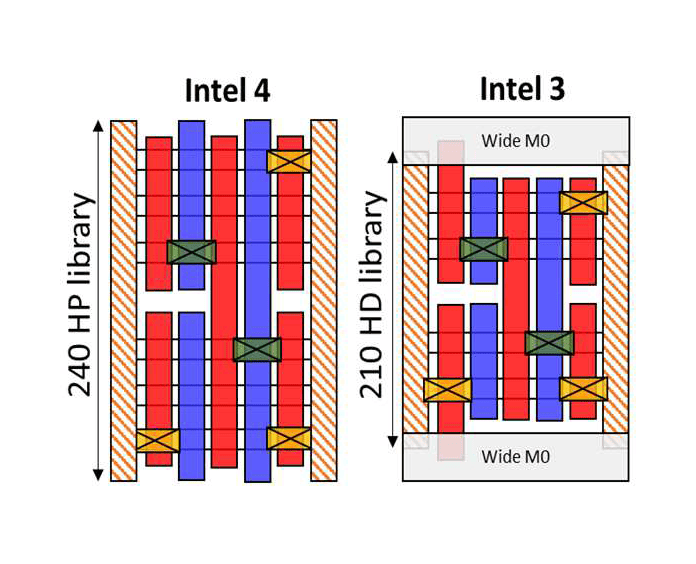

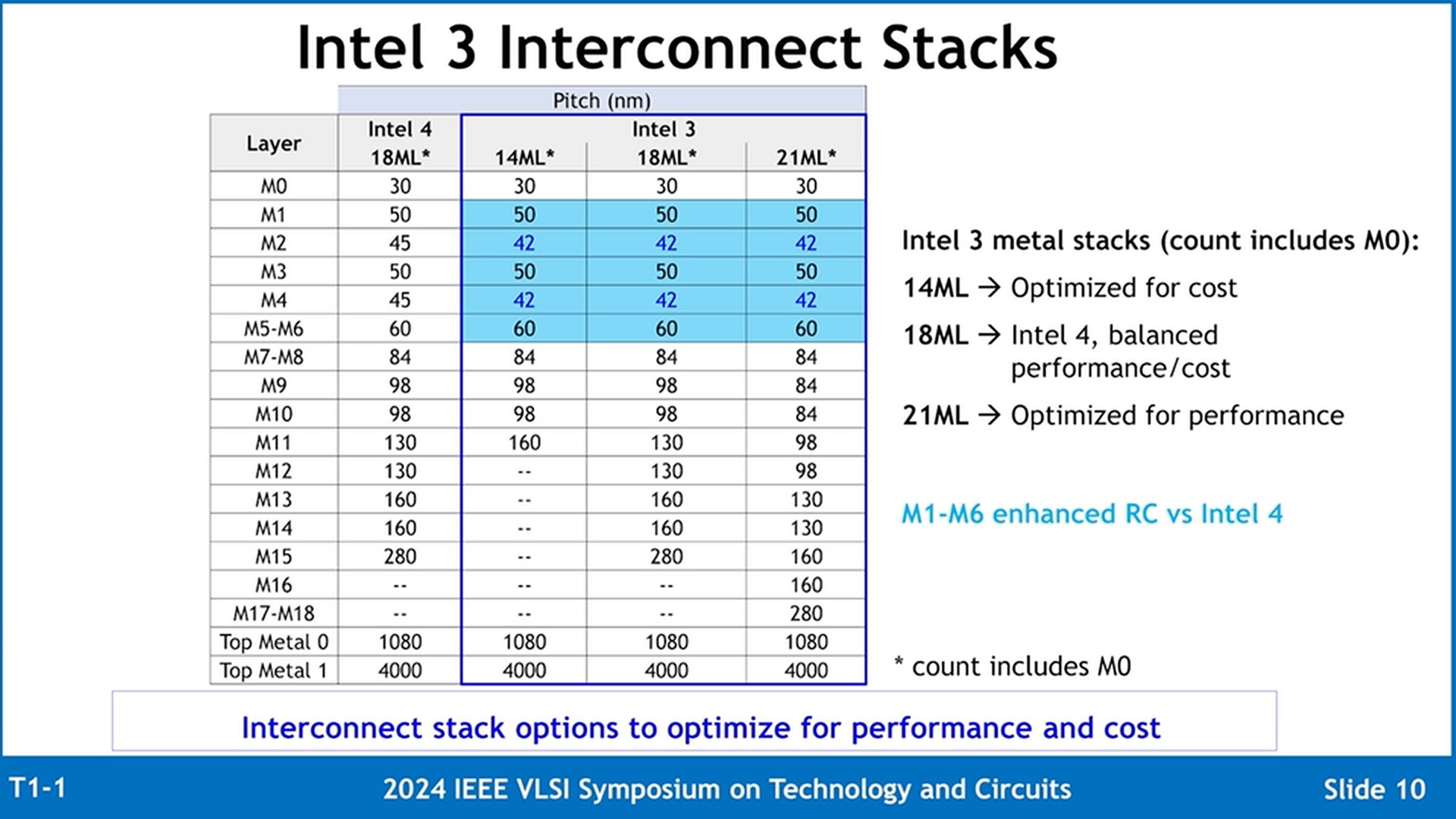

Ganz offiziell ist Intel 3, 3-T, 3-E und 3PT eine stark optimierte und gleichzeitig abwärtskompatible Verbesserung von Intel 4, so wie es bisher nur beim CPU-Tile von Intel Meteor Lake genutzt wird. Das Logic Scaling liegt dabei nur bei zehn Prozent, weil Intel viele Dinge wie Gate, Fin-Pitch und M0-Metal-Pitch von Intel 4 beibehält, aber diverse andere Baustellen angeht: An die bisherige High-Performance-Library schließt nun eine High-Density-Variante an, die parallel angeboten wird und so für möglichst effiziente Produkte genutzt werden kann – Stichwort Sierra Forest. Neu ist nun auch ein nochmal vergrößerter Meta-Layer-Stack, der zusammen mit vielen anderen Dingen zum Leistungsgewinn beiträgt.

Isopower

performance improvements are achieved through

improved short channel effects (SCE), higher transistor drive

at a given leakage, lower contact capacitance, reduced

interconnect RC (intrinsic and design-enabled), and additional

metal layers for improved routing.

Intel

Bis zu 18 Prozent mehr Leistung bei gleicher Leistungsaufnahme entsprechen zum Vergleich mit dem Wettbewerb bei TSMC dem Sprung von seinerzeit N5 auf N3, der mit bis zu 15 Prozent mehr Leistung angegeben wurde. Dafür war das Logic Scaling, wie es bei einem Full-Node-Shrink üblich ist, deutlich größer. Im zweiten Halbjahr dieses Jahres folgt TSMCs N3E und steigert die Leistung nochmals um rund fünf Prozent.

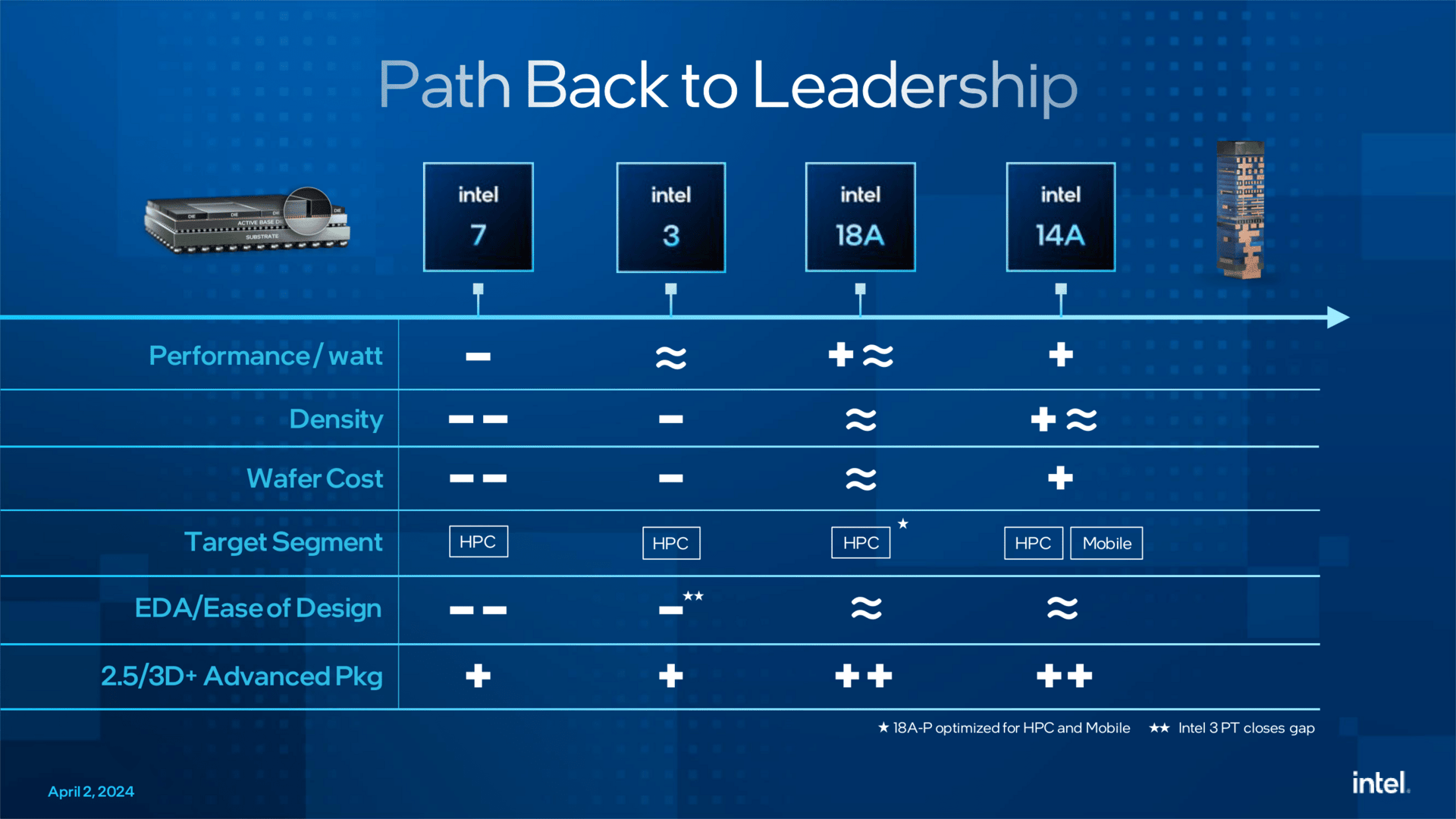

TSMC liegt mit N3/N3E nach wie vor deutlich vorn – sagt sogar Intel – dafür legt Intel ab Ende dieses Jahres dann die ersten GAA-Prozesse auf. Intels eigene Prognose hat ab Intel 18A im kommenden Jahr ein ungefähres Gleichgewicht zu TSMC im Blick, traditionell ist es für den Herausforderer aber nötig, besser zu sein als der Platzhirsch, wenn man Kunden gewinnen will. Anders gesagt: Vor Intel 18A dürften sich kaum Kunden zu Intel Foundry verirren, großspurigen Präsentationen müssten Taten folgen.

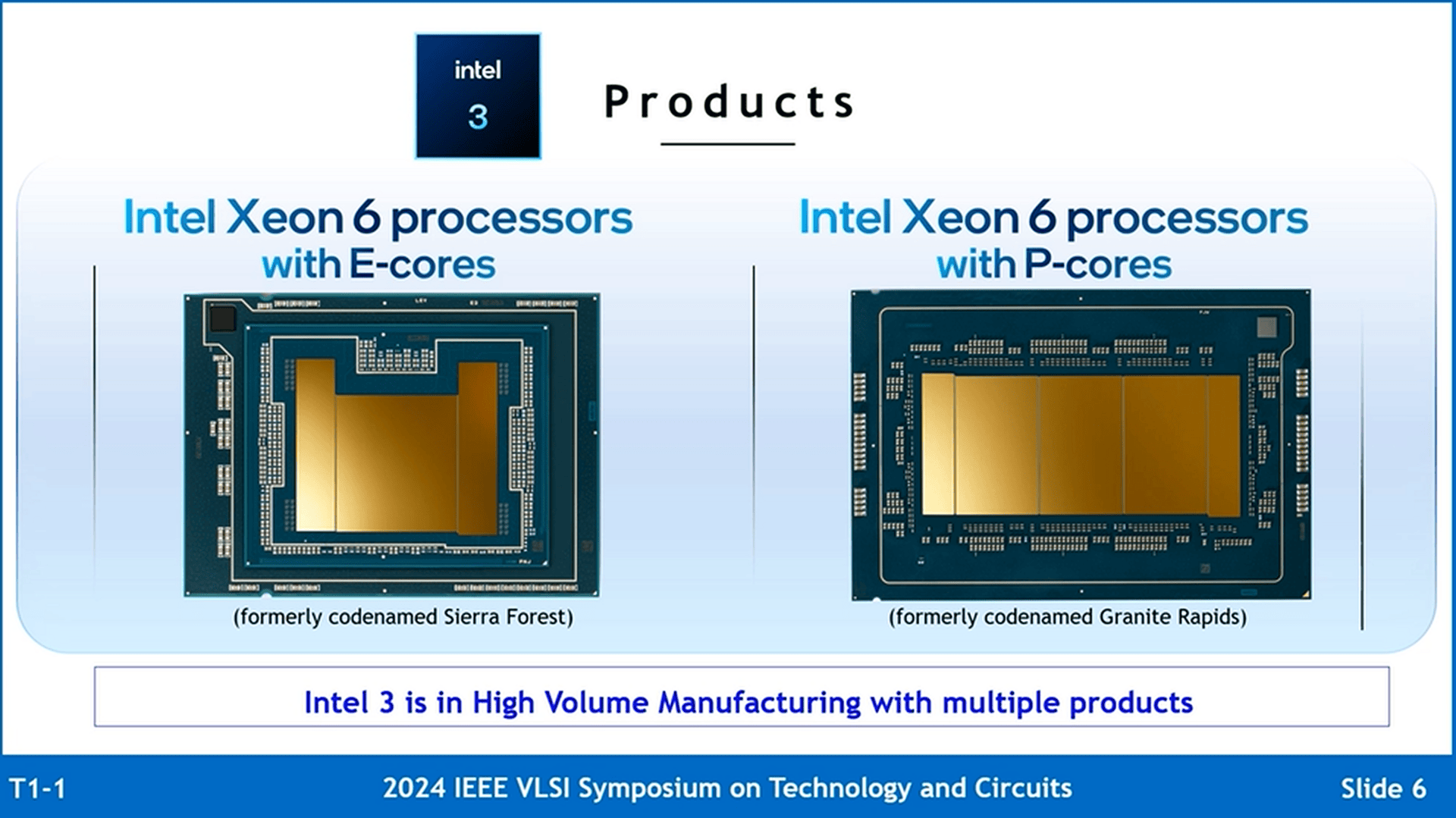

Die Intel-3-Produkte Sierra Forest und Granite Rapids dürfen im zweiten Halbjahr dann schonmal zeigen, ob dort etwas dran ist. In den Vorabtests von Intel Sierra Forest gab es erste positive Stimmen hinsichtlich der Effizienz.

ComputerBase hat Informationen zu dieser Meldung zum Teil vorab von Intel unter NDA erhalten. Die einzige Vorgabe war der frühestmögliche Veröffentlichungszeitpunkt.