JEDEC: Spezifikationen von HBM4 rücken näher

Die für Speicherstandards zuständige Organisation JEDEC hat mitgeteilt, dass sich die Finalisierung des HBM4-Standards nähert. Die kommende Generation des High Bandwidth Memory soll nochmals schneller werden, mehr Speicherkapazität bieten und zudem weniger Strom benötigen.

Einen Zeitrahmen für das Erscheinen der fertigen Spezifikationen von HBM4 hat die JEDEC aber noch nicht genannt. Allzu eilig ist es auch nicht, denn Hersteller rechnen frühestens im zweiten Halbjahr 2025 mit dem Start der Produktion. Allgemein gilt eine Verfügbarkeit im Jahr 2026 derzeit als wahrscheinlich, sofern die bisherigen Pläne nicht doch noch beschleunigt werden.

HBM4 verdoppelt Interface auf 2.048 Bit

HBM4 soll gegenüber HBM3 doppelt so viele Speicherkanäle aufweisen, statt deren 16 wären es also deren 32. Das Interface ist mit 2.048 Bit doppelt so breit. Pro Pin wird eine Datenrate von zunächst 6,4 Gbit/s anvisiert. Das ist zwar genauso viel wie bei HBM3, doch durch das schnellere Interface würde der Durchsatz effektiv auf rund 1,6 TB/s pro Stapel verdoppelt werden. Das ist auch schneller als die rund 1,2 TB/s bei HBM3E (1.024 Bit, 9,6 Gbit/s).

| Interface | max. Durchsatz pro Pin | max. Durchsatz pro Stack | |

|---|---|---|---|

| HBM1 (JEDEC) | 1.024 Bit | 1,0 Gb/s | 128 GB/s |

| HBM2 (JEDEC) | 2,0 Gb/s | 256 GB/s | |

| HBM2E | 3,6 Gb/s | 461 GB/s | |

| HBM3 (JEDEC) | 6,4 Gb/s | 819 GB/s | |

| HBM3E (Micron) | 9,2 Gb/s | 1.178 GB/s | |

| HBM3E (Samsung) | 9,8 Gb/s | 1.254 GB/s | |

| HBM3E (SK Hynix) | 10,0 Gb/s | 1.280 GB/s | |

| HBM4 (JEDEC) | 2.048 Bit | 6,4 Gb/s | 1.638 GB/s |

| HBM4E | ? | 2.000+ GB/s |

Bei HBM4 sollen 4, 8, 12 oder 16 Lagen DRAM übereinander gestapelt werden. Bei 24-Gbit-Dies (3 GByte) ergeben sich so bis zu 48 GByte pro Stapel. Bei den neuen 32-Gbit-Dies (4 GByte) sind es dann bis zu 64 GByte pro Stack.

Hersteller planen mit 2025 oder 2026 für HBM4

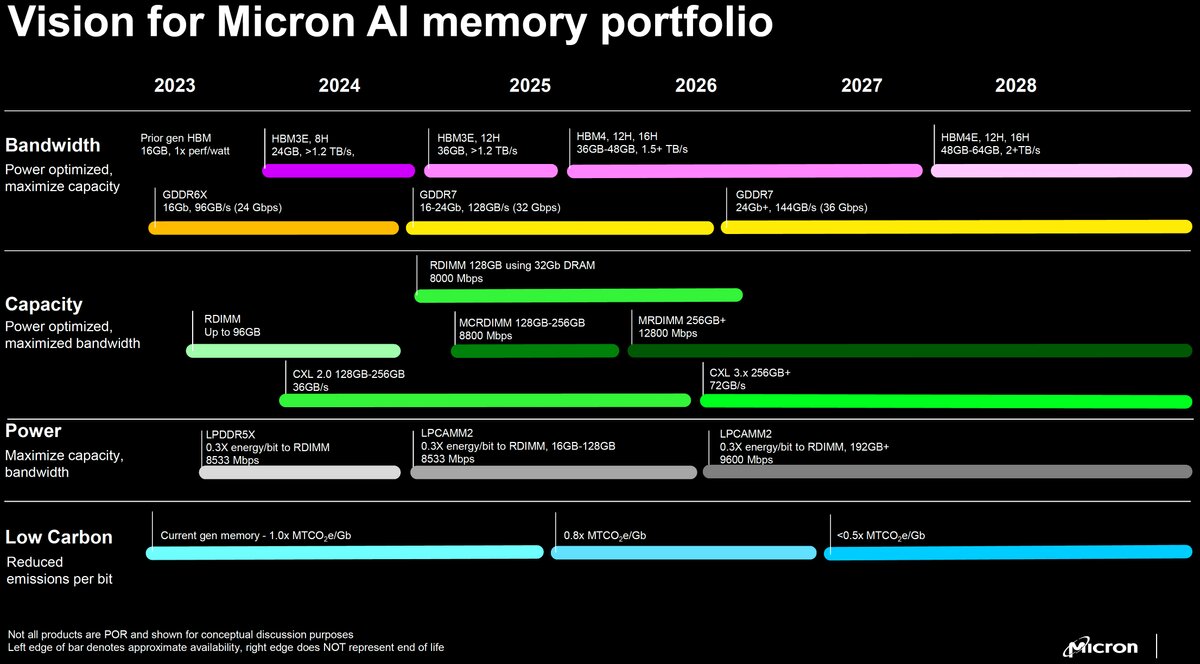

Micron hat HBM4 mit 36 GB (8H) oder 48 GB (12H) und „1,5+ TB/s“ schon auf einer Roadmap stehen, die den Produktionsstart im zweiten Halbjahr 2025 vermuten lässt.

Auch Samsung plant mit 2025, während es bei SK Hynix zuletzt 2026 geheißen hatte.

Nvidia als potenzieller Abnehmer hat HBM4 ebenfalls für 2026 auf dem Zettel, denn dann soll die Data-Center-GPU Rubin als Blackwell-Nachfolger mit HBM4 erscheinen.