Stacking wie Ryzen X3D: Apple M5 könnte auch gestapelt erscheinen

Apple soll beim kommenden M5-Chip auf TSMCs SoIC-X-Verfahren zum Stapeln von Dies setzen, so wie es beim Ryzen X3D bisher genutzt wird. Die große Frage und Unbekannte in den Gerüchten dabei ist jedoch: Was stapelt Apple dann übereinander?

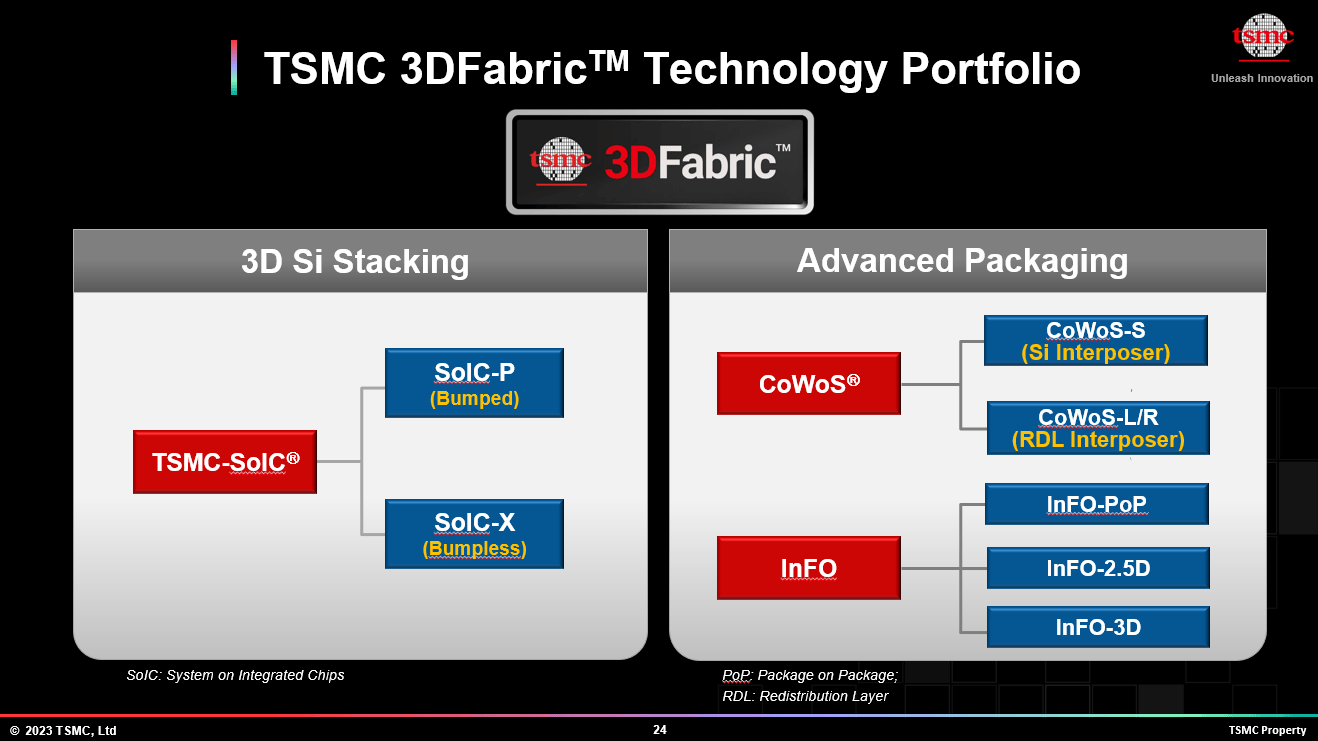

SoIC ist ein starkes Zugpferd von TSMC, es soll in den nächsten Jahren aber noch weiter wachsen. Im Frühjahr erklärte das Unternehmen, dass die Lösung für das Stacking, wie es beispielsweise beim 3D-Cache der Ryzen-X3D-CPUs genutzt wird, mit geplanten 30 Tapeouts bis zum Jahr 2026 zwar auf deutlich kleinerer Flamme kocht als beispielsweise CoWoS (Chip-on-Wafer-on-Substrate), aber auch in dem Bereich an Fahrt gewinnt. Beim Kapazitätsausbau wird es entsprechend berücksichtigt.

Dass Apple irgendwann in diese Technologie einschwenkt, überrascht letztlich nicht. Das Verfahren ist mittlerweile einige Jahre lang erprobt und wird stetig verbessert, neue Fertigungsstufen sollen in Kürze schneller übereinander gestapelt werden können, als es bisher der Fall war. Apple-Chips werden zudem stetig größer und nehmen viel Fläche in Anspruch, in die Höhe zu gehen, um zusätzliche Möglichkeiten zu bieten, wäre eine entsprechende Option. Die Gerüchte melden nun, dass Apple für einen M5-Chip (Pro, Ultra, Max werden als Möglichkeit genannt), der für den Cloud-Einsatz und AI-Funktionalität gedacht ist, auf einem Basis-Chip aus der N2-Fertigung, welcher im Grunde die CPU darstellt, einen weiteren stapelt, eventuell eine GPU. Entsprechend durchkontaktiert halten beide die Kommunikation zueinander aufrecht.

Noch ist vieles unklar

Was letztlich genau übereinander gestapelt wird und in welcher Fertigungsstufe, bleibt aber ein vages Gerücht. Sollte TSMCs N2-Technologie wirklich die Basis sein, ist schon deshalb nicht vor Ende 2025 damit zu rechnen. TSMC hatte zuletzt in Aussicht gestellt, dass sich die Technologie für den Basis-Chip und den darauf gestapelten in Zukunft weiter annähern wird, bisher liegt im Schnitt ein Node dazwischen. Auch erschien das Stacking bestimmter Chips bisher deutlich später als die Basistechnologie, es braucht schlichtweg zusätzlich Entwicklungszeit, diese Features ohne Probleme für die Massenproduktion parat zu haben. Ein zusammengefasst suggerierter N2+N3-Chip dürfte jedoch realistisch gesehen eher ein Produkt des Jahres 2026 sein.