IBM Telum II: 8 Kerne, DPU und 360 MB L2-Cache erschaffen Monster-Chip

IBM nutzt Samsungs 5-nm-Fertigung für einen großen Mainframe-Chip, der keine Konkurrenz fürchten muss – denn er hat quasi keine. Auf Basis des vor drei Jahren an gleicher Stelle enthülltem Telum entsteht die zweite Generation mit noch mehr Cache, Takt und Leistung.

Mehr und mehr Cache

IBMs zweiter Telum-Chip ist erneut ein interessantes Konstrukt. So scheinen sich die Konstrukteure für den neuen Mainframe-Chip, also ein Produkt für Großrechner, des Unternehmens gefragt zu haben, was bei wenig Cache im Chip hilft, die Antwort war klar: mehr Cache. Aber wenn nun davon schon eine schiere Menge vorhanden ist, heißt es nicht, dass man diese nicht dennoch weiter ausbauen kann. Und genau das hat IBM getan. Und wenn beim Blick auf den 43 Milliarden Transistoren fassenden und 600 mm² großen Chip aus Samsungs 5HPP-Fertigung gefühlt mindestens 40 Prozent Cache sind, dann wird erst so richtig klar, wie groß der Cache eigentlich wirklich ist.

Zehn Slices, jeder davon fasst 36 MByte, markieren zusammen einen 360 MByte großen L2-Cache. Das sind 40 Prozent mehr als beim Vorgänger, seinerzeit waren es 8 × 32 MB. Damit wachsen auch die virtuellen Caches in der dritten und vierten Ebene an, da sie die Basis des L2-Caches nutzen. Der riesige L2-Cache ist allerdings nicht nur L2-Cache, sondern auch ein virtueller L3-Cache – diesen Ansatz gab es seit Telum. Das Resultat: Die auf die Prozessoren abgestimmte Software sieht den Cache als physikalisch vorhandenen und über alle Kerne geteilten L3-Cache, wenn sie den Prozessor anspricht. Das System geht mit einer vierten Cache-Ebene weiter. Der virtuelle L3-Cache ist nun 360 MByte groß, mit dem Faktor 8 davon ergibt sich der virtuelle L4-Cache: 2,88 GByte groß ist dieser letztlich.

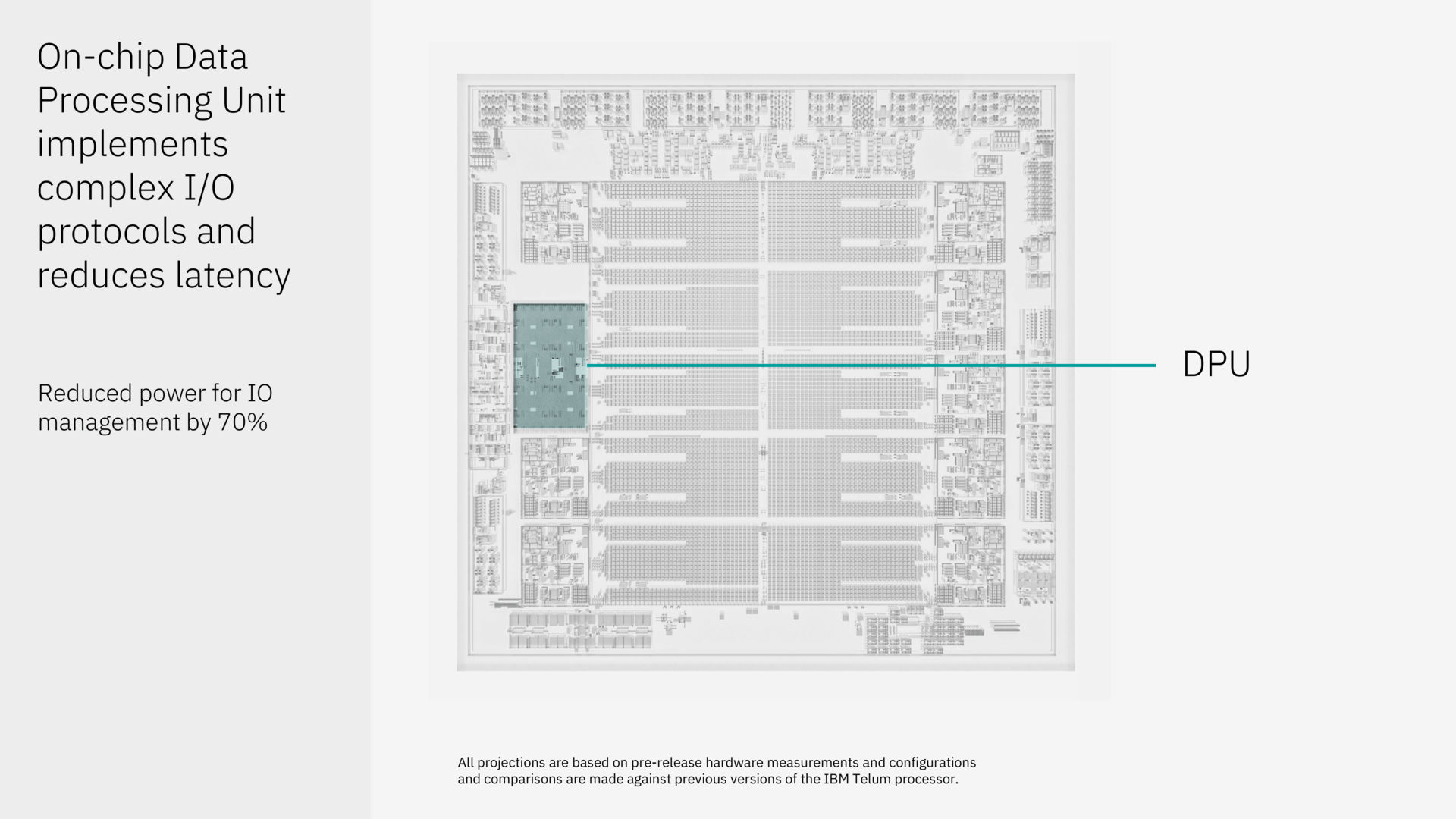

Die eigentlichen CPU-Kerne sind im Vergleich dazu winzig: Es sind acht an der Zahl, sie arbeiten mit 5,5 GHz – immer und überall, garantiert. Sie wurden leicht überarbeitet und ihre IPC gesteigert. Diese Kerne nutzen jeweils einen L2-Cache-Slice im private Modus, auch die neue integrierte eigens entwickelte DPU (Data Processing Unit) für I/O-Beschleunigung nutzt einen weiteren. Der zehnte L2-Cache-Block wird geteilt genutzt. Auch ein aufgewerteter integrierter AI-Beschleuniger mit 24 TOPs ist dabei, er wird bei Kreditkartenfirmen unter anderem zur Betrugserkennung genutzt.

Bis zu 32 Telum II lassen sich in einem System verbauen. Mit 12 I/O Expandern, die jeweils 16 PCIe Slots bieten können, werden 192 PCIe-Karten im Gesamtsystem möglich. Genau dafür wurde die DPU entwickelt, um mit dieser riesigen Skalierung ohne große Probleme hantieren zu können. Und die Mainframe-Kunden wollen genau das, erklärt IBM.

Eine Stunde Ausfall in 11.400 Jahren

IBM hat mit den Mainframe-Chips, die in Systemen der z-Serie verbaut sind, einen Stand im Markt, der seinesgleichen sucht. Milliarden an Dollar werden jede Sekunde über Mainframes von IBM abgewickelt, denn beispielsweise nahezu alle großen Kreditkartenfirmen setzen auf diese Lösungen, 70 Prozent aller finanziellen Transaktionen weltweit. Was diese Unternehmen brauchen, ist eine garantierte Verfügbarkeit. IBM gibt keine 100 Prozent an, aber 99,999999 % – 100% gibt es bekanntlich nicht, wenngleich das „z“ in der z-Serie für „zero downtime“ steht. Das entspricht umgerechnet einer Stunde Ausfallzeit in 11.400 Jahren, rechnet IBM vor.

Zusätzlicher AI-Beschleuniger Spyre

Um Telum II in Richtung AI zu ergänzen, präsentiert IBM auch eine Beschleunigerkarte, Spyre getauft. Denn der AI-Beschleuniger in Telum ist manchmal zu klein, manchmal aber auch schon zu groß, um den ganzen Prozessor dazu nutzen zu müssen. Spyre soll diese Lücken schließen.

Die Fertigung übernimmt auch hier Samsung, mit 5LPE kommt quasi ein Smartphone-SoC-Fertigungsprozess zum Einsatz, der entsprechend Effizienz höher stellt. Auf einer 75-Watt-PCIe-Karte wird der 300 mm² große Spyre über 300 TOPS an Leistung bieten. LPDDR5 in einer Größe von 128 GByte stehen als Speicher zur Seite – HBM war aufgrund von zu hoher Leistungsaufnahme nicht im Rennen, erklärte IBM auf Nachfrage. Zusammen mit der Skalierbarkeit von Telum II im I/O-Bereich, sollen sich leicht große Cluster bilden lassen.

Aktuell baut IBM ein Testsystem mit 96 Spyre-Karten, welches 30 Peta-Ops Leistung in einem System bieten soll. Telum II als auch Spyre sollen im Laufe des Jahres 2025 dann verfügbar werden.

- IBM Telum II: 8 Kerne, DPU und 360 MB L2-Cache erschaffen Monster-Chip

- Intel Granite Rapids-D: Xeon 6 SoC mit zwei 44-Kern-Tiles plus I/O bildet neue Xeon D

- Nvidia & Supermicro: Wie (AI-)Rechenzentren einen kühlen Kopf bewahren

- +2 weitere News