SK Hynix: 3D DRAM soll Kosten der EUV-Fertigung halbieren

Inzwischen sind alle DRAM-Hersteller bei der Fertigung mit EUV-Lithografie angekommen. Diese ist allerdings kostspielig. Abhelfen soll der kommende 3D DRAM, mit dem sich die Kosten der EUV-Prozesse angeblich halbieren lassen, so ein Wissenschaftler von SK Hynix.

Dies soll der Forscher Seo Jae Wook von SK Hynix am Montag im Rahmen einer Konferenz geäußert haben, berichtet The Elec aus Südkorea. Die Kosten der EUV-Herstellungsprozesse sollen spätestens mit der 6. Generation DRAM der 10-nm-Klasse, die auch 1c DRAM genannt wird, schnell steigen. Sowohl SK Hynix als auch Samsung wollen mit der 1c-Fertigung im späteren Jahresverlauf beginnen.

SK Hynix’s Seo said with VG or 3D DRAM, the process can be designed to reduce the cost of EUV processes by half.

The Elec

3D DRAM mit „Layern“ ähnlich wie beim 3D-NAND

Beim 3D DRAM werden die Transistoren vertikal übereinander gestapelt, sodass mehrere Speicherebenen entstehen, ähnlich wie es beim 3D-NAND der Fall ist. Durch die Flucht in die Höhe können mehr Bit auf gleicher Fläche untergebracht werden oder eben die Speicherchips bei gleicher Kapazität kleiner ausfallen. Der 3D DRAM im sogenannten 4F2-Layout soll so eine etwa 30 Prozent kleinere Chipfläche als herkömmlicher 6F2-DRAM besitzen.

Sowohl SK Hynix als auch Samsung erwägen einen Wechsel zur 3D-DRAM-Fertigung für die nähere Zukunft. Samsung rechnet nach öffentlichen Aussagen mit dem Jahr 2030 für einen kommerziellen Start und will 16 Ebenen (Layer) übereinander stapeln. Laut Berichten aus Südkorea soll Micron vorerst mit nur 8 Ebenen planen.

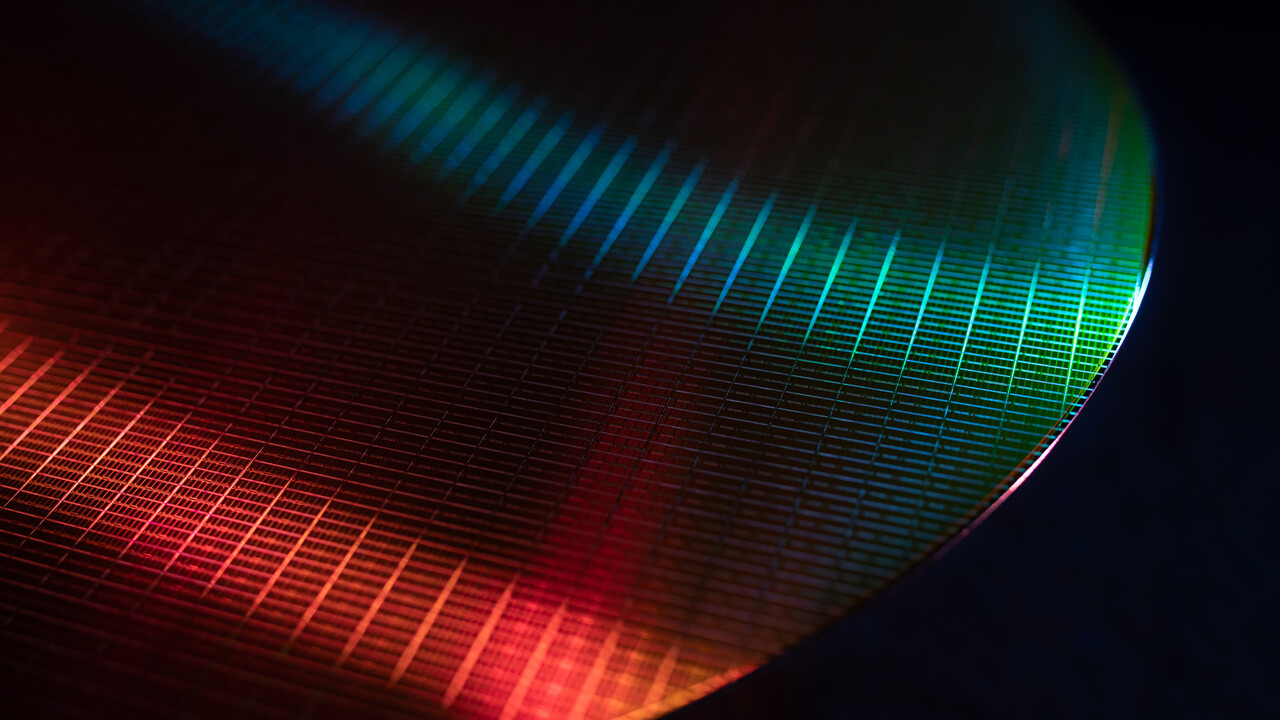

Mehrere Wafer werden vereint

Laut Samsung sind für 3D DRAM unter anderem neue Materialien nötig. Zusätzlich soll das sogenannte Waferbonden zum Einsatz kommen, mit dem zwei Wafer vollflächig miteinander verbunden werden. Dieses Verfahren wird mittlerweile auch bei manchem 3D-NAND genutzt.

Ein großer Umbruch steht bevor

Im Bereich des DRAM, der nicht nur die Basis für klassischen Arbeitsspeicher wie DDR5-Module, sondern etwa auch den High Bandwidth Memory (HBM) bildet, gilt das neue 3D-Design als radikaler Umbruch in der Herstellung, der aber aus Kostengründen wie auch technischen Limits des bisherigen 2D-Designs alsbald nötig wird.