- Registriert

- Juni 2007

- Beiträge

- 8.752

Hallo zusammen!

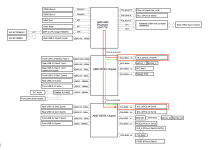

Mich würde mal interessieren, wie genau bei X870E die Daten von einem M2-Slot zum anderen fließen, z.B. M.2_2 ←→ M.2_3:

Läuft das immer über die CPU oder direkt zwischen M.2_2 und M.2_3 ? Oder anders gefragt, wenn ich Daten von einer SSD in M.2_2 auf eine SSD in M.2_3 schiebe, stünde die volle PCIe 4.0 x4 Übertragungsrate zur Verfügung oder nur die Hälfte davon (wegen Umweg über die CPU)?

lg autoshot

Mich würde mal interessieren, wie genau bei X870E die Daten von einem M2-Slot zum anderen fließen, z.B. M.2_2 ←→ M.2_3:

Läuft das immer über die CPU oder direkt zwischen M.2_2 und M.2_3 ? Oder anders gefragt, wenn ich Daten von einer SSD in M.2_2 auf eine SSD in M.2_3 schiebe, stünde die volle PCIe 4.0 x4 Übertragungsrate zur Verfügung oder nur die Hälfte davon (wegen Umweg über die CPU)?

lg autoshot