Piak schrieb:

Für mich liest sich das immer noch deutlich schlechter als die amd chiplets mit Zen 4C oder 5C kernen ...

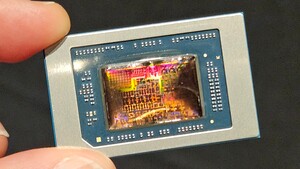

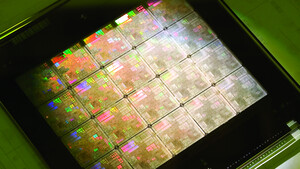

Das Packaging ist schon besser als bei AMD, dadurch dass die Chiplets näher aneinander positioniert sind und anders verbunden sind, ist der Datentransfer von Chiplet zu Chiplet deutlich energiesparender möglich. Damit bleibt mehr Budget für die Kerne übrig. Wie der Vergleich von Kern zu Kern ausfällt, ist natürlich noch eine offene Frage, aber auf jeden Fall kann man jetzt schon sagen, dass bei Intel ein größerer Anteil der TDP für die Kerne und weniger für IO benötigt wird als bei Zen 4/5(c). Selbst leicht schlechtere Kerne könnten da immer noch Intel zum effizienteren Gesamt-Chip verhelfen.

Gleichzeitig ist aufwendigeres Packaging natürlich auch teurer, da hat AMD wiederum Vorteile bei den Produktionskosten. Die Frage für den Markt wird also sein, ob Intel das teurere Produkt produzieren muss, um mit Zen 5c gleichzuziehen, oder ob die Cores gut genug sind, um davonziehen zu können und den Aufpreis (auch für den Kunden) zu rechtfertigen.

Andererseits kann man es aber auch so sehen: Intel kündigt jetzt etwas an, was AMD als MI300 bereits erfolgreich im Markt positioniert hat. Das ist zwar eine APU mit integriertem HBM, aber der Technologiestand ist dann durchaus vergleichbar mit Base-Die mit Cache, aufgestapelten CCD etc.

EDIT: Vergessen zu erwähnen, natürlich sind Backside Power Delivery etc schon Technologien, die AMD derzeit (nicht) hat, ich hab jetzt nur den Punkt Packaging betrachtet.