- Registriert

- Juni 2001

- Beiträge

- 19.017

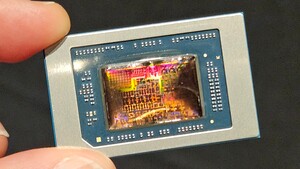

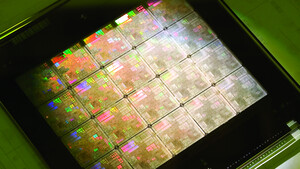

Intels Server-Prozessoren der Baureihe Xeon D waren bereits stark, in der nächsten Generation gehen sie aber auf das nächste Level: 2 × 44 Redwood-Cove-Kerne auf kleinstem Raum. Dafür nutzt das Xeon 6 SoC die Basis von Granite Rapids mit multiplen Tiles, packt dazu aber einen neuen I/O-Die, was dem Einsatzgebiet geschuldet ist.

Zur News: Intel Granite Rapids-D: Xeon 6 SoC mit zwei 44-Kern-Tiles plus I/O bildet neue Xeon D

Zur News: Intel Granite Rapids-D: Xeon 6 SoC mit zwei 44-Kern-Tiles plus I/O bildet neue Xeon D