3D DRAM: Kioxia verrät etwas mehr über den sparsamen OCTRAM

Wie zuvor angekündigt, hat Kioxia auf dem diesjährigen IEEE International Electron Devices Meeting (IEDM) über eine neue Speichertechnologie gesprochen. Gemeint ist der sogenannte Oxide-Semiconductor Channel Transistor DRAM (OCTRAM), dessen Herzstück ein vertikaler Transistor ist.

DRAM bei Kioxia gab es lange nicht

Dass Kioxia (früher Toshiba Memory) überhaupt an einem DRAM-Produkt arbeitet, ist schon an sich eine Neuheit, denn zum Kreise der DRAM-Hersteller gehört das Unternehmen bereits seit über 20 Jahren nicht mehr.

Eine Rückkehr ist aber möglich. Zumindest wird an einem neuartigen DRAM-Produkt geforscht und das nicht im Alleingang, sondern zusammen mit dem eher kleinen DRAM-Hersteller Nanya.

3D DRAM mit vertikalem Transistor

Beide arbeiten, wie schon Ende Oktober verkündet wurde, am sogenannten Oxide-Semiconductor Channel Transistor DRAM oder abgekürzt OCTRAM.

Das Herzstück ist ein vertikaler Transistor (Stichwort 3D DRAM), der dank eines Oxidhalbleiters besonders wenig Energie benötigen soll. Konkret haben die Forscher nach eigenen Angaben ein funktionsfähiges OCTRAM Array mit 275 Mbit (~34 MByte) hergestellt.

Neue Details zum OCTRAM

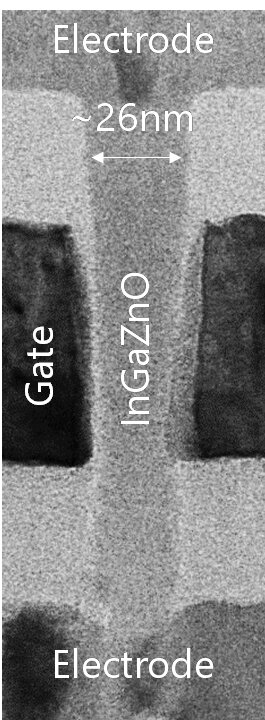

Zum kürzlich abgehaltenen IEDM 2024 wurden weitere Details veröffentlicht, die eine Pressemitteilung knapp zusammenfasst. Der OCTRAM verwendet demnach einen „zylinderförmigen vertikalen InGaZnO-Transistor als Zellentransistor“. Die Abkürzung InGaZnO steht für eine Verbindung aus Indium (In), Gallium (Ga), Zink (Zn) und Sauerstoff (O). Durch eine „Optimierung von Bauteil und Prozess“ erreiche dieser Transistor einen besonders hohen Strom im eingeschalteten Zustand und einen besonders niedrigen Strom im ausgeschalteten Zustand. Letzteres soll „einen DRAM mit niedrigem Stromverbrauch realisieren“, heißt es.

Ferner soll das vertikale Transistor-Design vor allem die Speicherdichte weiter erhöhen. Ein Punkt, der bei „2D“-DRAM immer schwieriger respektive teurer geworden ist. Der neue „3D“-DRAM besitzt ein quadratisches 4F²-Layout statt des bisher üblichen 6F²-Designs.

Auch Micron, Samsung und SK Hynix arbeiten am 3D DRAM

Samsung und SK Hynix arbeiten ihrerseits an 3D DRAM, der die Kosten der teuren EUV-Fertigung im besten Fall halbieren soll. Auch Micron forscht an 3D DRAM mit mehreren Ebenen von Speicherzellen.