3D X-DRAM: Speicherkonzept will 16-mal mehr als 2D-DRAM speichern

Die Firma NEO Semiconductor ist durch interessante Speicherkonzepte wie den X-NAND oder den X-DRAM bekannt geworden. Beim X-DRAM mit 3D-Aufbau geht es nun weiter. Neuerdings soll dieser sogar 512 Gbit speichern. Herkömmlicher DRAM ist bisher erst bei 32 Gbit angekommen.

3D X-DRAM mit bis zu 512 Gbit

Bereits 2023 hatte NEO Semiconductor das Konzept des 3D X-DRAM vorgestellt. Dieser sollte durch einen ähnlichen Aufbau wie bei 3D-NAND eine Speicherkapazität pro Chip von 128 Gigabit (16 GByte) erreichen.

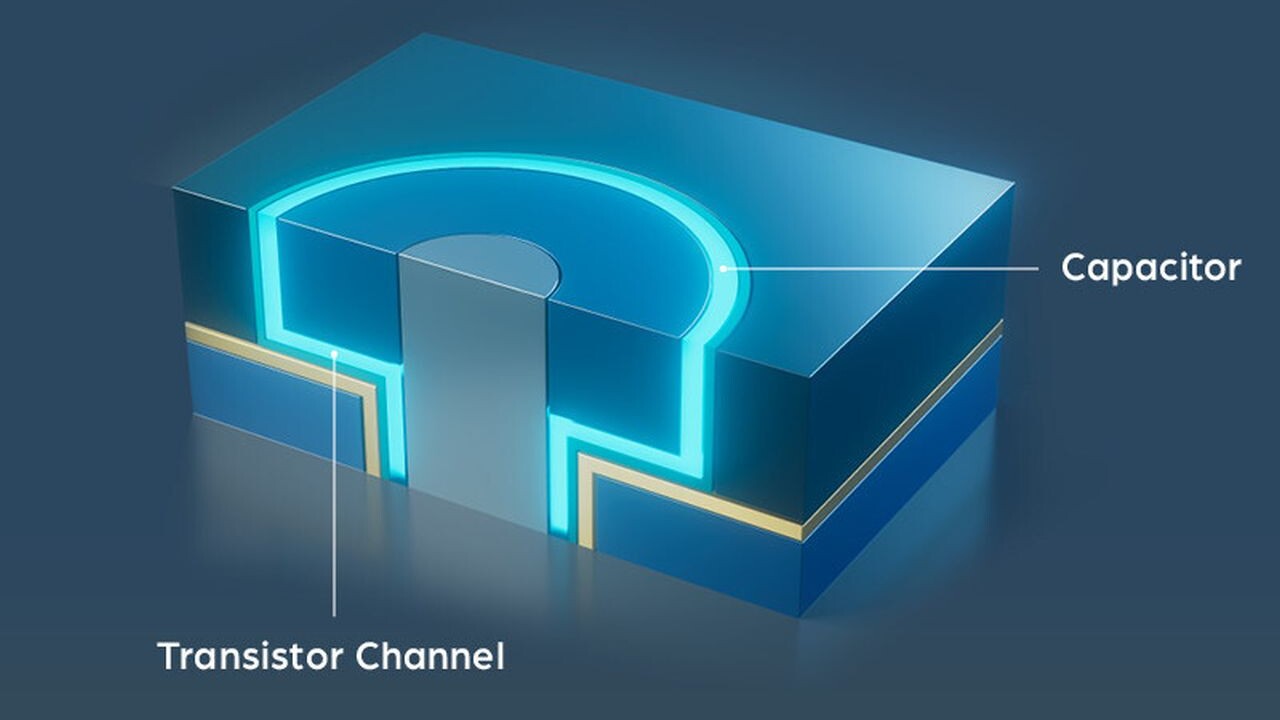

Jetzt geht es einen Schritt weiter. Unter Einsatz des Halbleitermaterials Indium-Gallium-Zink-Oxid (IGZO) sollen noch höhere Speicherkapazitäten möglich werden. Das Unternehmen spricht nun von bis zu 512 Gbit (64 GByte). Das wäre mehr als zehn Mal so viel wie bisherige 2D-DRAM-Chips erreichen und etwa halb so viel wie aktuelle 3D-NAND-Chips bieten.

Doch damit nicht genug, die bisher nur simulierten Chips sollen eine Retention Time von 450 Sekunden aufweisen. Herkömmlicher DRAM muss hingegen etwa alle 64 Millisekunden „aufgefrischt“ werden, um die Daten zu erhalten. Der 3D X-DRAM könnte bei Stromausfall also die Daten zumindest für einige Minuten vorhalten. Vor allem sorge dies aber für einen geringeren Energiebedarf durch seltenere Refreshs.

Grobe Leistungsangaben

Zur Leistung werden Angaben wie 10 Nanosekunden Zugriffszeit beim Lesen und Schreiben sowie „Ultra-High Bandwidth“ gemacht. Zumindest bei der Zugriffszeit könnte der Speicher also locker mit DRAM mithalten.

Angeblich einfach herzustellen

Um den 3D X-DRAM zu fertigen, bedarf es laut NEO Semiconductor lediglich einer leichten Modifizierung der bisherigen 3D-NAND-Prozesse mit „minimalen Änderungen“.

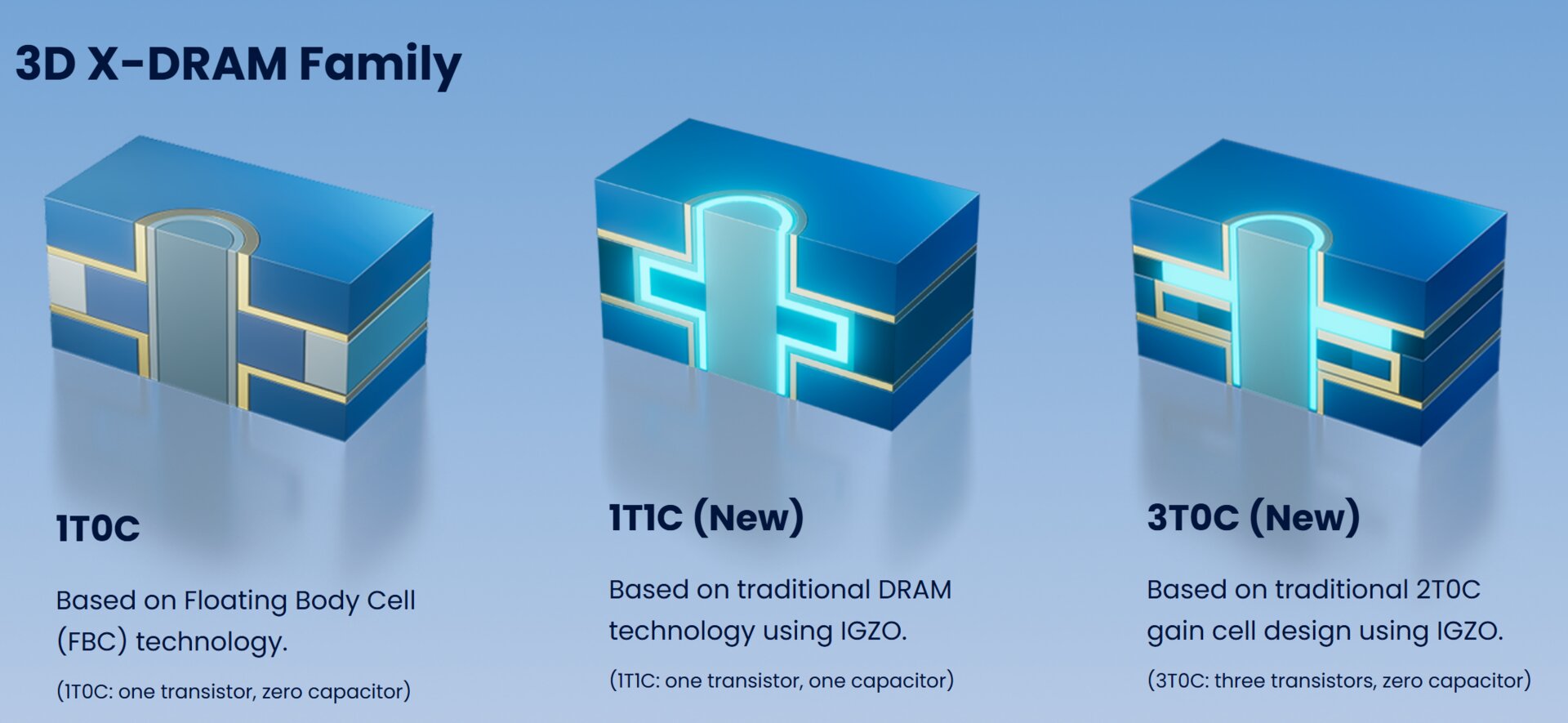

Inzwischen 3 Varianten des 3D X-DRAM

Mit den beiden neuen IGZO-Designs wächst die Zahl der Konzepte auf drei, die wie folgt beschrieben werden:

- 1T1C (one transistor, one capacitor) – The core solution for high-density DRAM, fully compatible with mainstream DRAM and HBM roadmaps.

- 3T0C (three transistor, zero capacitor) – Optimized for current-sensing operations, ideal for AI and in-memory computing.

- 1T0C (one transistor, zero capacitor) – A floating-body cell structure suitable for high-density DRAM, in-memory computing, hybrid memory and logic architectures.

Es fehlen noch echte Belege

Erstmals hatte ComputerBase im Jahr 2020 über das Start-up NEO Semiconductor berichtet, als es im Rahmen des Flash Memory Summit seinen X-NAND vorgestellt hatte. Das neue Konzept für Flash-Speicher versprach QLC-Kapazität mit SLC-Leistung. Für die Firma gab es zwar den Best of Show Award als innovativstes Unternehmen, doch wie es mit diesem Speicher weitergeht, ist unklar.

Auch beim X-DRAM bleibt abzuwarten, ob dieser die Versprechen halten kann und sich letztlich als Produkt umsetzen lässt. Für 2026 werden die ersten Chips als „Proof of Concept“ für den 3D X-DRAM erwartet.

Details zum 3D X-DRAM sind dem offiziellen Whitepaper (PDF) zu entnehmen.