Speicherforschung: SanDisk 3D Matrix Memory soll die Memory Wall einreißen

Die Weiterentwicklung von DRAM wird immer schwieriger und teurer. Das Heil suchen die Hersteller in der Vertikalen mit dreidimensionalen Strukturen, dem sogenannten 3D DRAM. SanDisk verfolgt mit dem 3D Matrix Memory einen neuen Ansatz. Dieser soll die vierfache Speicherkapazität bei halbierten Kosten ermöglichen.

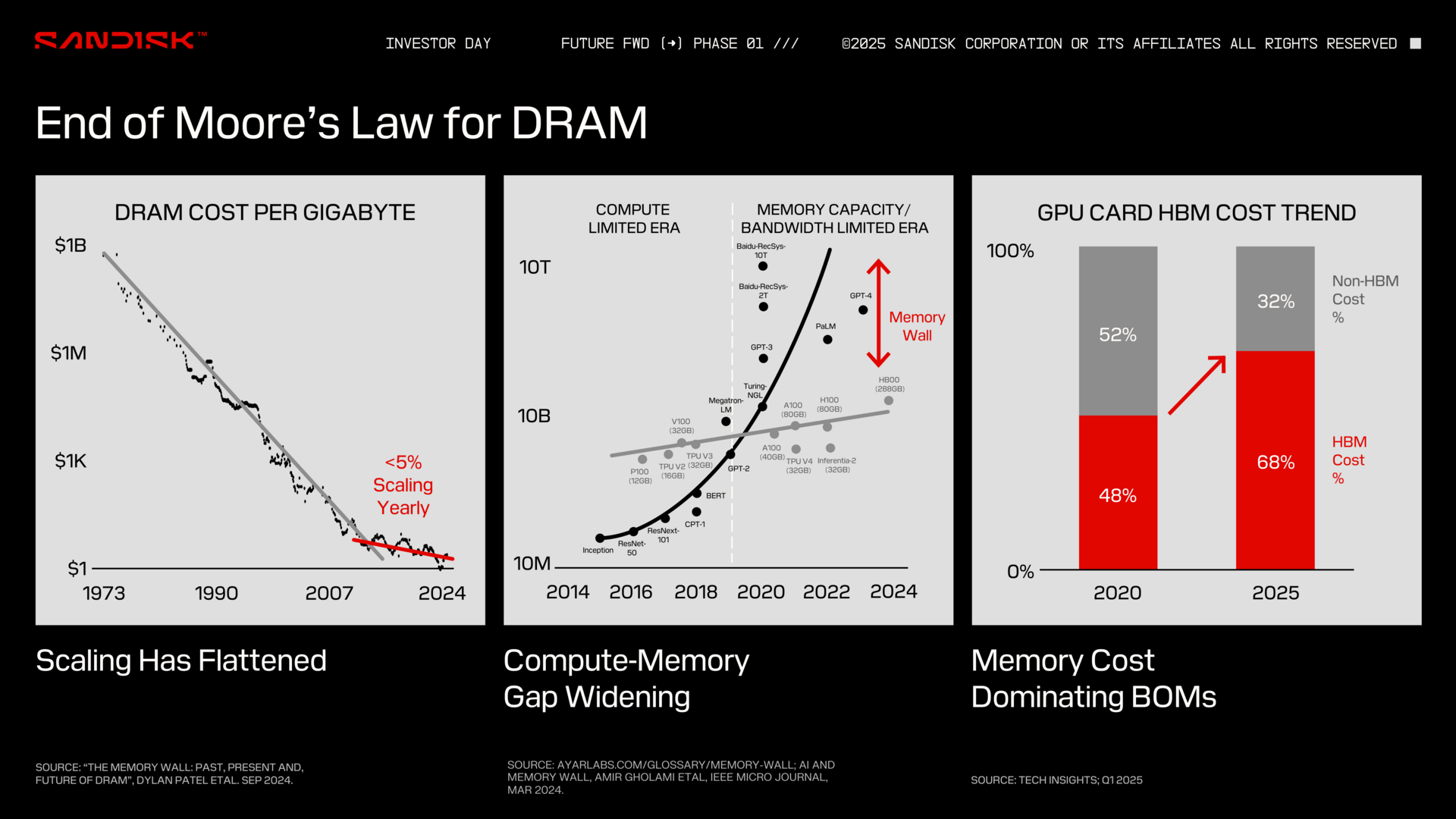

Die Branche rennt gegen eine Memory Wall, wie SanDisk in einer Präsentation zum Investor Day 2025 erklärt hat. Denn den seit über 50 Jahren als Arbeitsspeicher eingesetzten Dynamic Random Access Memory (DRAM) kann man nur noch mit hohem Kostenaufwand weiter skalieren, was etwa jüngst mit der teuren EUV-Lithografie geschieht. Die Speicherkapazitäten steigen nur noch langsam, was auch für die Reduzierung der Kosten pro Bit gilt.

Gerade jetzt, wo der weltweite Speicherbedarf durch das Aufkommen von KI-Anwendungen rasant wächst, wird dies zu einem Problem. SanDisk verweist auf eine Analyse von Techinsights, dass der Kostenanteil für Speicher bei GPU-Beschleunigern inzwischen mehr als die Hälfte beträgt. Der aus gestapelten DRAM-Chips bestehende High Bandwidth Memory (HBM) soll in diesem Jahr bereits 68 Prozent der Kosten einer solchen Beschleunigerkarte ausmachen.

SanDisk setzt auf 3D Matrix Memory

Zwar will die Branche mit 3D DRAM die hohen Kosten der EUV-Fertigung halbieren und DRAM weiter skalieren. Doch zumindest nach Ansicht von SanDisk ist 3D DRAM aufgrund der technischen Herausforderungen noch nicht soweit, obgleich Samsung einen kommerziellen Start für 2030 in Aussicht gestellt hat.

SanDisk zählt nicht zu den DRAM-Herstellern und verfolgt einen neuen Ansatz, den das Unternehmen 3D Matrix Memory getauft hat. Der Speicher sei für die Zukunft gut skalierbar und soll die vierfache Speicherkapazität von DRAM bei 50 Prozent der Kosten pro Bit ermöglichen. Das Leistungsniveau soll in etwa jenes von DRAM erreichen. Die technische Basis bildet ein neues Speicherzellendesign.

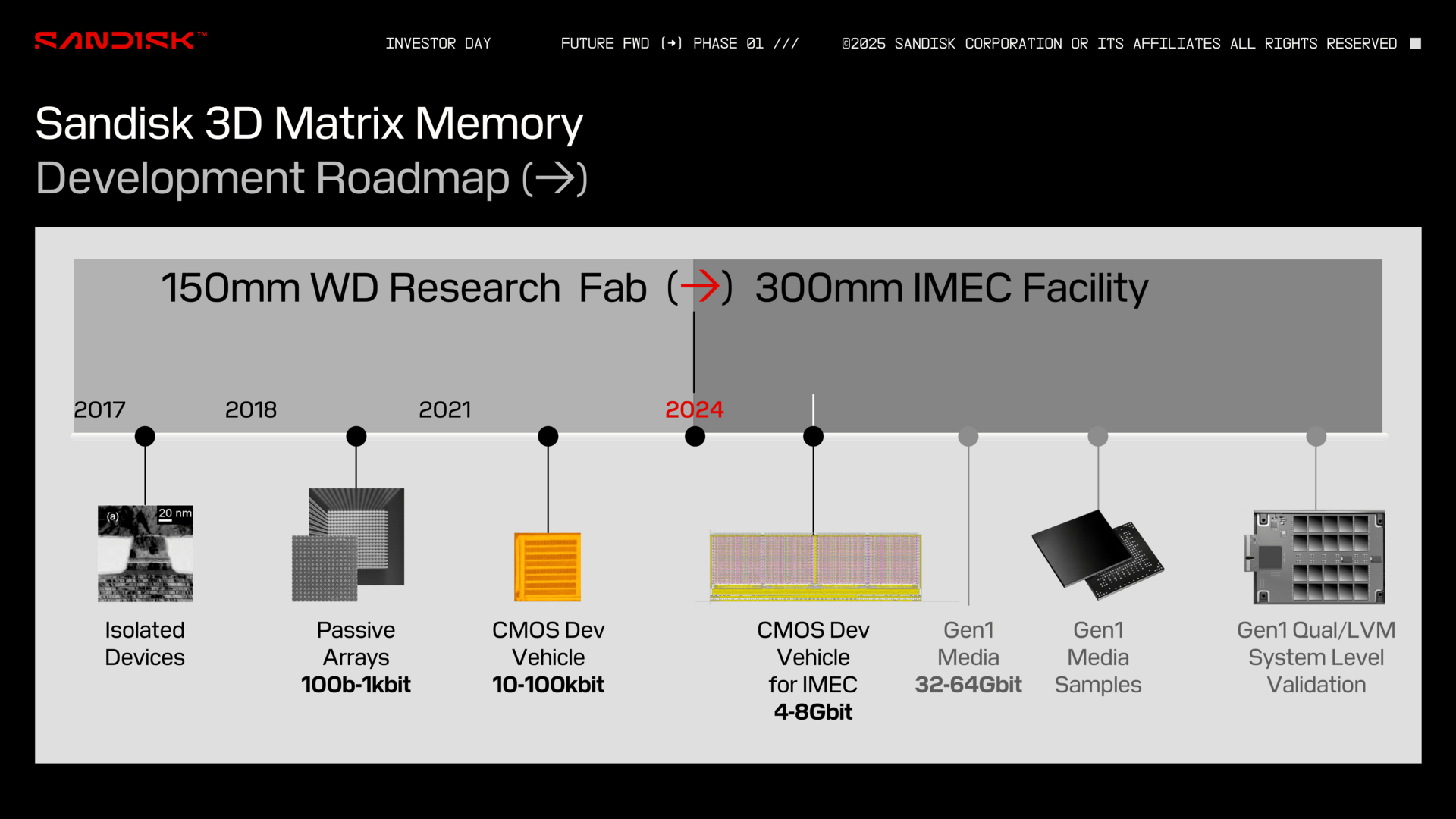

An diesem arbeitet SanDisk angeblich seit dem Jahr 2017 und hat erste Versuche in den eigenen Forschungsanlagen auf 150-mm-Wafern durchgeführt. Seit kurzem werden die modernen Reinräume des Forschungszentrum für Nano- und Mikroelektronik IMEC im belgischen Löwen genutzt. Anlagen mit einem Gegenwert von 700 Millionen US-Dollar bei IMEC sollen für die weitere Entwicklung des 3D Matrix Memory zum Einsatz kommen.

Dieser soll zum jetzigen Stand Speicherkapazitäten von 4 bis 8 Gbit erreichen. Das liegt noch weit unter den 32 bis 64 Gbit, die für die erste Generation geplant sind. Dennoch gibt es schon Abnehmer für die kleineren Forschungsvehikel: Das US-Verteidigungsministerium hat zugesichert, den neuen Speicher im Bereich der Luft und Raumfahrt einzusetzen. In der Klasse des „Strategic Radiation Hardened (SRH) Memory“ sollen die 4 Gbit immerhin das 16-fache der bisherigen Lösungen mit 256 Mbit bedeuten. In diesem Segment wird aber auch Magnetoresistive Random Access Memory (MRAM) eingesetzt.

High Bandwidth Flash für den Speicherhunger

Bis neue Speichertypen wie der 3D Matrix Memory von SanDisk oder der 3D DRAM hohe Speicherkapazitäten von 64 Gbit und mehr erreichen, wird es aber wohl noch viele Jahre dauern.

Den Speicherhunger der oben erwähnten KI-Beschleuniger will SanDisk mit seinem High Bandwidth Flash (HBF) stillen. Hier soll 3D-NAND dem HBM zur Seite stehen. 3D-NAND ist bereits bei 2 Tbit oder rund 2000 Gbit pro Chip angekommen. Allerdings sind die Zugriffszeiten und die möglichen Schreibzyklen deutlich schlechter aufgestellt, weswegen es kein wirklicher Ersatz für DRAM oder HBM sein kann.