AMD Ryzen und Epyc mit Zen 6(c): Gerüchte zu Medusa Ridge, Point, Halo und Epyc „Venice“

Auf Zen 5 und Zen 5c für Ryzen 9000 (Granite Ridge, Strix Point, Strix Halo) und Epyc (Turin) folgen Zen6 und Zen 6c – das und nur das ist offiziell bekannt. Seit dem Frühjahr kursieren allerdings Gerüchte um Chiplets mit bis zu 32 Kernen und seit Sommer auch Codenamen. Deren Urheber liefert jetzt nach.

Neue Gerüchte zu AMD Zen 6(c)

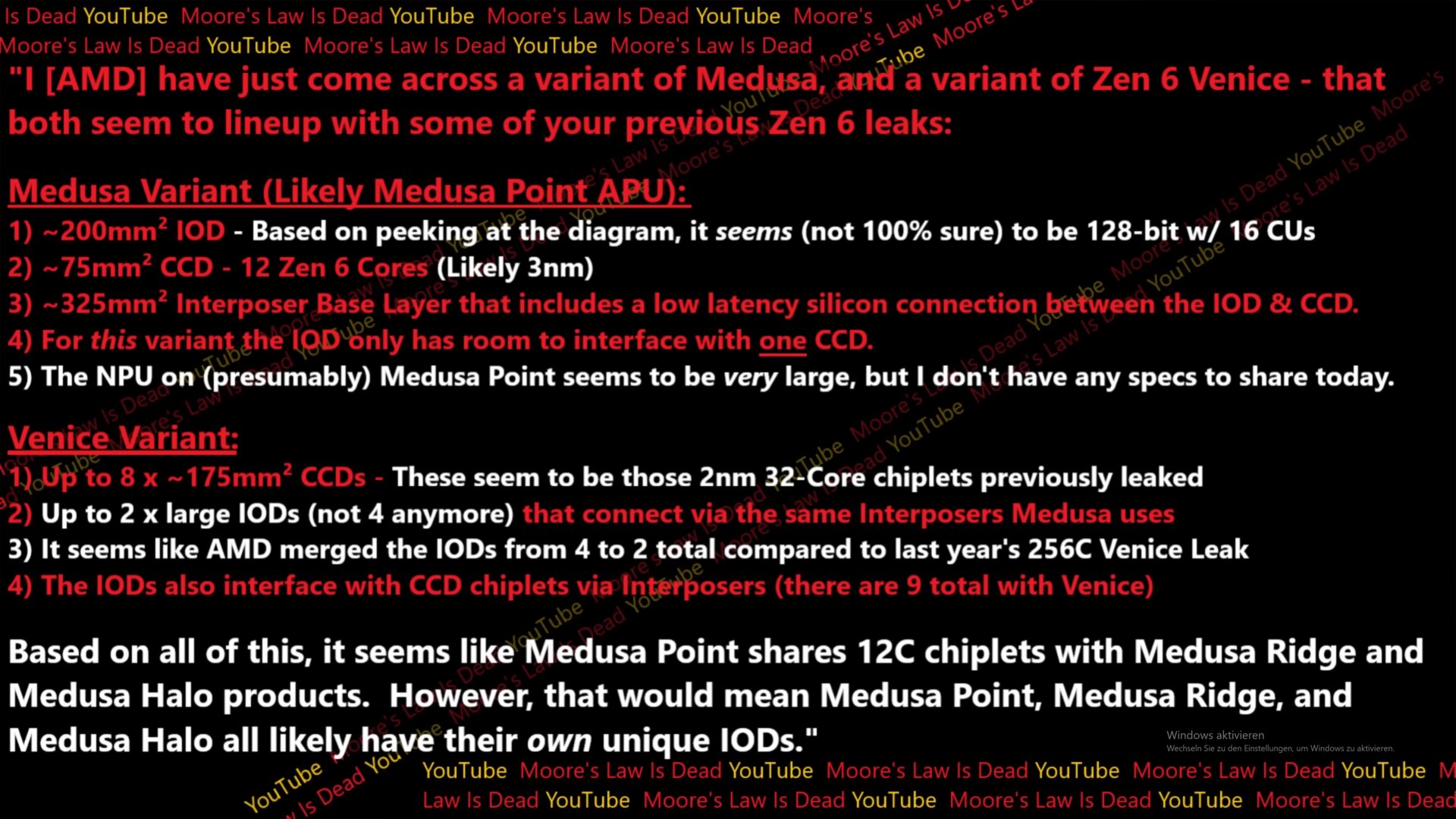

Erneut ist es der YouTube-Kanal Moore's Law is Dead (MLID), der neue Informationen zu AMDs Zen-6-Generation in Erfahrung gebracht haben will. Der sehr viele Gerüchte verbreitende Kanal verfügt zweifelsohne über Quellen in der Industrie, als besonders treffsicher gelten die „Leaks“ in der Branche jedoch nicht. Allerdings hat der für seine eher mit Bedacht veröffentlichten Leaks bekannte X-Account Kepler_L2 die neuesten Gerüchte mit „Good Job“ kommentiert. Derselbe Account hatte im Frühjahr die bis zu 32 Kerne pro CCD vermeldet.

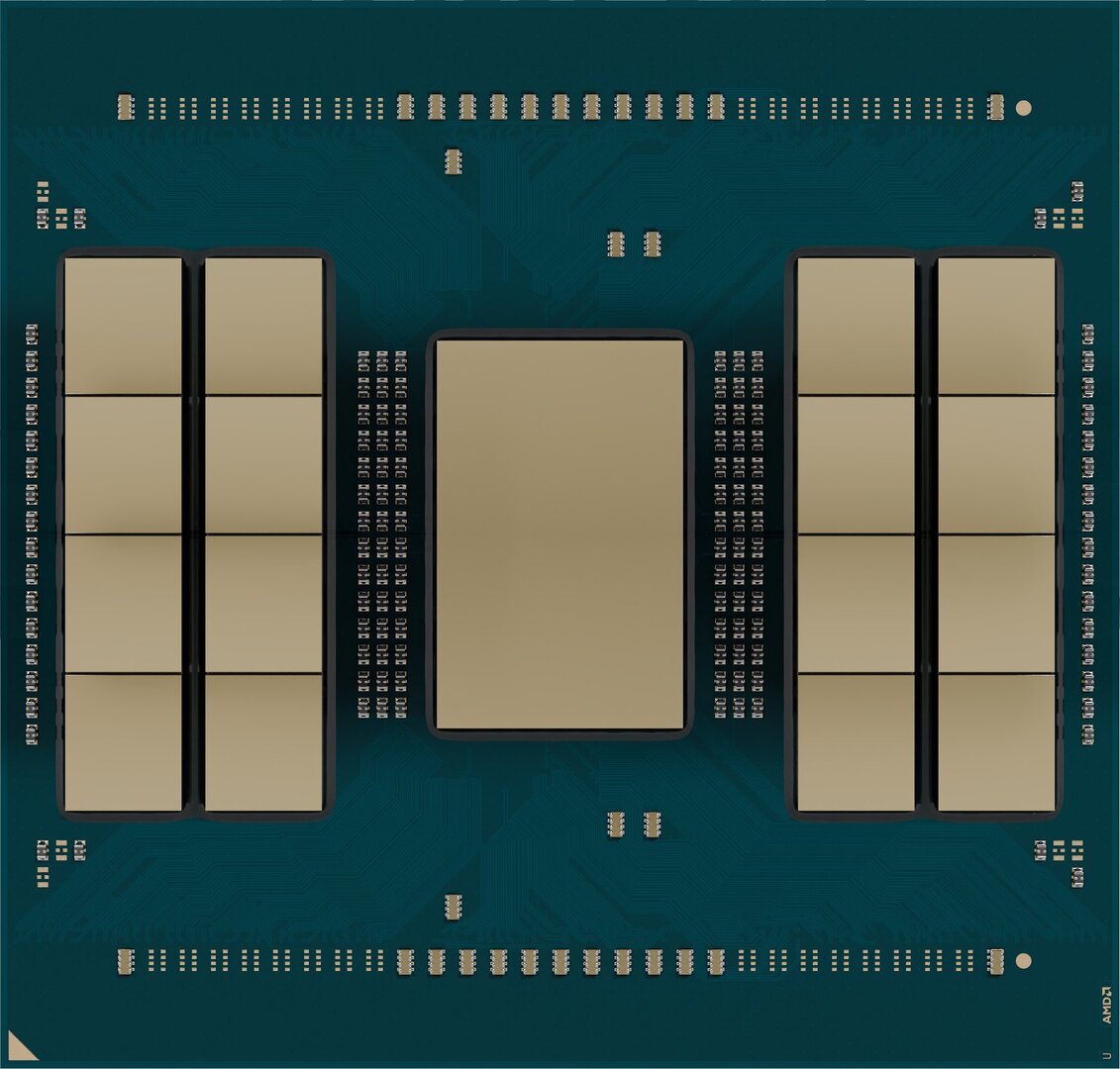

MLID vermeldet jetzt mutmaßlich neue Details zu den auf Zen 6 („Morpheus“) und Zen 6c („Monarch“) basierenden Ryzen-Serien Medusa Ridge (Desktop-Ryzen), Medusa Point (Notebook-APU mit kleiner iGPU) und Medusa Halo (Notebook-APU mit großer iGPU) sowie Venice (Epyc).

Im Desktop mit 12-Kern-Chiplets?

Demzufolge soll alle drei Medusa-Plattformen dasselbe 12-Kern-CCD (3 nm) einigen, was nicht nur der Vorhersage von Kepler_L2 widerspricht (Zen 6 mit 8-, 16- und 32-Kern-Chiplets), sondern auch bedeuten müsste, dass AMD mit Medusa den bis dato bei den APUs verfolgten monolithischen Ansatz (nur ein Die) ad acta legt. Doch laut MLID ist genau das der Fall: Das CPU-Chiplet und der I/O-Die würden dabei in Zukunft über einen neuen „Low Latency Base Layer“ kommunizieren. Die iGPU soll wie bei Strix Point abermals 16 CUs breit sein. Die NPU sei „sehr groß“.

Ob sich die 12 Kerne im Chiplet aus 12 Mal Zen 6 oder einer Kombination aus Zen 6 und Zen 6c zusammensetzen, bleibt abzuwarten, ist mit Blick auf Strix Point alias Ryzen AI 300 mit Zen-5- und Zen-5c-Kernen aber sehr wahrscheinlich. MLID spricht allerdings explizit lediglich von Zen 6.

Erhöht Epyc 9006 Venice auf 256 große Kerne?

Für Venice alias Epyc 9006 nennt MLID abermals maximal 8 Chiplets mit bis zu 32 Zen-6-Kernen und damit bis zu 256 Kernen – allerdings aus der 2-nm-Fertigung. Dass AMD Ryzen und Epyc beim Chiplet in Sachen Fertigung trennt, wäre neu.

Turin alias Epyc bietet als „Turin Classic“ aktuell maximal 128 Zen-5-Kerne mit 16 8-Kern-CCDs respektive mit maximal 192 Zen-5c-Kernen mit 12 16-Kern-CCDs. Venice würde durch viermal so breite Zen-6-CCDs die Anzahl der CCDs also wieder reduzieren – es sei denn, die Gerüchteküche vermischt aktuell noch Zen-6- und Zen-6c-Varianten.