AMD Zen 5: Hochauflösende Die-Shots zeigen überraschende Änderungen

Fritzchens Fritz, bekannt für extrem hochauflösende so genannte „Die-Shots“, hat auf seinem Flickr-Account erste Aufnahmen eines AMD Ryzen 5 9600X mit neuem 4-nm-Zen-5-Chiplet und bekanntem 6-nm-I/O-Die veröffentlicht. Erste Analysen der im Original über 100 GB großen Bilder zeigen interessante Veränderungen gegenüber Zen 4.

Was ist ein Die-Shot?

Der „Die“ ist der eigentliche Chip, so wie er vom Wafer kommt, ohne ein schützendes Package, das ihn im finalen Produkt umgibt. Auf dem Weg zu hochauflösenden Fotos, die den Aufbau des Dies zeigen, ist das Entfernen des Packages damit die erste Herausforderung. Fritzchens Fritz stellt sich dieser Herausforderung seit Jahren.

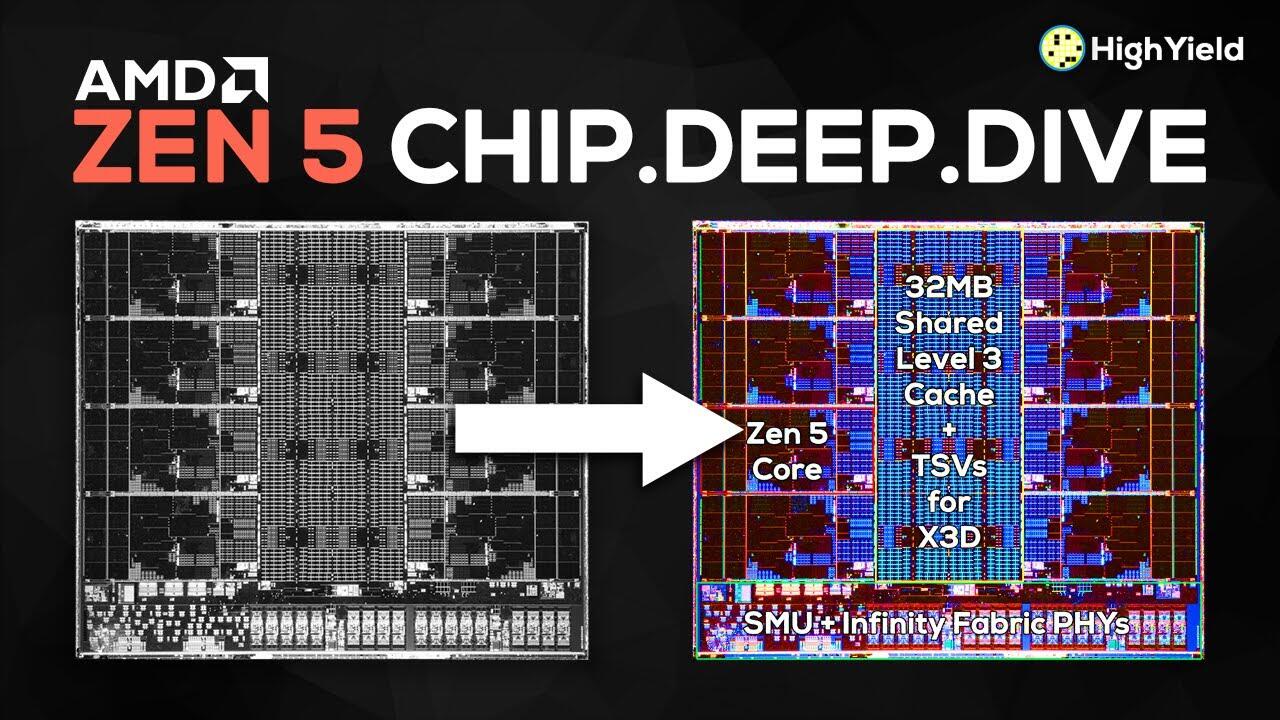

Zur Verfügung gestellt hat er seine Aufnahmen im Original (über 100 GB für ein Bild, das aus Hunderten Einzelaufnahmen zusammengesetzt wurde) dem YouTube-Account High Yield, der eine erste Analyse von Zen 5 im Vergleich zu Zen 4 vorgenommen hat. Beim I/O-Die ist das Fazit wenig überraschend wenig spektakulär, beim CPU-Chiplet sieht das hingegen ganz anders aus.

Der I/O-Die: Alles beim Alten

Der I/O-Die, den AMD mit Zen 4 alias Ryzen 7000 vor zwei Jahren mit einer 2-CU-iGPU vollständig neu aufgelegt hatte, ist in der Tat der alte geblieben. Das betrifft den Aufbau als solchen sowie die Fertigung (TSMC N6).

Das Zen-5-Chiplet: Fast alles neu

Regelrecht auf den Kopf gestellt hat AMD das weiterhin acht Kerne und 32 MB L3-Cache beinhaltende CPU-Chiplet. Vollständig neu wurde der Integer-Part der CPU gestaltet, aber auch die Fließkommaeinheit (FPU) hat grundlegende Änderungen erfahren. Bei der Integer-Einheit hat sich laut High Yield so viel getan, dass es ihm zurzeit noch nicht möglich ist, die einzelnen Bestandteile treffsicher zu benennen. Die FPU wurde wiederum quasi verdoppelt um AVX-512 möglich zu machen.

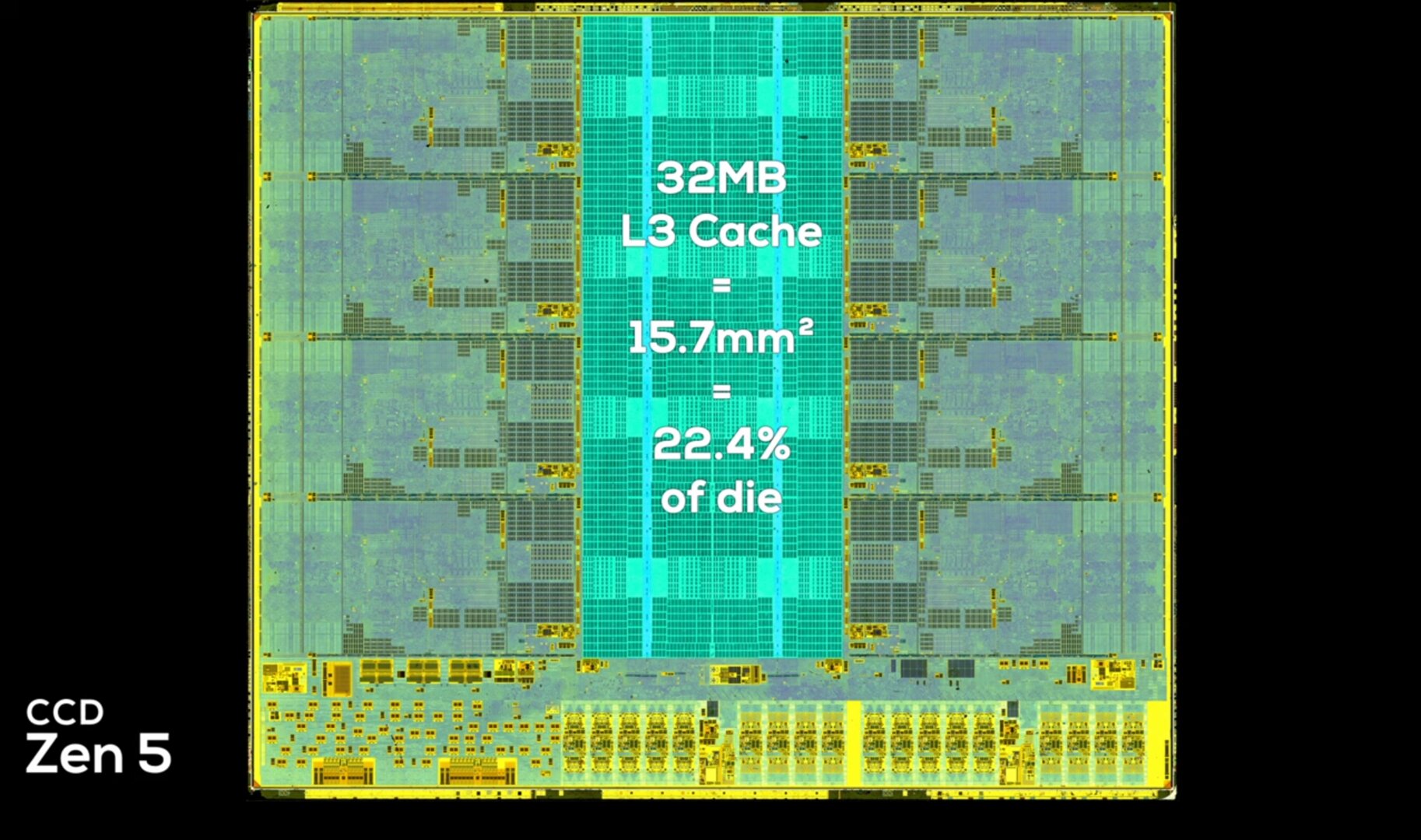

Der L3-Cache ist gravierend geschrumpft

Die eigentliche Überraschung hält aber der zentral gelegene L3-Cache parat, denn er nimmt, obwohl die Fertigung im Kern dieselbe geblieben ist und Cache-Zellen respektive deren Transistoren kaum noch mit kleineren Fertigungsstufen skalieren, eine wesentlich kleinere Fläche ein.

Grund dafür sind dann auch keine kleineren Cache-Blöcke, sondern dass AMD in der Lage gewesen ist, sie viel dichter zu packen. Im Ergebnis ist der L3-Cache-Block nur noch knapp 16 statt vormals 24 mm² groß und nimmt nur noch 22,4 statt 34,6 Prozent der Fläche des gesamten Chiplets ein.

Wie High Yield anmerkt, dürfte das Implikationen für X3D-CPUs haben. Bei diesen waren die 64 MB L3-Cache (3D V-Cache) zuletzt auf den L3-Cache und den zu beiden Seiten in den Kernen untergebrachten L2-Cache aufgesetzt – Cache verdeckte also lediglich Cache.

Sofern AMD am 3D V-Cache nicht ebenfalls gravierende Veränderungen vorgenommen hat, wird das auf einem Zen-5-Chiplet aber nicht mehr möglich sein – Cache müsste auch Kerne abdecken, was thermisch ein Problem darstellen dürfte.

Dass AMD auch den 3D V-Cache angepasst hat, dafür gibt es allerdings noch andere Hinweise, wenngleich das Bild unvollständig bleibt.

Viel weniger TSV-Kontakte als bisher?

Ein Zen-4-Chiplet wies bis dato über 24.000 so genannte TSV-Kontaktflächen im L3- und L2-Cache auf. TSV steht für Through-Silicon Via und wird im Deutschen Silizium-Durchkontaktierung genannt. Die vertikale Verbindungstechnik dient der Verbindung gestapelter Dies und hat Vorteile gegenüber dem sogenannten Wire Bonding mit feinen Drähten nur an den Rändern der übereinander gestapelten Chip.

Die Daten übertragenden TSVs fanden sich bei Zen 3 und Zen 4 in zwei Reihen innerhalb des L3-Caches, die Strom übertragenden TSVs bei Zen 4 im L3-Cache und im L2-Cache.

Auf den Fotos des Zen-5-Chiplets wurden bis dato hingegen nur knapp 9.000 derartige, viel kleinere Kontakte ausschließlich in zwei Reihen im L3-Cache ausfindig gemacht.

Entweder, so High Yield, wurde hier noch etwas übersehen, oder AMD könnte sich wirklich dazu entschlossen haben, einen doppelt gestapelten und dadurch kleineren Cache-Baustein auf den L3-Cache des Chiplets aufzusetzen.

Die Analyse steht noch am Anfang

Nicht nur die neue Integer-Einheit, sondern auch der bisherige Erkenntnisstand bei der Anzahl der TSV-Kontaktflächen werfen zur Zeit also noch Fragen auf.