AMD Zen 5: Neue CPUs bekommen zusätzliche AVX-Fähigkeiten und mehr

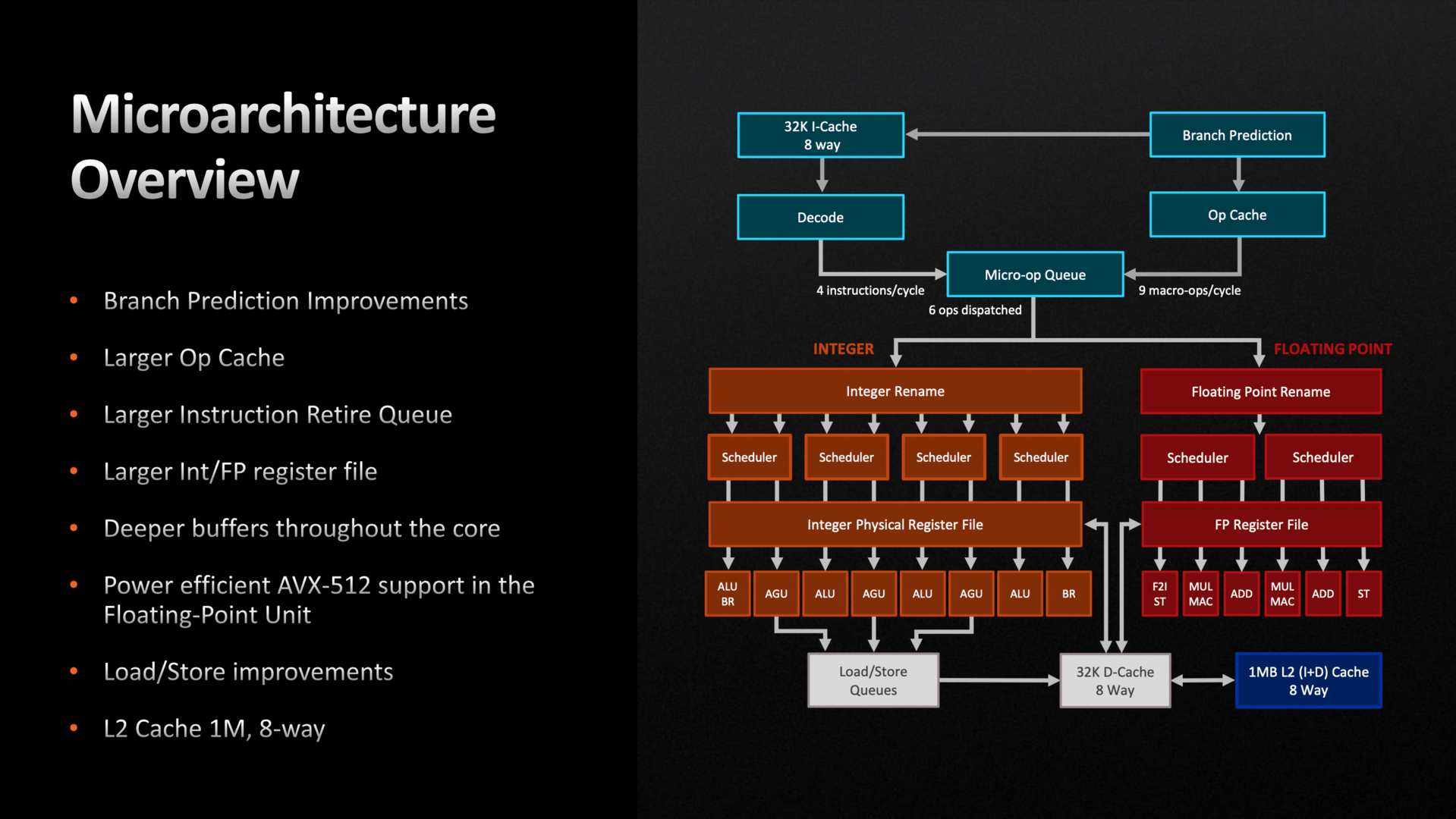

AMDs Zen-5-Architektur wird augenscheinlich vor allem fürs Profi-Segment gegenüber Zen 4 aufgebohrt, zusätzliche AGUs, ALUs sowie AVX-Fähigkeiten inbegriffen. AMD hatte zuvor bereits einmal offiziell erklärt, dass mit Zen 5 alles ein wenig breiter, aber auch effizienter werden soll, diese Anpassungen könnten dafür Sorge tragen.

Architektur geht in die Breite

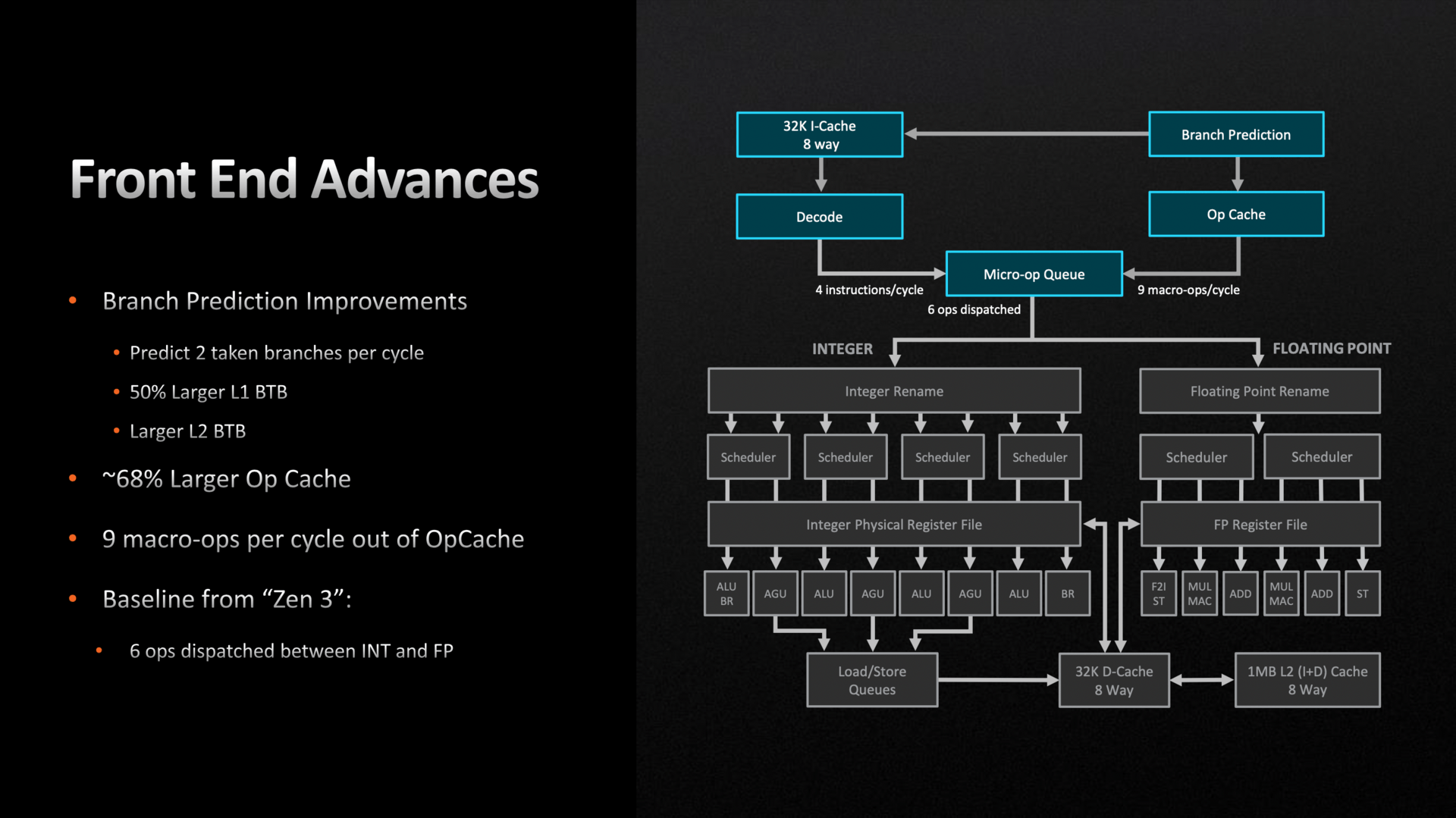

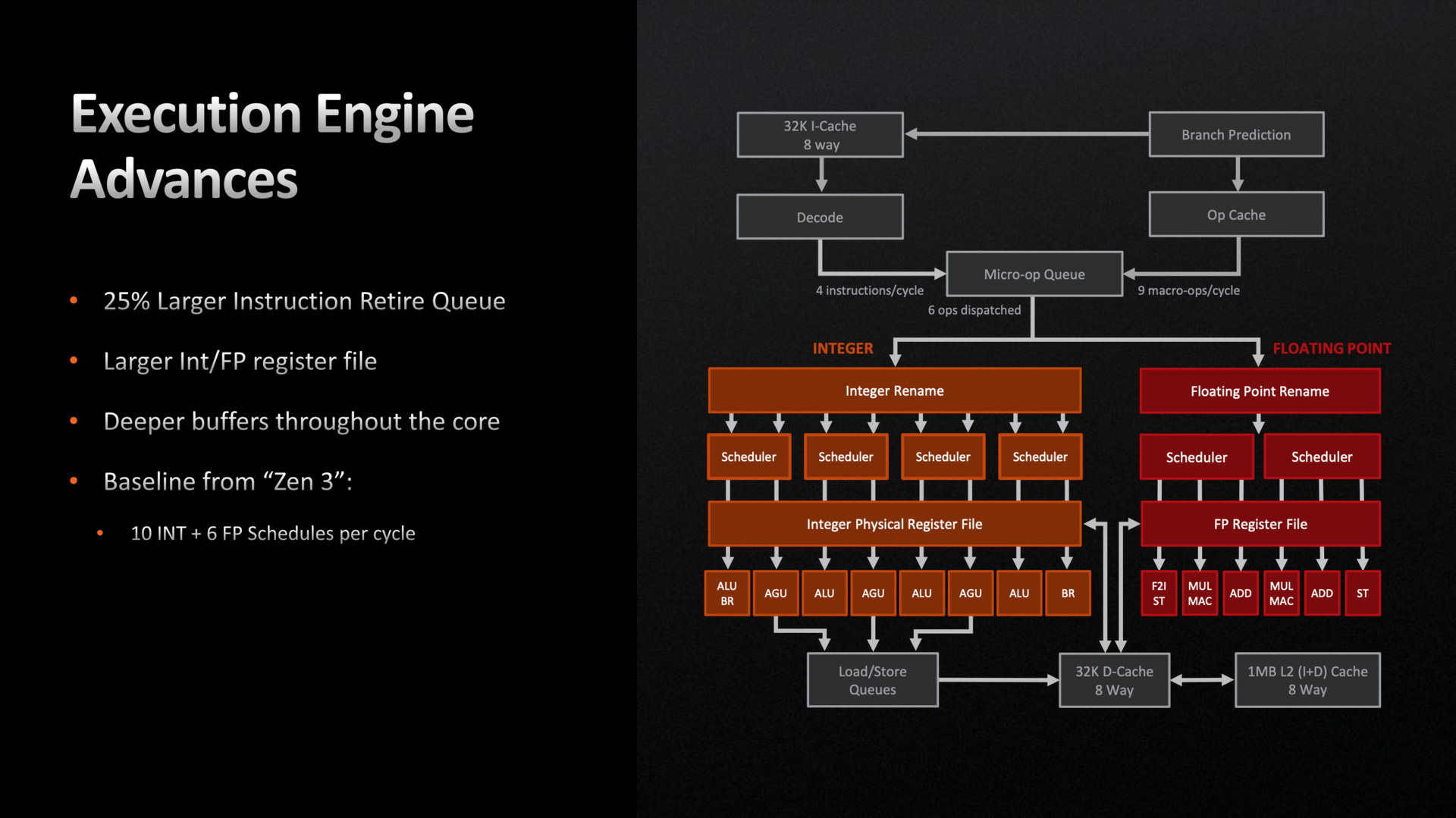

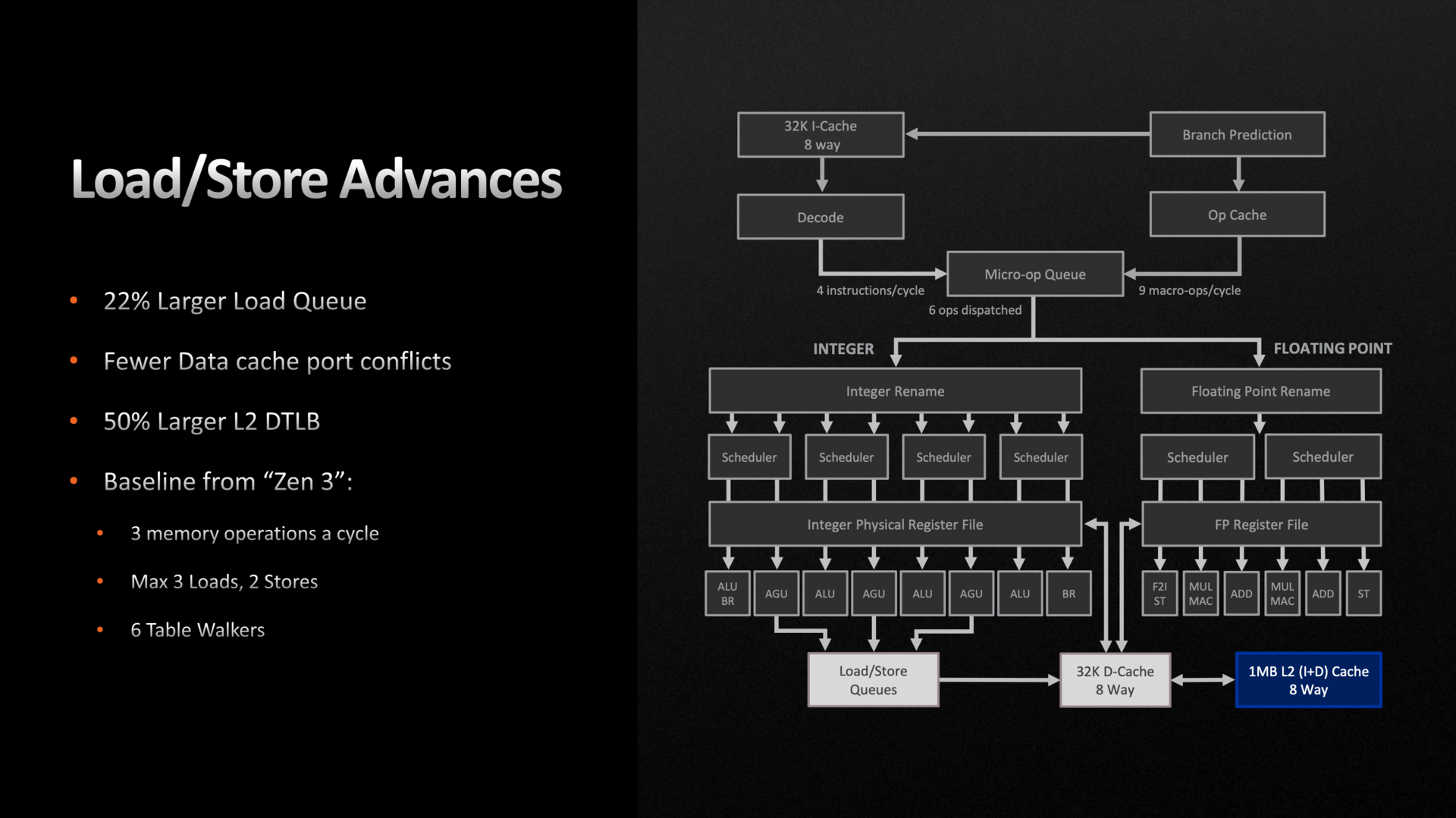

Vor allem hinsichtlich der AVX-Instruktionen plant AMD einen großen Schritt mit Zen 5 gegenüber der aktuellen Zen-4-Generation. Das geht aus einem von AMD selbst eingebrachten Patch der GNU Compiler Collection hervor. Nicht nur werden eine Menge weiterer Befehle unterstützt, auch wird die Architektur dafür umgebaut. Die FPU (Floating-Point Unit) wird 512-Bit-Befehle verstehen, verbleibt aber bei den in Zen 4 genutzten 2 × MUL + 2 × ADD zuzüglich 2 × Store. Die Anzahl der AGUs im Integer-Bereich erhöht sich im Vergleich zum bisherigen Modell bei Zen 5 von drei auf vier, bei den ALUs geht es laut dem Patch gar von vier auf sechs. Die neue Architektur geht somit in die Breite.

Die Eintragungen im Patch bestätigen das, was AMD bereits durchblicken ließ. Zen 5 soll vorherigen Aussagen zufolge „wider“, also breiter werden, und somit mehr auf einmal schaffen. Genau diesen Schritt ging auch Intel zuletzt in massiver Form, legte dort bei Alder Lake mit Golden Cove einen entsprechenden Grundstein, der noch heute Bestand hat. Rückhalt brauchen die Anpassungen in der Regel auch durch aufgebohrte Puffer und Caches, hierzu liegen für Zen 5 allerdings noch keine Informationen vor. Traditionell werden diese aber bei jeder neuen Architektur stets (etwas) vergrößert.

+;; Fix me: Need to revisit this later to simulate fast path double behavior.

+(define_reservation "znver5-double" "znver5-direct")

+

+

+;; Integer unit 6 ALU pipes.

+(define_cpu_unit "znver5-ieu0" "znver5_ieu")

+(define_cpu_unit "znver5-ieu1" "znver5_ieu")

+(define_cpu_unit "znver5-ieu2" "znver5_ieu")

+(define_cpu_unit "znver5-ieu3" "znver5_ieu")

+(define_cpu_unit "znver5-ieu4" "znver5_ieu")

+(define_cpu_unit "znver5-ieu5" "znver5_ieu")

+

+;; As of now we have taken based on znver4, We need to revist once znver5 information

+(define_cpu_unit "znver5-bru0" "znver5_ieu")

+(define_reservation "znver5-ieu" "znver5-ieu0|znver5-ieu1|znver5-ieu2|znver5-ieu3|znver5-ieu4|znver5-ieu5")

+

+;; 4 AGU pipes in znver5

+(define_cpu_unit "znver5-agu0" "znver5_agu")

+(define_cpu_unit "znver5-agu1" "znver5_agu")

+(define_cpu_unit "znver5-agu2" "znver5_agu")

+(define_cpu_unit "znver5-agu3" "znver5_agu")

+(define_reservation "znver5-agu-reserve" "znver5-agu0|znver5-agu1|znver5-agu2|znver5-agu3")

+

+;; Load is 4 cycles. We do not model reservation of load unit.

+(define_reservation "znver5-load" "znver5-agu-reserve")

+(define_reservation "znver5-store" "znver5-agu-reserve")

+

+;; vectorpath (microcoded) instructions are single issue instructions.

+;; So, they occupy all the integer units.

+(define_reservation "znver5-ivector" "znver5-ieu0+znver5-ieu1

+ +znver5-ieu2+znver5-ieu3+znver5-ieu4+znver5-ieu5+znver5-bru0

+ +znver5-agu0+znver5-agu1+znver5-agu2+znver5-agu3")

+

+;; Floating point unit 4 FP pipes.

+(define_cpu_unit "znver5-fpu0" "znver5_fpu")

+(define_cpu_unit "znver5-fpu1" "znver5_fpu")

+(define_cpu_unit "znver5-fpu2" "znver5_fpu")

+(define_cpu_unit "znver5-fpu3" "znver5_fpu")

+

+(define_reservation "znver5-fpu" "znver5-fpu0|znver5-fpu1|znver5-fpu2|znver5-fpu3")

+

+;; Floating point store unit 2 FP pipes.

+(define_cpu_unit "znver5-fp-store0" "znver5_fp_store")

+(define_cpu_unit "znver5-fp-store1" "znver5_fp_store")

Zusätzliche AVX-Fähigkeiten

Zu den aufgewerteten AVX-Fähigkeiten zählen unter anderem AVXVNNI, MOVDIRI, MOVDIR64B, AVX512VP2INTERSECT und PREFETCHI. Letztere bekommt Intel erst mit Granite Rapids, die drei mittleren gibt es in Intels CPUs aber seit Tiger Lake. AVX-VNNI könnte trotz seiner Abstammung nicht aus dem AVX-512-Befehlssatz im angehenden AI-Zeitalter durchaus an Bedeutung gewinnen, Intel wird dies ebenso breit unterstützen.

IPC-Zugewinn unbekannt, Vorbereitungen laufen

Anhand der Anpassungen lassen sich aktuell noch keine Rückschlüsse auf die zusätzliche Leistung ziehen, schon gar nicht auf die IPC, mit der sich die Gerüchteküche zu gern beschäftigt und dort oft über das Ziel hinausschießt. Denn diese ist stark abhängig von den Testszenarien, AMD hatte hier zuletzt erstmals unterschiedliche IPC-Zugewinne für den Desktop inklusive Gaming und das Profi-Segment benannt. Die Anpassungen in den Patches, wenngleich diese explizit als nicht final gekennzeichnet sind, deuten darauf hin, dass das Profi-Segment aber tendenziell eher profitieren könnte. Die Anpassungen im Front End, die AMD ebenfalls bereits angedeutet hat, sind jedoch noch unbekannt.

Interessant ist zudem das Timing: Für Zen 4 gab es diese Patches erst nach der Vorstellung von Ryzen 7000 im Oktober 2022, die Pflege der neuen Anpassungen für Zen 5 soll anscheinend einen reibungslosen Start später im Jahr vorbereiten. Zen 5 soll dabei auf breiter Front in allen Bereichen vom Notebook über den Desktop bis zum Server vermutlich im zweiten Halbjahr 2024 erscheinen, hatte AMD zuletzt noch einmal bestätigt.