Intel Granite Rapids-D: Xeon 6 SoC mit zwei 44-Kern-Tiles plus I/O bildet neue Xeon D

Intels Server-Prozessoren der Baureihe Xeon D waren bereits stark, in der nächsten Generation gehen sie aber auf das nächste Level: 2 × 44 Redwood-Cove-Kerne auf kleinstem Raum. Dafür nutzt das Xeon 6 SoC die Basis von Granite Rapids mit multiplen Tiles, packt dazu aber einen neuen I/O-Die, was dem Einsatzgebiet geschuldet ist.

Die Zeit der kleinen Xeon D scheint vorbei zu sein. Zumindest dürfen sie in Zukunft viel weiter nach oben gehen, wie die Präsentation von Intel zur Hot Chips 2024 verrät. Dass es darunter auch kleinere Lösungen geben wird, ist weiterhin zu erwarten. Denn genau dort sollten die CPUs ursprünglich hin, und die Brücke zu den großen Xeons schlagen.

Bei der Präsentation von Intel musste man dann aber schon gehörig aufpassen. Denn offiziell nannte der Hersteller heute noch nicht die Anzahl der Kerne, das Demo-System hatte „nur“ 42 Kerne und vier Speicherkanäle. Doch auf den Folien stand es dann doch ziemlich offensichtlich: Mehr als die dreifache Anzahl an Kernen und Speicherbandbreite soll mit dem Xeon 6 geboten werden. Von den 22 Kernen, die Xeon D bisher bietet, geht es dann doch ganz schnell in Regionen, die bisher nicht auf dem Schirm waren.

Der Tile-Ansatz der großen Granite Rapids

Intel nutzt für das Xeon 6 SoC den Tile-Ansatz von Granite Rapids. Bis zu zwei Compute-Tiles werden von einem angepassten I/O-Tile unterstützt. Die zwei Compute-Tiles kommen einem schnell vertraut vor: Es sind die gleichen in Intel 3 gefertigten Kerne, wie sie Granite Rapids-SP/AP nutzt. Und dann ist mathematisch auch schnell die Anzahl der möglichen Kerne erklärt: Granite Rapids-AP nutzt 3 Tiles und bietet 128 Kerne in der Maximalkonfiguration, pro Tile sind 44 Kerne verbaut, jedoch nicht alle aktiv. Verbunden werden sie via EMIB.

Zwei Tiles bieten also 88 Kerne, 88 geteilt durch die bisherigen 22 Kerne ergibt einen Faktor >3, wie ihn das Marketing auf die Folien geschrieben hat. Da in diese Rechnung jedoch auch die Speicherbandbreite einfließt und eine komplette Nutzung des 44-Kern-Tiles unrealistisch ist, dürfte es am Ende vermutlich auf etwa 70 bis 80 aktive CPU-Kerne und viele weitere Modelle mit geringerer Anzahl darunter hinauslaufen. Dabei dürfte es auch 1-Tile-Lösungen geben, wie die Erklärungen von Intel verdeutlichen.

Selbst MCR-DIMMs sind mit dabei

Angeschlossen an jeden CPU-Tile sind die Speichercontroller. Auch diese sind beim Xeon 6 SoC alte Bekannte, selbst die Unterstützung für neue MCR-DIMMs bringt Intel für die ehemals kleinen Xeon D vom großen Granite Rapids mit. Die 1-Tile-CPUs erhalten so vier Speicherkanäle, die mit zwei CPU-Tiles deren acht. Schnell ist damit eine nahezu automatische Segmentierung im Portfolio erreicht: die kleineren Varianten mit 42 Kernen und 4-Kanal-Speicher – so wie im Demo-System – und die großen Chips mit der doppelten Menge in beiden Bereichen.

Am Ende entstehen so zwei Packages, die unterschiedlich groß sind. Dennoch verspricht Intel eine kompatible Plattform, um die Kosten für Boardpartner zu senken. In das 8-Kanal-Board passt auch ein 4-Kanal-Produkt.

Der I/O-Die ist neu

Den I/O-Tile der regulären Xeon-Plattform mit zweigeteiltem Aufbau konnte Intel aber nicht auch noch übernehmen. Dafür ist das Einsatzgebiet zu speziell, so spielt beispielsweise integriertes Ethernet bei den Xeon D eine Rolle. Bei den großen Xeons wird der Netzwerkbereich über viele, viele PCIe-Lanes später vom Kunden selbst realisiert.

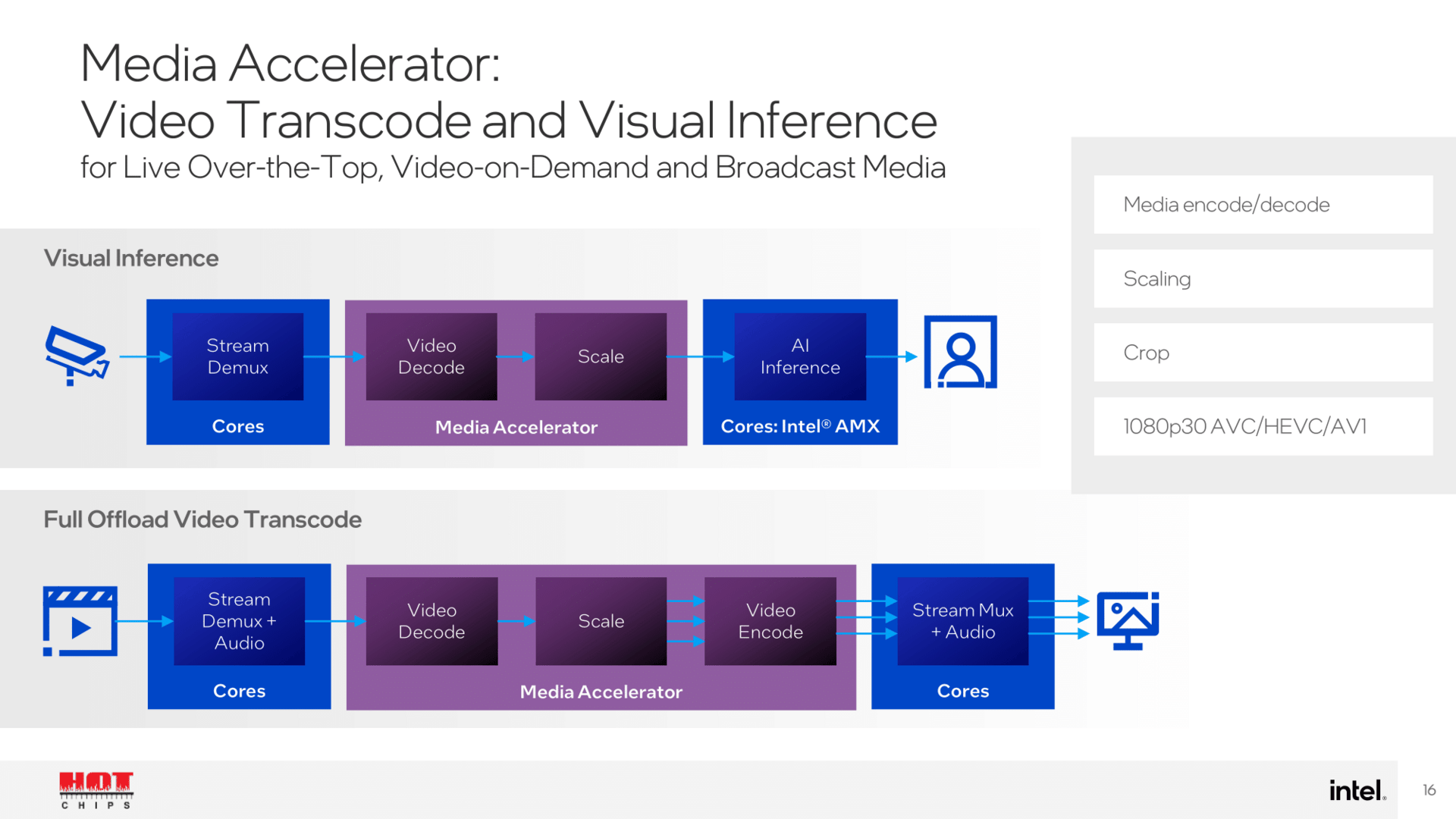

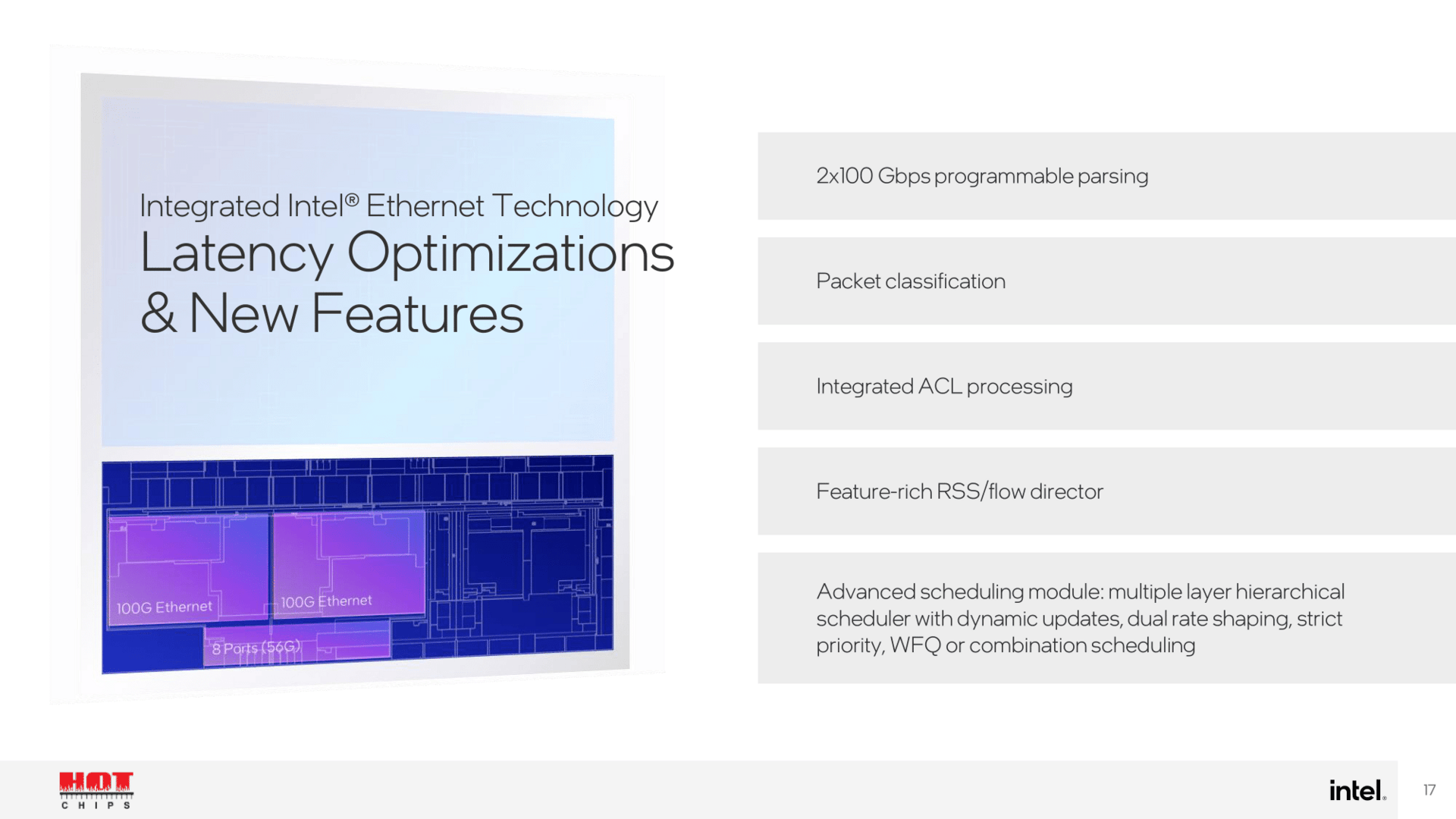

Der I/O-Die wird in Intel 4 gefertigt. Er enthält quasi alles, was zur Kommunikation mit der Außenwelt nötig ist, inklusive PCIe, CXL in aktueller Version 2.0 und Ethernet, aber auch Beschleuniger multipler Art, inklusive erstmals verbauter Media Acclerators mit Features wie Decode und Encode. Acht Ports für Ethernet sind ebenfalls dabei.

AMX, SGX, TDX und mehr

Gegenüber dem Vorgänger Ice Lake-D macht die Plattform in vielen Bereichen einen großen Sprung. Denn de facto wird eine ganze Generation übersprungen – Intel Sapphire Rapids mit dem Refresh Intel Emerald Rapids – sodass nun auch beim Xeon 6 SoC Technologien wie AMX & Co Einzug halten.

Das verspricht satte Leistungsgewinne bereits beim Einsatz der kleinen 1-Tile-Version mit 4-Kanal-Speicher, für die 8-Kanal-Lösung, die auch mit MCR-DIMMS kommt, stellt Intel noch viel mehr Leistung in Aussicht, ohne sie heute auf der Bühne zu benennen. Hinsichtlich der integrierten Sicherheitsfunktionen gibt es die aktualisierte Version von SGX als auch neuerdings hier TDX.

In der Fragerunde nach der Präsentation ging Intel auf einige Details ein. So erklärte das Team, dass DDR5 gegenüber LPDDR5 bevorzugt wurde, weil die Kapazität schnell und günstiger viel größer werden könne. Auch AVX-512 wurde von Intel bestätigt, ebenso die weitere Nutzung von Hyper-Threading, was dem Redwood-Cove-Kern geschuldet ist.

- IBM Telum II: 8 Kerne, DPU und 360 MB L2-Cache erschaffen Monster-Chip

- Intel Granite Rapids-D: Xeon 6 SoC mit zwei 44-Kern-Tiles plus I/O bildet neue Xeon D

- Nvidia & Supermicro: Wie (AI-)Rechenzentren einen kühlen Kopf bewahren

- +2 weitere News