MTIA v2: Metas zweite Generation des eigenen AI-Chips ist viel schneller

Es ist die Zeit für AI, aber auch die Zeit für neue Chips – nahezu jeder Großkonzern hat in den letzten Wochen und Monaten hier etwas Neues präsentiert. Meta stellt nun die neue Generation ihrer Lösung vor, die dreimal schneller wird als das bisherige Modell, welches gerade ein Jahr alt ist.

Entgegen Googles Ankündigung zum Axion ohne auch nur einen technischen Fakt überrascht Meta positiv mit vielen technischen Details. MTIA v2, das steht für Meta Training and Inference Accelerator in der zweiten Version, folgt auf den erst im Mai des letzten Jahres vorgestellten MTIA v1. Der Chip war explizit auf die eigenen Anwendungen ausgelegt, mit dem Hintergrund von Deep Learning aber auch Inference und Training.

Dabei offenbarten sich aber auch schnell kleinere Schwachstellen am Design, weshalb nun binnen kurzer Zeit die zweite Generation folgt. Das ist in dem Bereich gar nicht so unüblich, die Mitbewerber mit eigenen AI-Chips haben zum Start ihrer Lösungen einen ziemlich ähnlichen Zeitplan verfolgt, denn viele Schwachstellen werden erst im realen Alltag sichtbar und nicht in Simulationen vorab.

Mit MTIA v2 wird deshalb direkt die Compute- aber auch Speicherbandbreite mehr als verdoppelt, einige Bereiche erhalten noch viel größere Wachstumsfaktoren. Herzstück ist ein 8 × 8-Gitter an processing elements (PEs), wie Meta die Kerne nennt. Bei diesen wurde die Architektur optimiert, vor allem aber an den Speichern geschraubt: Der On-Chip-SRAM ist doppelt so groß und hat nun 3,5 Mal mehr Bandbreite als in Gen1, schon die PE-Kerne besitzen einen drei Mal so großen Zwischenspeicher. Abgerundet wird dies von einem doppelt so großen ansprechbaren LPDDR5-Speicher, der zudem auch noch höher taktet. Damit diese Leistung auch nach außen geführt werden kann, wird die Netzwerkleistung verdoppelt. Man erkennt also schnell: Flaschenhälse bei der Bandbreite aufzulösen war die Hauptaufgabe in der zweiten Generation.

Doch dafür wächst auch der Chip: Trotz des Wechsels auf die kleine N5-Fertigung von TSMC ist der Chip nun 421 mm² groß, zuvor waren es in N7 noch 373 mm². Mit höherer Spannung und viel höherem Takt geht bei dem zweiten Modell auch eine deutliche Steigerung der TDP mit einher, 90 Watt sind es nun statt zuvor 25 Watt. Das wirkt sich am Ende leicht negativ auf die Effizienz aus, bei 25 Watt und sehr niedriger Spannung und ganz geringem Takt war die erste Generation extrem effizient, trotz der nun deutlichen Mehrleistung schafft es das neue Modell in diesen Bereich nun nicht mehr, liegt aber nur minimal dahinter.

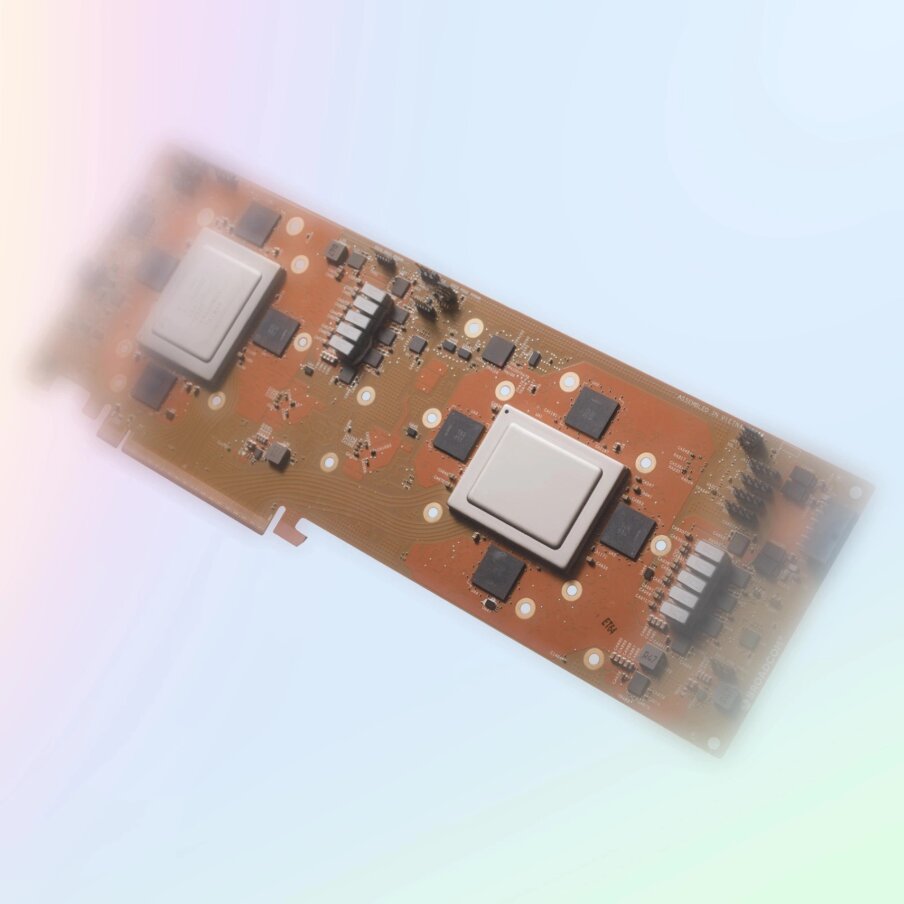

Bis zu 72 Chips werden auf 36 PCIe-Gen5-Karten in je 3 × 12 Stück bei Meta in Racks verstaut. Für die Option auf ein Scale-out kann ein RDMA-NIC genutzt werden. In diese Richtung dürfte Meta nun weiter forschen, das Unternehmen plant noch weiter Hardware – inklusive GPUs:

We’re designing our custom silicon to work in cooperation with our existing infrastructure as well as with new, more advanced hardware (including next-generation GPUs) that we may leverage in the future. Meeting our ambitions for our custom silicon means investing not only in compute silicon but also in memory bandwidth, networking and capacity as well as other next-generation hardware systems.

We currently have several programs underway aimed at expanding the scope of MTIA, including support for GenAI workloads.