ISSCC 2025: Samsung bereitet 4xx Layer V10 TLC-NAND mit 5,6 Gb/s vor

Im Februar startet die International Solid-State Circuits Conference, kurz ISSCC 2025. Hier sind technische Details zu neuen Halbleiterprodukten zu erwarten. So auch für 3D-NAND der nächsten Generation. Was Samsung, SK Hynix und Kioxia so planen, liest sich zumindest eindrucksvoll.

Samsungs 4xx Layer TLC-NAND

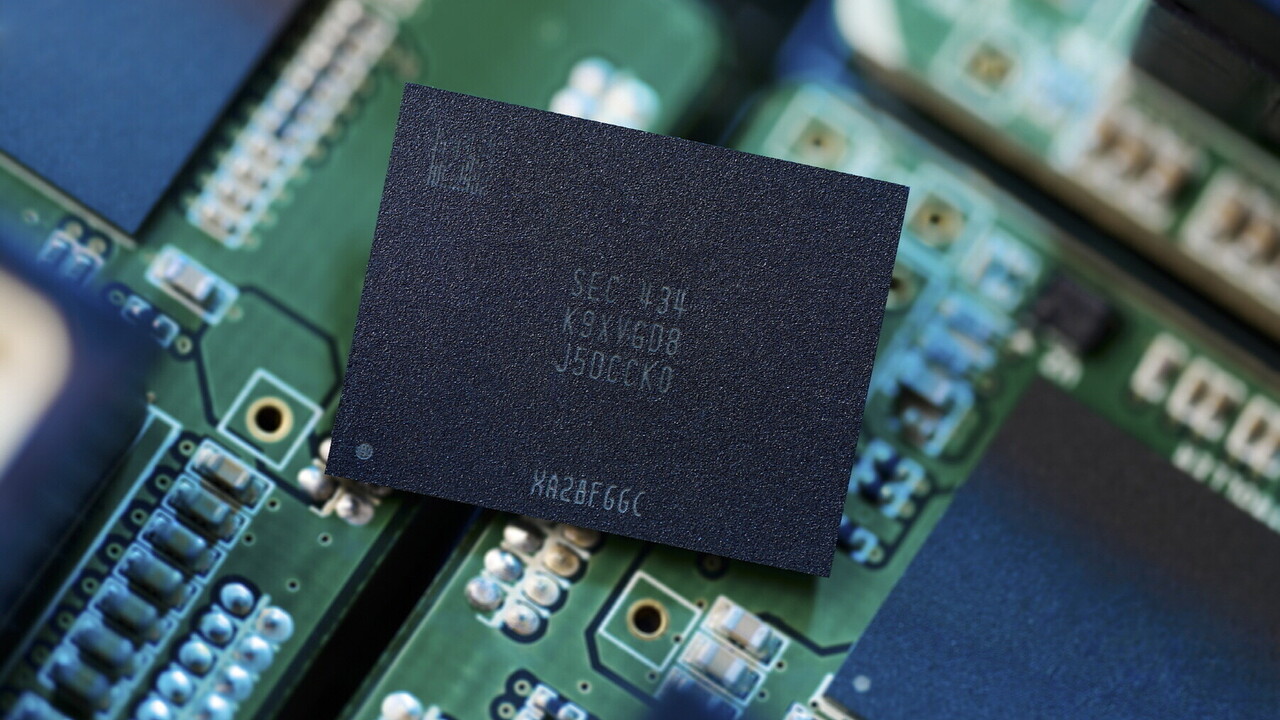

Stand in diesem Jahr der QLC-NAND mit 28,5 Gbit/mm² (siehe Titelbild) im Fokus, der die bisher höchste Flächendichte von 3D-NAND bietet, will Samsung das mit einer kommenden Generation auch mit TLC und 3 Bit pro Zelle schaffen.

„A 28Gb/mm² 4XX-Layer 1Tb 3b/cell WF-Bonding 3D-NAND Flash with 5.6Gb/s/pin IOs“ lautet eine geplante Session von Samsung auf der ISSCC 2025. Der TLC-NAND mit „4xx“, also über 400 Layern, soll mit 28 Gbit/mm² fast genauso viel Speicherkapazität pro Fläche aufweisen wie der 286-Layer-QLC-NAND der Generation V9, der im September in Serie ging.

Beachtlich ist aber auch das schnelle NAND-Interface von 5,6 Gbit/s pro Pin. Die bis dato in diesem Punkt schnellsten NAND-Chips liegen bei 3,6 Gbit/s.

Samsung war lange Zeit führend bei 3D-NAND, geriet in den letzten Jahren aber ins Hintertreffen und muss jetzt wieder aufholen. Dass mit dem 4xx-Layer-NAND erstmals bei Samsung auf Waferbonden bei der Herstellung gesetzt wird, ist bei Konkurrenten schon längst geschehen. So hatte YMTC bereits bei seiner „XTacking“-Architektur darauf vertraut, Kioxia und Western Digital folgten jüngst mit ihrem BiCS8-Flash.

Das Waferbonden beschreibt einen Herstellungsschritt, bei dem zwei Silizium-Wafer vollflächig miteinander verbunden werden. Im Falle des 3D-NAND werden die Chip-Logik (I/O) und der Speicherbereich zunächst getrennt voneinander auf separaten Wafern gefertigt und erst später zu einem Speicherchip vereint. Obwohl somit zwei Wafer benötigt werden, sollen die Kosten insgesamt nicht steigen, da sich auf diesem Weg die Speicherdichte erheblich steigern lässt, sodass es sich rentiert.

Samsung wird 3xx Layer voraussichtlich überspringen

Es gab bereits Gerüchte, dass Samsung von seinem 286-Layer-NAND der Generation V9 direkt auf über 400 Layer gehen wird und so die 3xx-Layer überspringt. Von 430 Layern bei Samsung V10 war die Rede. Die angesetzte ISSCC-Präsentation untermauert diese Annahme nun weiter.

SK Hynix hatte wiederum kürzlich seinen 321-Layer-TLC-NAND in die Massenfertigung entlassen.

2-Tbit-QLC mit 321 Layern bei SK Hynix

Die höchste Speicherkapazität (nicht Dichte) bei 3D-NAND bieten aktuell Kioxia und Western Digital mit dem BiCS8-QLC-NAND der 2 Tbit pro Die aufweist. Diese Speicherkapazität will bald auch SK Hynix mit seiner QLC-Variante des 321-Layer-NAND liefern. Der QLC-NAND soll zudem auf Chipebene eine Schreibrate von 75 MB/s erreichen. Das ist für QLC-Speicher sehr schnell. Die 60 MB/s bei Kioxias BiCS6 QLC galten vor zwei Jahren schon als rasant.

A 321-Layer 2Tb 4b/cell 3D-NAND-Flash Memory with a 75MB/s Program Throughput

SK Hynix für die ISSCC 2025

Effizienter TLC bei Kioxia

Bei Kioxia und Western Digital steht wiederum die Energieeffizienz im Fokus. Die kommende ISSCC-Session trägt den Namen „A 1Tb 3b/cell 3D-Flash Memory with a 29%-Improved-Energy-Efficiency Read Operation and 4.8Gb/s Power-Isolated Low-Tapped-Termination IOs“. Es geht also um einen neuen TLC-Speicher mit 3 Bit pro Zelle und 1 Tbit pro Die, der beim Lesen 29 Prozent effizienter arbeiten soll. Was hier genau miteinander verglichen wird, bleibt abzuwarten.