Advanced Packaging: Intel will mit neuer Technologie TSMC-Kundschaft abwerben

Foveros-S ist der neue Name für Intels Gegenspieler zu TSMCs CoWoS-S. Intel offenbart viele Gemeinsamkeiten auch bei zukünftigen Lösungen mit riesigen Packages und hofft so auf mehr Kundschaft. Denn während TSMC stets Kapazitätsmangel hat, hat Intel nicht ausgelastete, leere und nicht zu Ende gebaute Packaging-Komplexe.

Bisher packt Intel nur für Intel – auf kleiner Flamme

Bereits im März dieses Jahres hatte Intel zu einem Pressecall geladen und dort erklärt, man würde gern für andere Hersteller das Packaging von Chips übernehmen. Denn man habe freie Kapazitäten, während TSMC dieser stetig hinterher rennen muss und sie ohne die vielen Neubauten nicht bedienen kann. Doch bisher scheint diese Rechnung für Intel nicht aufzugehen, der vermeintliche Vorteil, den Intel bieten würde, ist wohl zu klein. Und so wurden Intels Ausbaupläne zum Teil gestoppt, vor allem in Malaysia wird viel Kapazität langsamer errichtet. Heute heißt es in der Roadmap, die gesteigerte Kapazität könne bei Bedarf in zwei Jahren abgerufen werden.

Neue Lösungen zielen auf TSMC

Den möglichen Bedarf will Intel auch mit neuen Lösungen schüren. Foveros-S ist dabei das bisherige 2,5D-Modell, welches nun mit ähnlich klingendem Namen wie TSMCs CoWoS-S das Basis-Packaging übernimmt. Klassische 1:1-Vergleiche sind bei den weiteren Produkten nicht ganz so leicht. Bei TSMC übernimmt aktuell bereits CoWoS-L mit RDL-Interposer, hierfür legt Intel Foveros-R auf. Es folgt bei Intel zudem Foveros-B mit zusätzlichen integrierten Schaltungen – wie Foveros-R aber frühestens ab 2027.

Das beste Produkt bleibt Foveros Direct 3D, welches auf Hybrid Bonding setzt. Hier hat TSMC ebenfalls einen großen Vorsprung: SoIC, wie es beim AMD Ryzen X3D genutzt wird, ist bereits seit Jahren alltagstauglich und geht in diesem Jahr in die nächste Generation über.

Große Stücke setzt Intel auch weiterhin auf EMIB, jene kleinen Chips, die auf dem Interposer für die Verbindung zwischen den darauf liegenden Compute-, I/O- und Speicherbausteinen herstellen. Dabei geht es vor allem um die Skalierung: Groß, größer und noch größer ist hier die Ansage von Intel. Je größer zukünftige Packages werden, desto deutlicher steigt deren Anzahl, auf den Folien gab es bereits Lösungen mit über 38 dieser kleinen Kommunikationsverbindungen. Mit EMIB-T wird den Silizium-Verbindungen in Zukunft auch die TSV-Möglichkeit gegeben, unter anderem, um schneller Speicher wie HBM4 und später HBM5 besser ansprechen zu können.

Mit EMIB hat Intel in der Vergangenheit sowohl schlechte als auch gute Erfahrungen gemacht. Auf der einen Seite löste es zwar gewisse Probleme, war aber auch kein Allheilmittel, wie etwa beim Server-Prozessor Intel Sapphire Rapids. Vier-CPU-Dies plus das Drumherum damit zu verschalten, brachte Probleme wie auch einen viel zu hohen Stromverbrauch, der durch die ständigen Transporte über die zehn EMIB-Chips verursacht wurde, letztlich aber keine Leistung brachte.

Der Nachfolger Intel Emerald Rapids verzichtete daher auf viele EMIB-Bausteine, es ging zurück zu größeren Einzelchips in nur zweifacher Form. Ponte Vecchio als bisheriges Monster mit 47 Chips, viele davon EMIB, war auch nur ein Aushängeschild fürs Packaging, nicht aber als Produkt – es floppte komplett.

Bei großen HPC-Chips ist der Stromverbrauch zwar auch ein Thema, bei den riesigen Interposern, mit von Intel sogar geplanten 120 × 180 mm – und somit mehr als TSMCs 120 × 150 mm – dürfte ohnehin ein Verbrauch weit jenseits der 1.000 Watt die Regel sein.

Bisher war EMIB aber ein Intel-exklusives Feature. In Zukunft wird jedoch Amkor als einer der großen Packaging-Mitbewerber im Markt, ebenfalls EMIB im Assembly im Angebot haben.

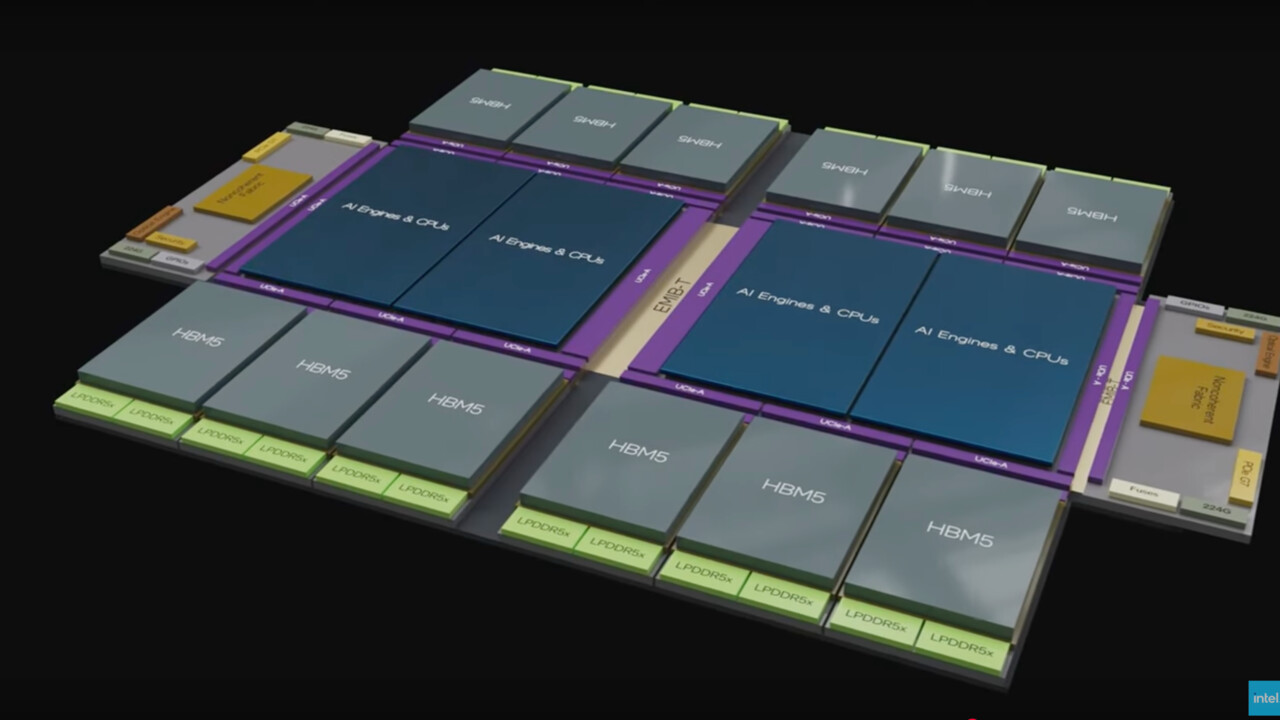

Wie dies am Ende in einem Produkt aussehen könnte, verdeutlicht eine Animation. Intel 18A-PT als neuer modernster Base-Die fasst unzählige Chips und Speicher und verbindet diese mit den genannten Technologien, oben drauf sitzt ein AI-Chip aus der Fertigung Intel 14A oder gar schon Intel 14A-E – und am Ende wird dieser mittels EMIB-T noch mit einem zweiten solchen Chip verbunden. Skalierung ist hier letztlich erneut das Stichwort.

Auch am Thema optische Verbindung kommt Intel natürlich nicht vorbei. Dies wird als heiße Lösung für die Zukunft gehandelt, es gibt da aber viele Herausforderungen. Schon seit Jahren gehen viele Träume letztlich in die Richtung, eine Umsetzung wird aber auch noch Jahre dauern.

Zum Abschluss zeigte Intel auf der Bühne zumindest ein Mockup-Package. Gemäß Insidern entspricht dieses zu 99 Prozent Intel Falcon Shores, das Intel kürzlich als kommerzielles Produkt abgesägt hatte, es wird jedoch intern für Tests genutzt – dazu passt dann durchaus auch, dass man es öffentlich zeigen kann.

Am Ende ist die Erkenntnis im Bereich Packaging bei Intel aber die gleiche wie bei den gezeigten Fertigungsschritten. Ankündigungen müssen Taten folgen, und dann auch Kundschaft. Diese gibt es beim Packaging bisher nicht, vieles läuft bei Intel in dem Bereich deshalb auf Sparflamme. Auch hier sehen die zukünftigen Möglichkeiten in Präsentationen gut aus, viele kommen aber erst 2027, 2028 oder noch später. Das in drei, vier Jahren viel passieren kann, haben wiederum die letzten drei, vier Jahre einmal mehr eindrucksvoll gezeigt. Das war zum Beispiel die Lebensdauer eines Pat Gelsinger als Intel-CEO.

Weitere Berichte vom Event: