High-NA EUV im Teststatus: Neue ASML-Scanner laufen bei Intel besser als erwartet

Gleich mehrfach hat Intel in den vergangenen Tagen über den Status von High-NA EUV informiert. Die beiden ersten Tools, die in Intels Forschungsfabrik stehen, laufen sehr gut und liefern zum Teil Ergebnisse, die die Erwartungen übertreffen. Der Einführung bei Intel 14A steht bisher nichts im Weg.

Das originale EUV, nun Low-NA EUV genannt, hatte zur Einführung diverse Schwierigkeiten. Die Leistungsfähigkeit war zu gering, die Ausfallzeiten viel zu hoch, der Ausstoß sehr klein. Dies konnte zu Beginn jedoch großflächig aufgefangen werden, da oft nur wenige Layer mit EUV belichtet wurden und die Wafer schnell wieder zu klassischen DUV-Systemen wechselten. Dies war damals einer der Gründe, warum Intel dachte, es gehe ohne EUV. Dies besserte sich in vielen Revisionen und Optimierungen über die Jahre hinweg aber stark, um stetig mehr Layer mit EUV zu belichten. Doch bei Intel lief es nicht rund und aktuelle Gerüchte aus Asien besagen, dass es Intel mit EUV auch bei Intel 18A noch passieren könnte, erneut werden nur 20 bis 30 Prozent Ausbeute bei Panther Lake genannt – zuletzt hatte Intel diese Angaben stets dementiert.

ASML hat bei EUV viel gelernt

ASML als Fabrikant dieser Systeme hat aber viel gelernt, das hatte sich schon angedeutet. Mit den ersten beiden High-NA-EUV-Tools, die bei einem Kunden installiert sind, werde dies unter Beweis gestellt. Und laut Intel, die der Erstkunde sind und nicht noch einmal auf die Nase fallen möchten, hat ASML nicht zu viel versprochen, es werden sogar Erwartungen übertroffen.

Wie unter anderem auch Reuters von der SPIE-Konferenz berichtet, sind die neuen Systeme mehr als doppelt so zuverlässig wie EUV-Systeme zur Einführung. Auch liefert die neue Lichtquelle mehr als zuvor erwartet wurde, dies ermöglichte deshalb schnelle Testreihen, die schon jetzt eine hohe Konsistenz beim Wafer-Ausstoß zeigen. Insgesamt wurden bereits 30.000 Wafer High-NA-EUV ausgesetzt, wobei ein Großteil davon auch simulierte Wafer sein dürften, üblicherweise wird nur ein Bruchteil auch wirklich vollständig belichtet, da dies schnell die Kosten sprengen würde.

Bereits vor knapp einer Woche hatte Intel im Rahmen einer weiteren Konferenz High-NA EUV gelobt. Ab Minute 11:50 ist dies auch auf YouTube zu finden. Dabei erklärte Intel, dass High-NA EUV viele Prozessschritte vereinfache, statt drei Belichtungen und 40 Einzelschritten mit klassischem EUV vorzunehmen, gelinge dies mit High-NA EUV in einem Durchgang. Ziemlich ähnlich sah es damals aus, als der Wechsel von DUV zu EUV vollzogen wurden, statt Multi-Patterning und Multi-Exposures in extremen Ausmaß ging mittels EUV alles in deutlich weniger Schritten. Dies verringert die Fehleranfälligkeit deutlich und steigert so die Ausbeute. Mit High-NA EUV wird dies nun auf das nächste Level gehoben.

Nach den ersten zwei Systemen bei Intel soll TSMC zum Jahresende 2024 das dritte Tool erhalten haben. Auch dort wird der Start dieser Lösungen in der Produktion in den kommenden Jahren nun vorbereitet.

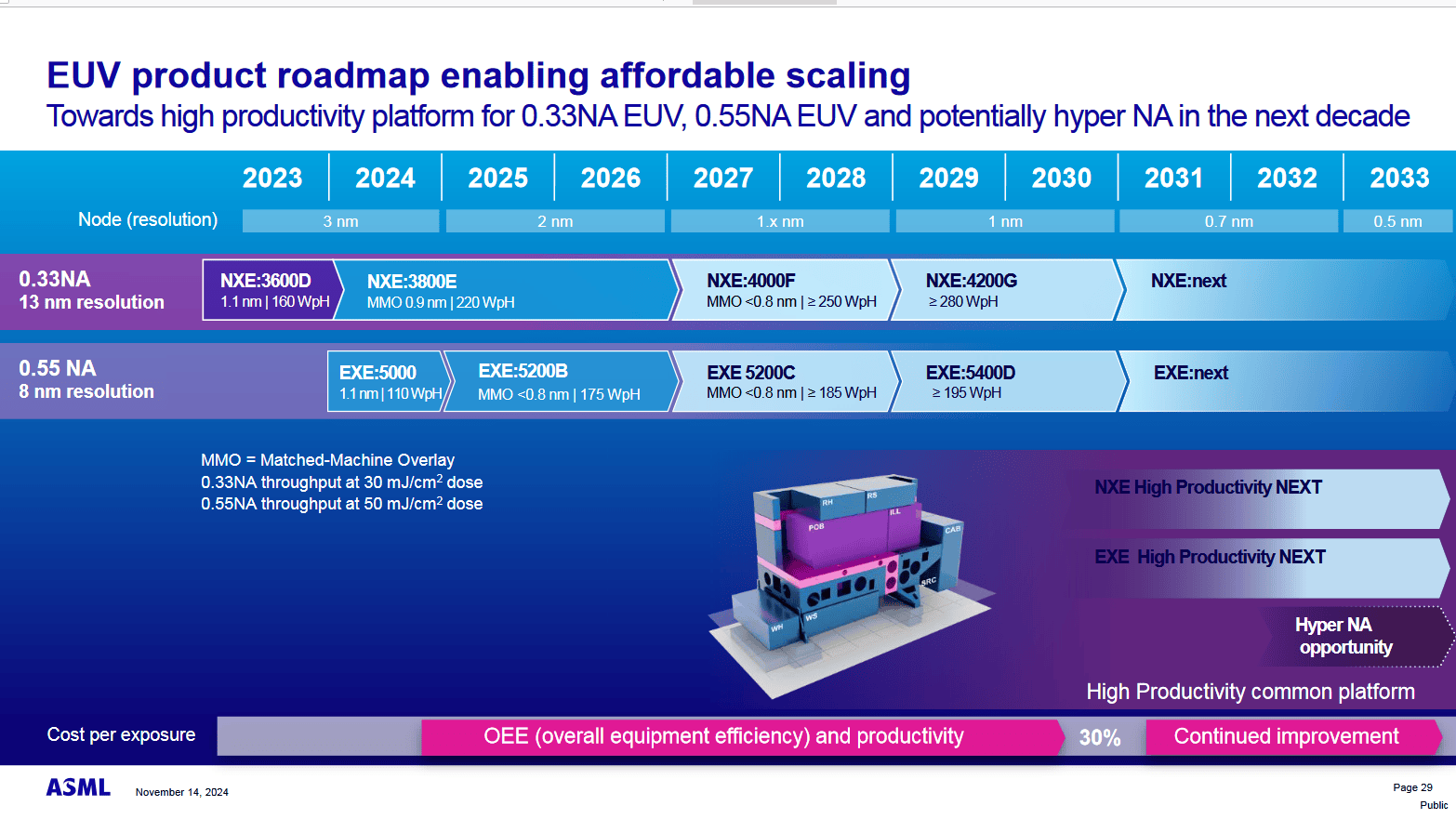

Aktuell entsprechen die Tools noch dem Forschungsstandard. In diesem Jahr wird es jedoch bereits ein Update geben, das die Maschinen auf ein Niveau nahe der Produktion bringt. Alle ASML-Systeme sind immer vollständig upgradebar, selbst die allerersten Systeme werden so nach und nach auf vollen Produktionsstandard aufgerüstet. Dieser wird spätestes 2027 mit den EXE:5200C erreicht sein.