AMDs Spider-Plattform im Test: CPU + Chipsatz + Grafikkarte

2/6Die CPU: Phenom

Bereits im November 2006 erblickte der erste Quad-Core-Prozessor für den Desktop-Bereich das Licht der Welt – der Chip hatte den Codenamen Kentsfield und kam aus dem Hause Intel. Nach nun gut einem Jahr will AMD mit einer eigenen Quad-Core-Kreation namens Phenom (Codename Agena) der Konkurrenz die Stirn bieten.

Grundlegend verschieden ist allerdings der Realisierungsansatz: während man bei Intel zwei Dual-Core-Prozessor-Dies (Core 2 Duo, Codename Conroe) zusammen auf einem Prozessorgehäuse (Multi-Chip-Package, MCP) gekoppelt hat, ist man bei AMD – aus eigener Sicht – einen Schritt weiter und bietet einen nativen Quad-Core-Prozessor an. Entwickelt wurde der Phenom in Austin, Texas. Gefertigt wird er im 65-nm-Prozess in Dresden. Im Laufe des nächsten Jahres möchte man dann – wie bei Intel bereits Gang und Gäbe – auf den 45-nm-Lithographieprozess umschwenken.

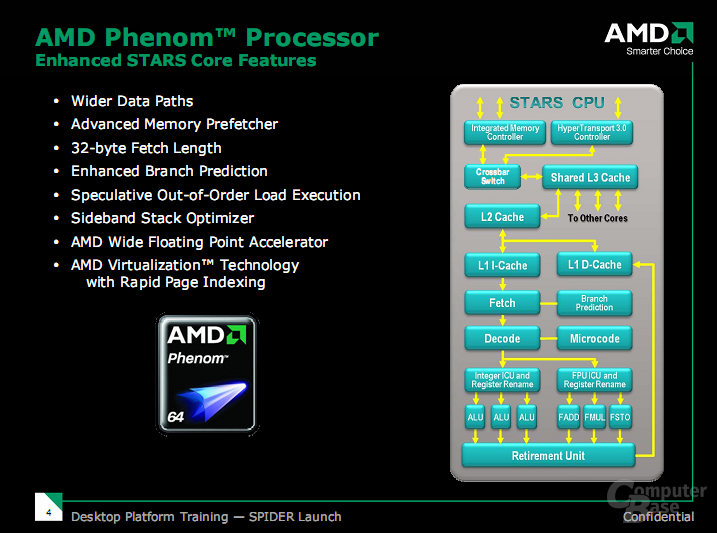

Die TDP des Phenom 9500 und 9600 liegt bei 89 Watt. Jeder einzelne Kern verfügt über 512 KB L2-Cache. Zusätzlich verfügt der gesamte Prozessor über einen Shared-L3-Cache mit 2 MB, der von den Kernen gemeinsam genutzt wird. Allerdings hat AMD was die Speicherhierarchie angeht in die Trickkiste gegriffen. So können die L1-Cache-Prefetcher Daten ohne den sonst üblichen Umweg über den L2- und L3-Cache Daten aus dem Arbeitsspeicher anfordern.

Die prozessorinternen Datenpfade wie auch die Ausführungseinheiten für SSE und FPU wurden von bisher 64 Bit auf 128 Bit (wie bei Intels Core Mikroarchitektur) verdoppelt. Damit können SSE-Befehle nun innerhalb eines Takts bearbeitet werden. AMDs Architektur erlaubt die Ausführung von zwei SSE-Befehlen parallel – Intel ist mit drei Execution-Ports für SSE jedoch weiterhin eine Nasenlänge voraus (nicht alle Ports können alle SSE-Befehle ausführen). Der Instruction-Fetch-Buffer des Phenoms wurde auf eine Breite von 32 Byte erweitert. Damit passen mehr x86-Befehle, die zwischen drei und 15 Byte lang sind, in den Instruction Fetcher, dem ersten Teil der Befehlspipeline. Dies stellt auch bei den längeren 64-Bit-Befehlen (im Schnitt ca. 4,5 Bytes) sicher, dass der weiterhin 3fach-superskalere Prozessor mit genügend Befehlen zur Verarbeitung versorgt wird. Intels Pipeline-Frontend liest (seit dem Pentium Pro) nur 16 Byte aus dem Instruktion Cache und läuft damit hochgradig Gefahr, insbesondere bei 64-Bit-Code, den 4fach-superskalaren nicht mit genügend Arbeit versorgen zu können.

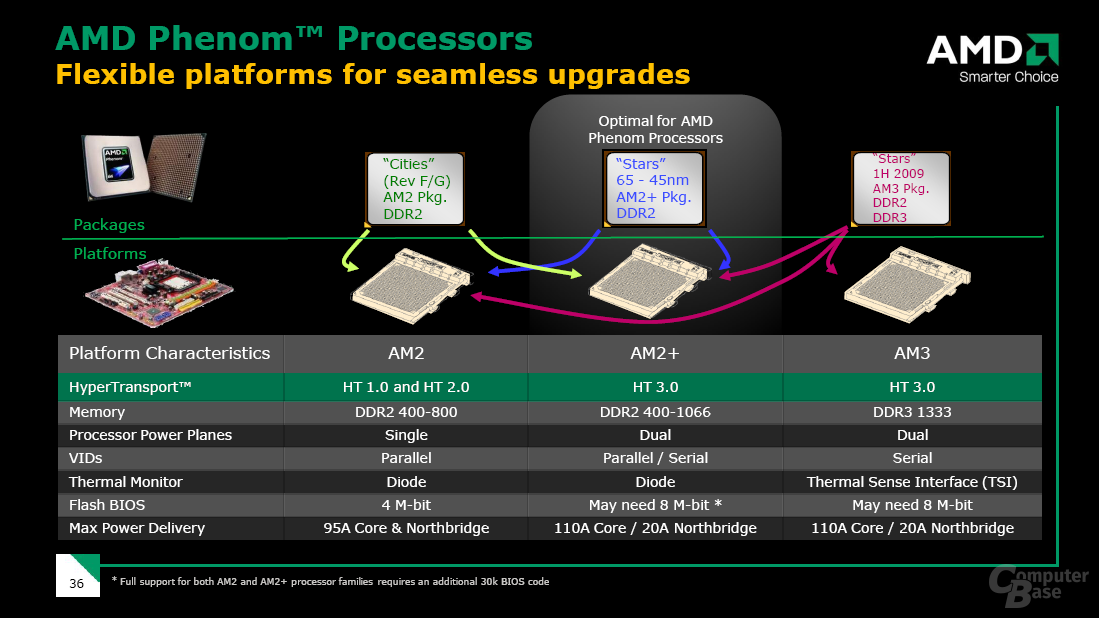

Auch die Sprungvorhersage wurde von AMD verbessert und mit einer neuen Logik versehen. Eine treffsichere Sprungvorhersage ist wichtig, da moderne Prozessoren mehrere Instruktionen parallel verarbeiten und ein Sprung (Branch), der sich nicht wie vorhergesagt verhält, die anderen auf Verdacht parallel ausgeführten Instruktionen hinfällig macht. Die Virtualisierungstechnik wurde dahingehend verbessert, dass der Hypervisor den Gastsystemen deren Speicherseiten schneller zur Verfügung stellen kann. Die Geschwindigkeit des bei AMD weiterhin integrierten Speichercontrollers wurde von bisher DDR2-800 auf DDR2-1066 gesteigert. Der im Silizium enthaltene Funktionsblock unterstützt auch DDR3 bis 1600 MHz (effektiv). Hiervon macht AMD jedoch noch keinen Gebrauch.

Mit dem Phenom macht AMD auch den Schritt zum Industriestandard HyperTransport 3.0 (HT 3.0), der deutlich höhere Bandbreiten bietet. Bis zu 20,8 GB/s kann diese Hochgeschwindigkeitsverbindung theoretisch übertragen. Der Phenom kann davon laut AMD zur Zeit bis zu etwa 18 GB/s nutzen und mit höheren Taktraten sollen diese Werte noch steigen. Bei alledem bleibt der Phenom abwärtskompatibel zum älteren HyperTransport 1.0 mit lediglich etwa 6,4 GB/s Bandbreite.

AMD hat sich auch um den Energiebedarf des Phenom Gedanken gemacht. Als „Split-Power-Lane“ bezeichnet AMD die Möglichkeit, den Speicher-Controller und die CPU-Kerne mit zwei unabhängigen Spannungen zu versorgen. Mit dem Power-State C1E, den der Phenom nun auch unterstützt, erfüllt AMD die seit Mitte des Jahres gültigen Energy-Star-4.0-Vorgaben.

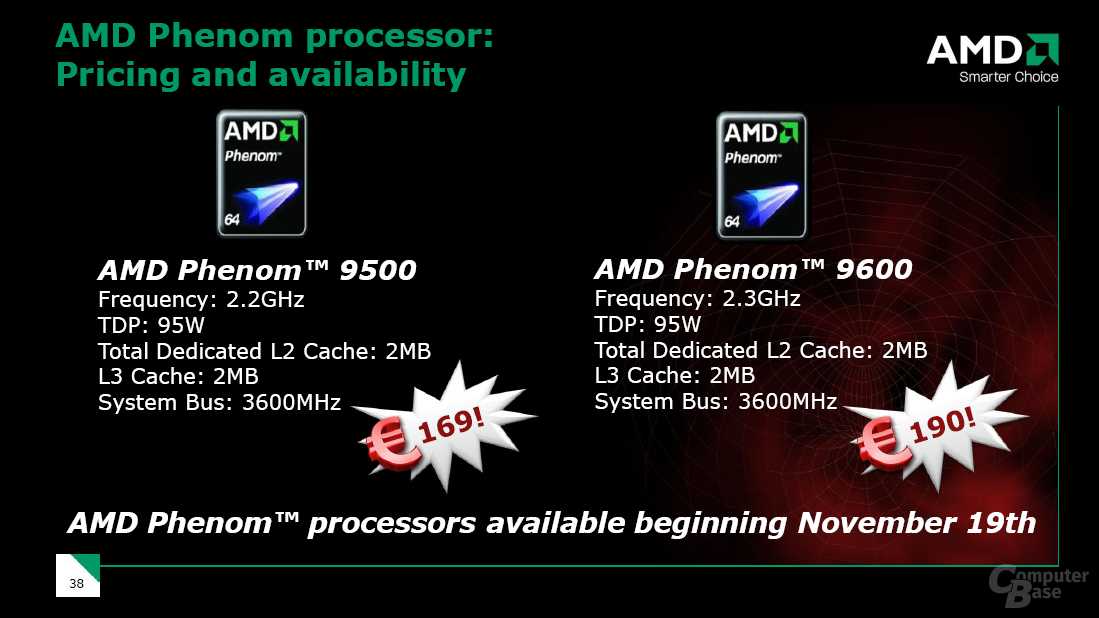

Nun ist der Phenom für viele Nutzer von Preisvergleichdiensten kein Neuling mehr. Bereits seit Tagen werden die neuen CPUs von unterschiedlichen Händlern gelistet, natürlich ohne jedwede Verfügbarkeit. Viel interessanter ist jedoch die Preisgestaltung dieser verfrühten Angebote. Während aktuell (18.11.) der Phenom 9500 ab 219,- Euro angeboten wird und der Phenom 9600 stolze 245,- Euro kosten soll, wird der heute gar nicht eingeführte Phenom 9700 (siehe nächster Absatz) für 259,- Euro präsentiert. Ohne viele Worte wollen wir an dieser Stelle einfach die der Presse präsentierte Preisgestaltung von AMD zeigen.

Zu guter Letzt wollen wir den Lesern nicht verschweigen, wieso der geplante und eben bereits erwähnte Phenom 9700 laut AMD wohl erst im Januar 2008 auf den Markt kommen wird. Schuld ist ein Fehler im Prozessor, ein Errata. Solche Fehler sind bei solch einem komplexen Objekt wie einem Mikroprozessor nichts Neues. Auch der altbekannte Pentium war durch solch einen Fehler geplagt und auch in Core 2 und Athlon 64 schlummern viele Fehler, die nur unter sehr seltenen Konstellationen ein Problem bedeuten. Nach Aussagen von AMD tritt der Fehler nur in extrem seltenen Fällen unter Volllast und bei hohen Taktfrequenzen des Prozessors auf. Auf Nachfrage erklärte uns Dave Everitt das es sich um einen Fehler im TLB des L3-Cache handeln soll.

Der TLB sorgt für die performante – da in Hardware als Cache implementierte – Konvertierung der von Anwendungen verwendeten virtuellen Speicheradressen in physische Speicheradressen. AMD möchte ein Tool und/oder BIOS-Update bereitstellen, mit dem der TLB des L3-Cache abgeschaltet werden kann. Das Abschalten des TLB führe zu einem Leistungsverlust von etwa zehn Prozent.