Intel-Technologien: Details zu 10 nm, 22FFL, EMIB, MCPs und 450-mm-Wafern

Intels Technology and Manufacturing Day war auch ein Tag der Abkürzungen: 10++, 22FFL, EMIB, MCP und 450-mm-Wafer sind nur einige der Begriffe, die da gefallen sind. Hinter allen stecken neue technische Errungenschaften, die in den kommenden Jahren genutzt werden. Einige Details im Überblick.

Mit EMIB zu mehr MCPs

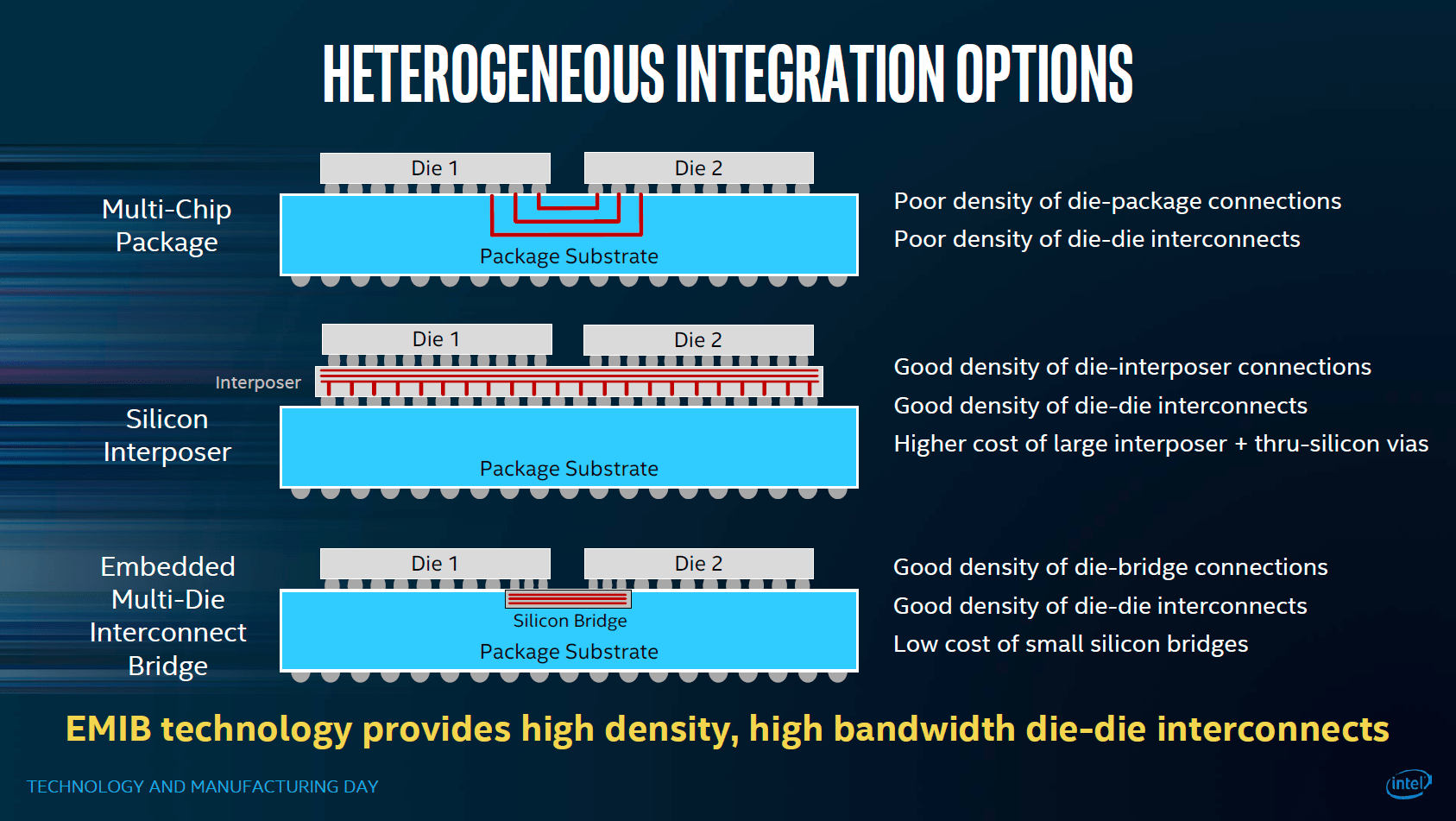

Seit Jahren reißt Intel das Thema immer mal wieder an, verrät jedoch nie Details – bis jetzt. Die Rede ist von EMIB, der Embedded Multi-Die Interconnect Bridge. Im einfachsten Sinne ist es die Verbindung zwischen zwei Chips auf einem Package, dem Multi-Chip-Package (MCP). Die Besonderheit liegt jedoch in den Tiefen der Technik. Denn während erste Lösungen von MCPs einfach über einige Leitungen im Package gelöst wurden, nahm der Hochleistungszug ein wenig später Fahrt auf.

Das beste und bisher einzige Produkt in Massenfertigung dafür ist AMDs Fury-Generation: Für den Fiji-Grafikchip wurden auf einem Package der eigentliche Grafikchip mit HBM verbunden. Dafür wurde ein Interposer genutzt, der unter anderem dank Thru-Silicon Vias (TSV) eine sehr gute Transferrate bietet, jedoch separat und teuer gefertigt werden muss.

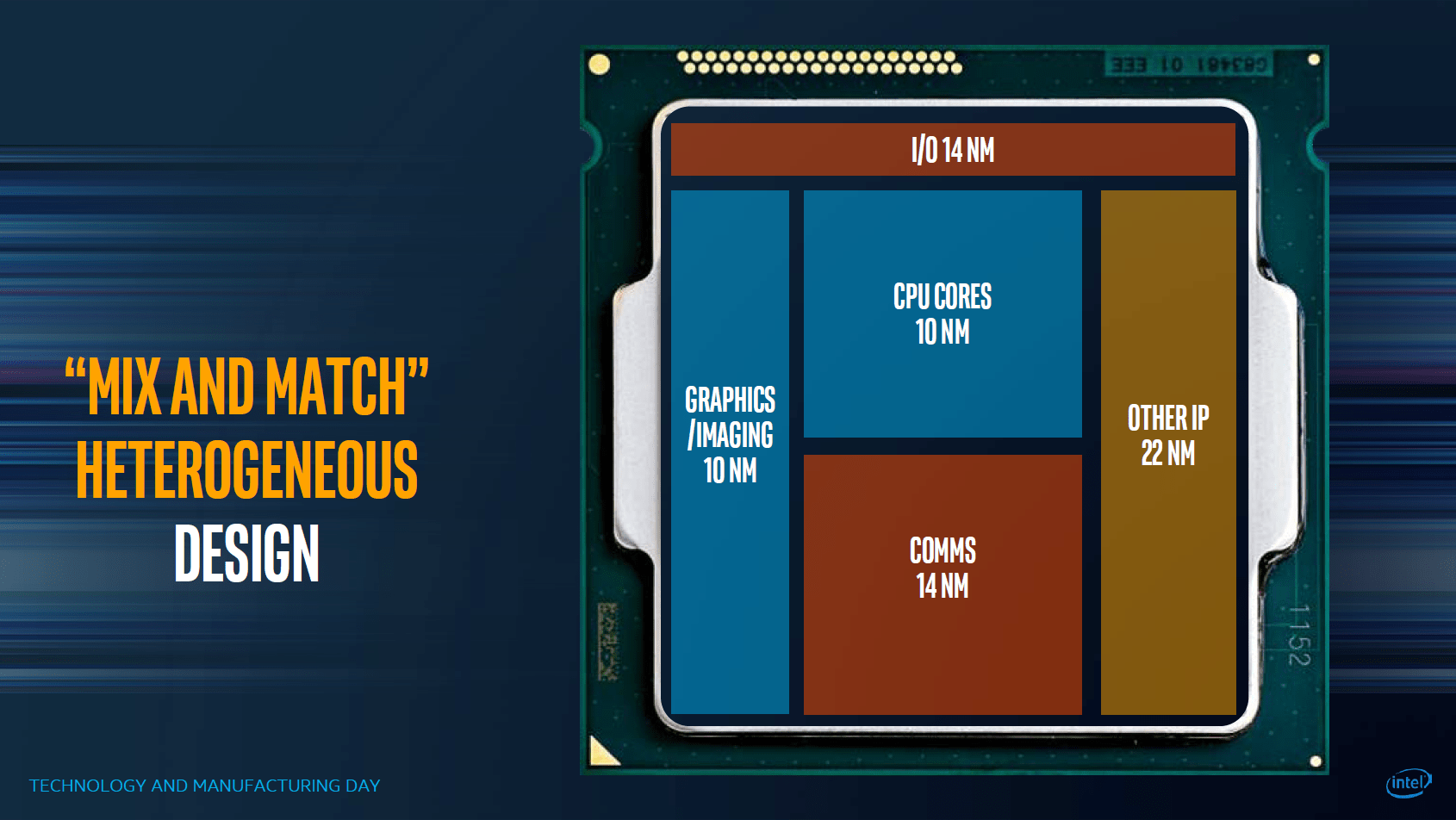

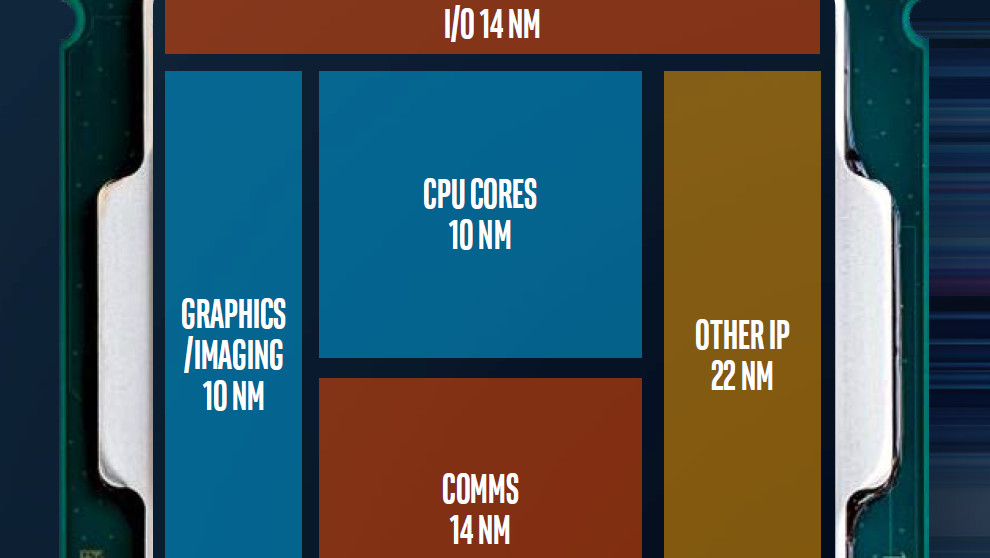

Die Embedded Multi-Die Interconnect Bridge schnappt sich viele dieser vorangegangenen Ideen und Lösungen und kombiniert sie. Die Leitungen liegen nun wieder direkt im Package – der zwischen geschaltete Interposer entfällt. Dies hat natürlich einen deutlichen Kostenvorteil, zudem konnte die Bandbreite nochmals gesteigert, der Platzbedarf zudem verringert werden. Dadurch lassen sich in Zukunft mehr MCPs realisieren, wie Intel an einem fiktiven Beispiel erklärt. Während der Prozessor selbst und die Grafikeinheit in 10 nm gefertigt werden, werden andere Komponenten in 14 oder gar noch 22 nm hinzugebracht – in diesem Zusammenhang bestätigte Intel, dass die Plattform Controller Hubs (PCH), umgangssprachlich weiterhin Chipsatz genannt, ab 2018 in 14 nm gefertigt werden. Am Package ändert dies nichts, alles verschwindet am Ende ohnehin unter einem Heatspreader.

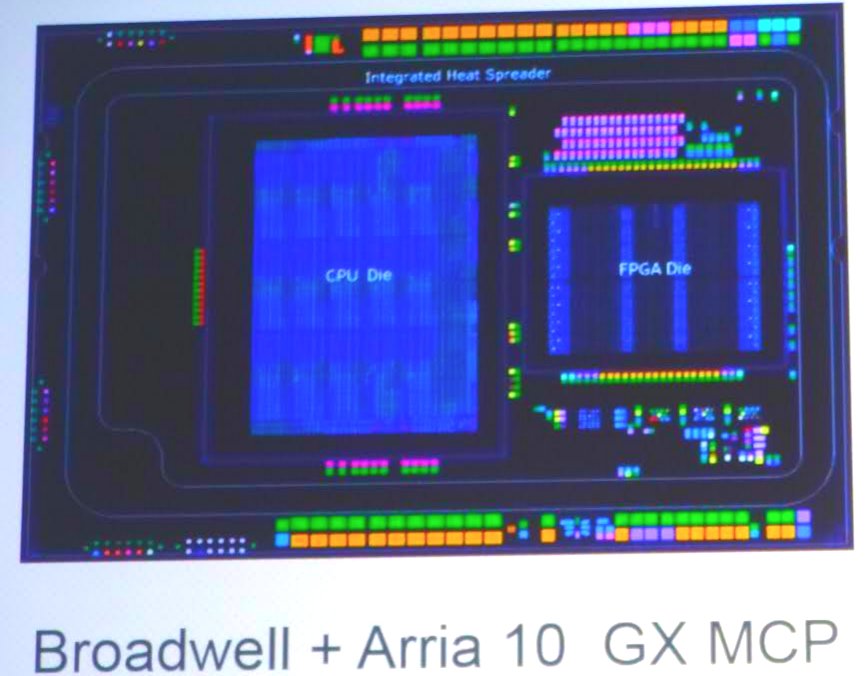

Die erste Lösung von Intel wird mit dem Arria 10/Stratix 10 genutzt, nach dem Kauf von Altera wird dieser unter Intels Namen vermarktet. Beim Arria treffen Xeon-Kerne auf den FPGA und bilden ein Multi-Chip-Package – dies hatte Intel erstmals vor einem Jahr gezeigt. Der Stratix 10 hingegen ist ein reiner FPGA, der mit Speicher auf einem Package kombiniert ist.

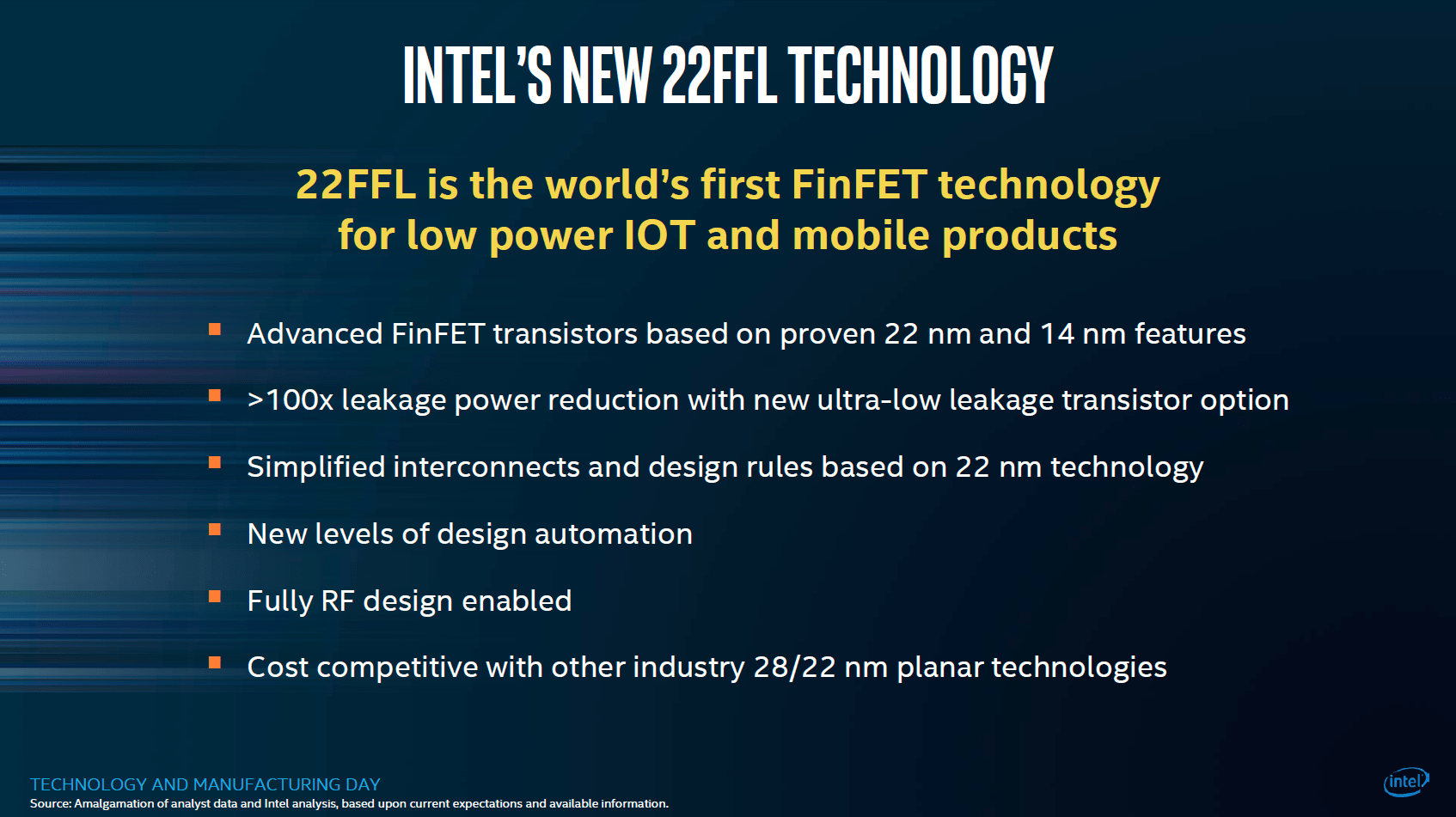

22FFL für IoT, Automotives und Smartphones

Das Rennen als Auftragsfertiger gibt Intel auch 2017 nicht auf, obwohl der Konzern dort bisher keinen richtigen Fuß in die Tür bekommt und alle großen Hersteller bisher den Gang zu Intel vermeiden – zu umständlich, zeitaufwändig und teuer heißt es hinter vorgehaltener Hand. Bereits im Sommer 2016 wurde deshalb auch ARM mit ins Boot geholt, jetzt wurde die Partnerschaft noch einmal beteuert. Denn der extra dafür angepasste neue Fertigungsprozess ist genau für eben jene Märkte, in denen ARM nahezu 100 Prozent Marktanteil besitzt.

22FFL steht für eine FinFET-Low-Power-Variante der 22-nm-Fertigung, die sich an der originalen 22-nm-Produktion bei Intel orientiert, aber viele Erkenntnisse und auch Verbesserungen der aktuellen 14-nm-Fertigung einfließen lässt. Heraus kommt am Ende ein Hybride mit besonders gutem Verhalten bei der Leistungsaufnahme, aber dennoch sehr hoher Leistungsfähigkeit, so wie es in den Bereichen Internet of Things, Automotive und im Smartphone gewünscht wird. Der neue Prozess soll als günstige Lösung im Vergleich zu den 22/28-nm-Prozessen von Globalfoundries, Samsung und TSMC fungieren und Ende 2017 einsatzbereit sein. Ob das Intels Foundry-Geschäft zu mehr Aufträgen verhilft, bleibt abzuwarten.

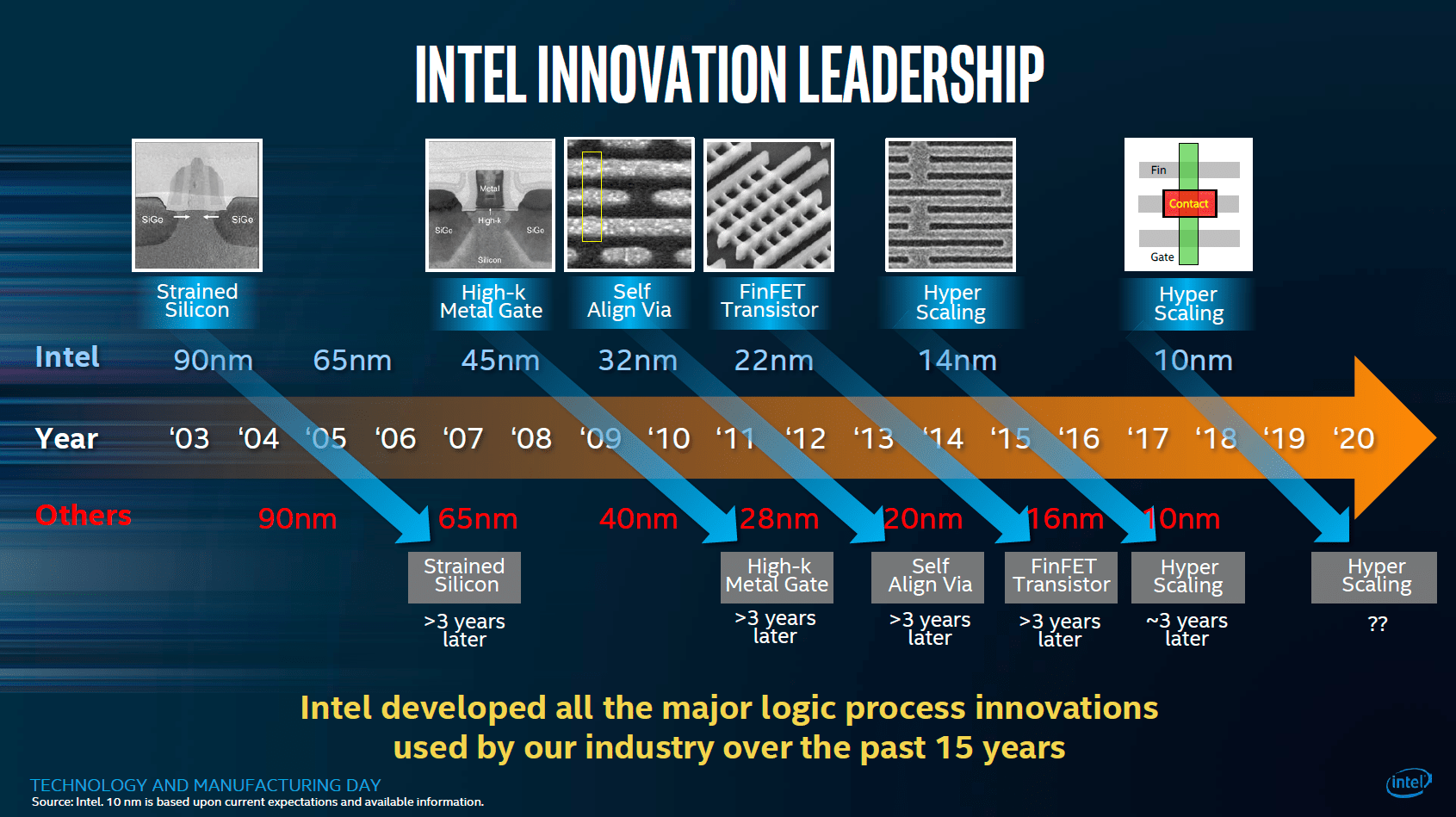

10 nm: Vorsprung auf die „kopierende“ Konkurrenz

Mit einem kleinen Rückblick eröffnete Intel den Reigen zu den Ausführungen der neuen 10-nm-Fertigung. Intel zufolge habe das Unternehmen in den letzten 15 Jahren viele technologische Entwicklungen als erste in die Serienfertigung gebracht, die von anderen „kopiert“ wurden – namentlich nennt Intel die großen Auftragsfertiger TSMC, Globalfoundries und Samsung nicht, wenngleich eine Präsentationsfolie genau diese vier Unternehmen als einzig verbliebene im Markt deklariert.

Dies begann laut Intel mit Strained Silicon bei der 90-nm-Fertigung und ging über High-k Metal Gate bei 45 nm zu den ersten FinFETs in 22 nm. Viele davon sind aber nicht auf Intels Erfindergeist gewachsen, sondern stammen im Ursprung von anderen ab. Intel hat sie jedoch als erstes massentauglich gemacht, wie beispielsweise FinFETS, deren Idee bereits Jahrzehnte alt ist.

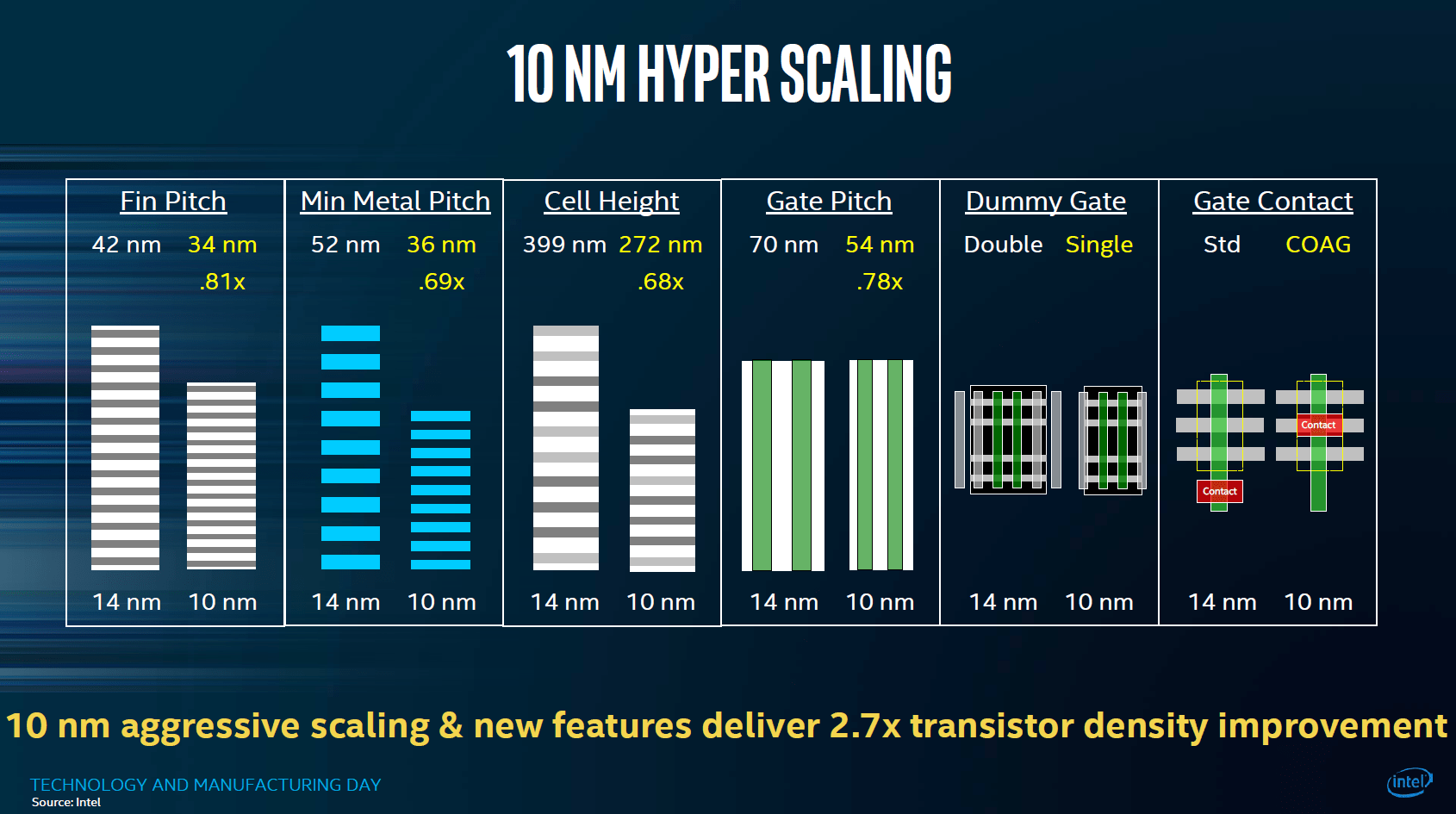

Bei der 10-nm-Fertigung will Intel die Konkurrenz weiterhin auf Abstand halten. Mit den Neuheiten Contact over Gate, in der die Kontaktstelle zukünftig über dem Transistor liegt, sowie dem Single Dummy Gate – statt bisher genutztem Double Dummy Gate – will Intel zusätzlichen Platz einsparen und so einen Vorteil bei der Flächennutzung für sich herausschlagen. Die Single Dummy Gates sind dabei aber erneut keine Erfindung von Intel, nur wurden sie niemals bei so kleinen Gate Pitches genutzt.

Zu Guter Letzt: 450-mm-Wafer

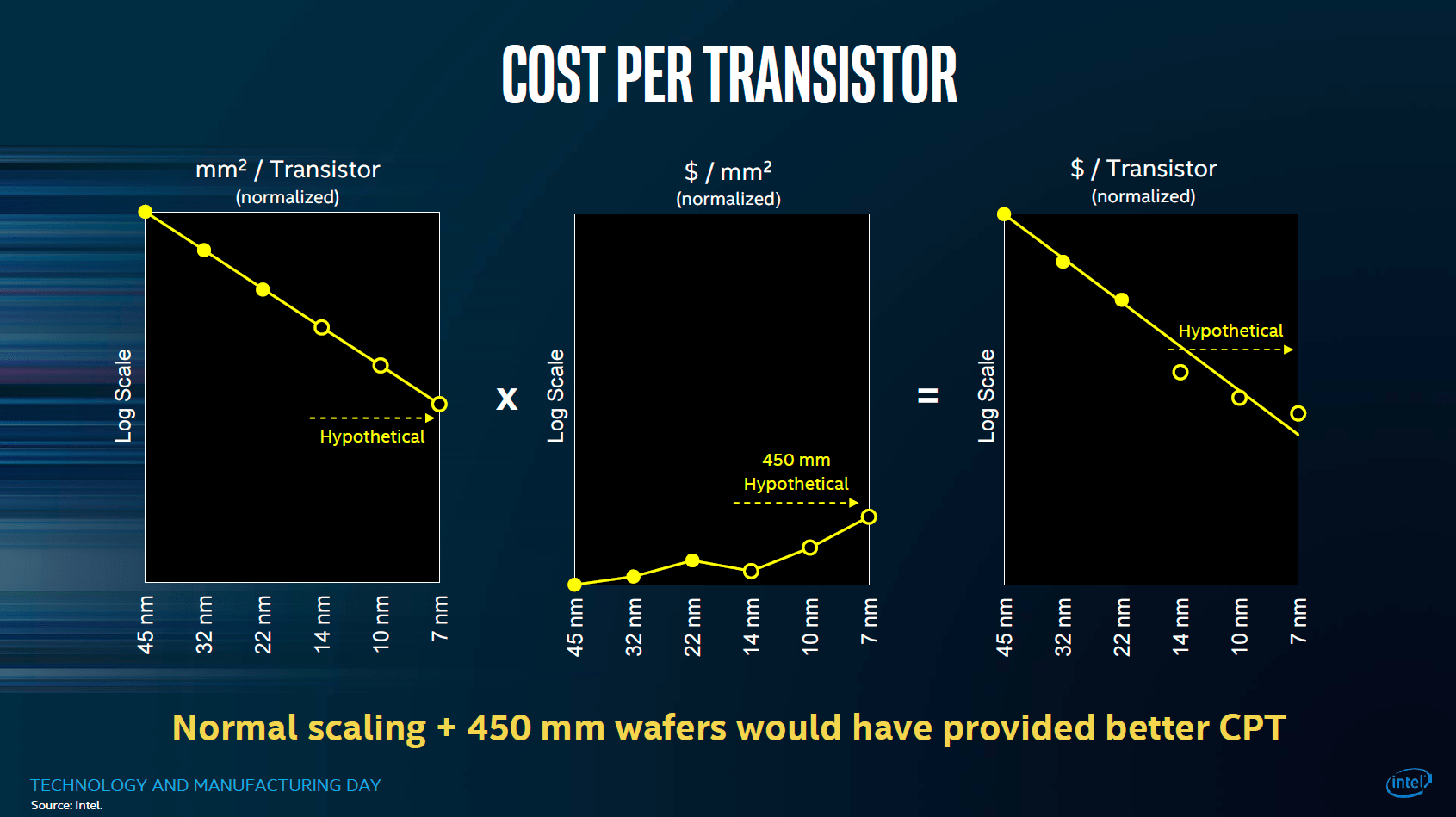

Natürlich kommt ein Fab-Day nicht ohne die nächste Ausbaustufe der Wafer-Fertigung aus: die 450-mm-Wafer. Wenngleich die Industrie von diesen abgerückt ist und ein Start somit in weiter Ferne liegt, werden die großen Wafer dennoch in theoretischen Rechnungen mit berücksichtigt. Bei der Frage nach den Kosten spielen diese immer wieder eine Rolle, da die höhere Ausbeute von den großen Scheiben einen positiven Effekt auf die Kosten gehabt hätte.

Laut Intels Aussagen wäre eine nicht weiter optimierte 14- und 10-nm-Fertigung mit 450-mm-Wafern auf ein ähnliches Verhältnis der Kosten pro Transistor gekommen. Ohne Optimierungen, die Intel Hyperscaling nennt, sowie den nicht vorhandenen 450-mm-Wafer würden die Kosten deutlich ansteigen.

Dass die 450 mm großen Wafer deshalb zu einem bestimmten Zeitpunkt doch noch kommen, sagt dies nicht aus. Jedoch besteht immer die Chance, sofern keine anderen Punkte zur Kostenersparnis eintreten.