X-NAND: Startup verspricht QLC-Kapazität mit SLC-Leistung

Das Unternehmen NEO Semiconductor hat auf dem Flash Memory Summit 2020 Details zum sogenannten X-NAND preisgegeben. Die neuartige NAND-Flash-Architektur soll bei einer Speicherdichte von QLC-Flash eine vergleichbare Leistung wie schneller SLC-Flash bieten.

NAND-Flash: Speicherdichte steigt, Leistung sinkt

Um immer mehr Bit pro Chip unterzubringen, die Speicherdichte also zu erhöhen und die damit verbundenen Kosten pro Bit weiter zu senken, wird bei NAND-Flash-Speicher die Zahl der gespeicherten Bit pro Speicherzelle kontinuierlich erhöht. Von SLC (1 Bit) über MLC (2 Bit) und TLC (3 Bit) ist man inzwischen bei QLC mit 4 Bit pro Zelle angelangt, Pläne zu Penta-Level Cell (PLC) mit 5 Bit wurden schon formuliert. Doch immer mehr Bit bedeuten, dass immer mehr unterschiedliche Spannungslevel innerhalb der Zelle vorliegen und unterschieden werden müssen. Bei QLC sind es bereits 16 dieser Level, mit PLC wären es schon 32. Dadurch wachsen unter anderem die Anforderungen an die Fehlerkorrekturmaßnahmen, die Haltbarkeit nimmt ab und der immer komplexere Speichervorgang senkt die Leistung.

Bei SSDs mit TLC- oder QLC-Flash kommt daher meist ein sogenannter Pseudo-SLC-Cache zum Einsatz: Daten werden im SLC-Modus zwischengespeichert, um temporär für schnelle Transfers zu sorgen. Doch zur dauerhaften Sicherung müssen die Daten (etwa in Leerlaufphasen) im regulären TLC- oder QLC-Modus geschrieben werden, was deutlich länger dauert. Spätestens die QLC-SSDs erreichen nach dem SLC-Cache etwa nur noch Transferraten auf HDD-Niveau. Für Anwendungen mit Dauerlast, ohne solche Idle-Phasen, eignet sich QLC-Flash daher kaum.

X-NAND verspricht hohe Speicherdichte und hohe Leistung

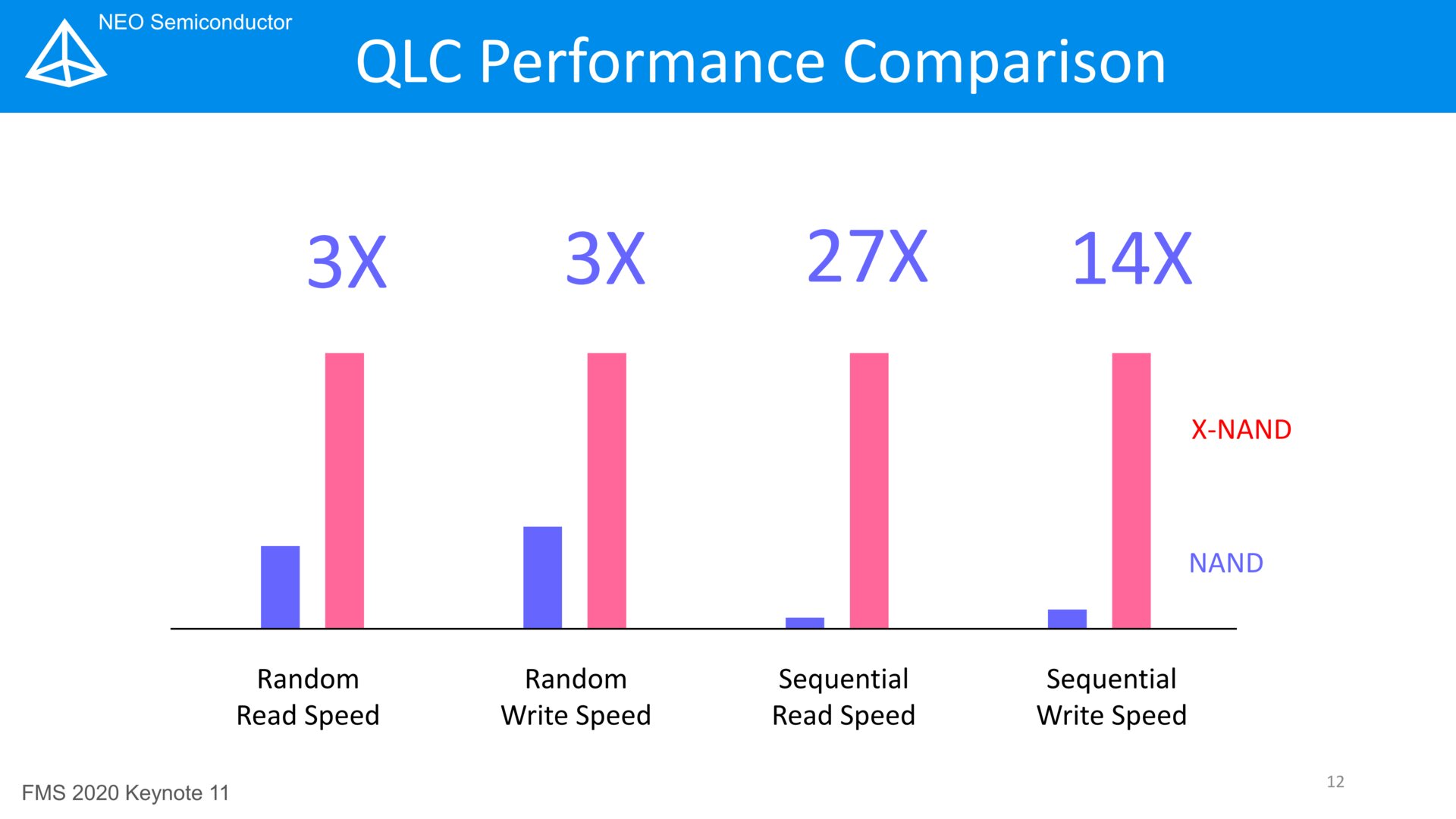

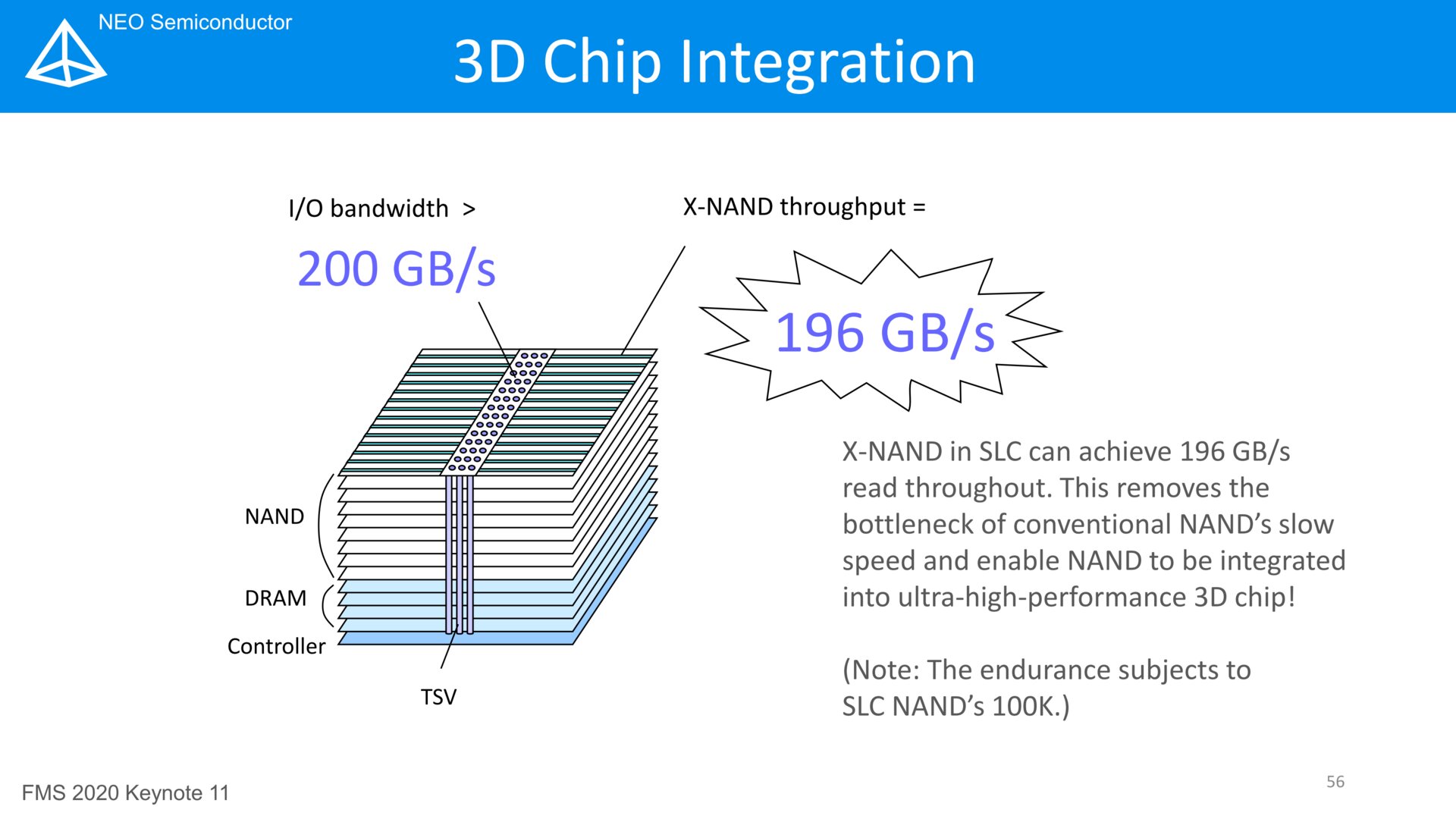

Mit dem X-NAND will NEO Semiconductor aus Kalifornien die niedrigen Kosten von QLC- mit der hohen Leistung von SLC-Flash kombinieren. Versprochen wird nicht weniger als die dreifache Geschwindigkeit beim wahlfreien Lesen/Schreiben (Random Read/Write), das sequenzielle Lesen soll um den Faktor 14 und das sequenzielle Schreiben sogar um den Faktor 27 beschleunigt werden. Die Mehrleistung soll es zudem quasi zum Nulltarif geben, denn die Fertigung soll nicht teurer als bisher ausfallen. Der X-NAND in QLC-Version soll sogar etwas schneller als herkömmlicher SLC-NAND arbeiten, zwar nicht bei den Latenzen, aber beim sequenziellen Durchsatz. Mit noch mehr Leistung (aber geringerer Speicherdichte) wäre X-NAND auch als TLC-, MLC- oder SLC-Variante möglich, so die Entwickler.

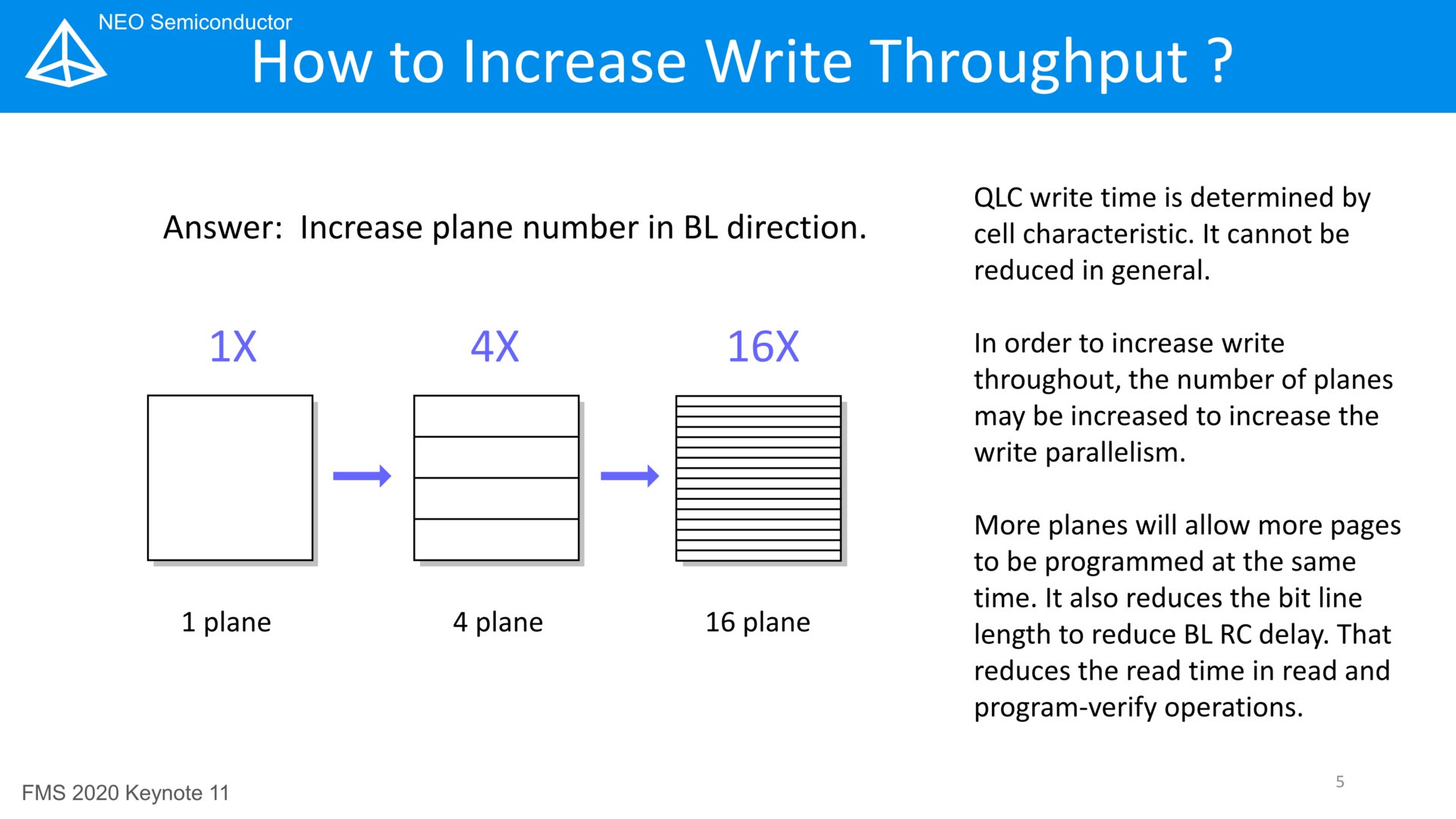

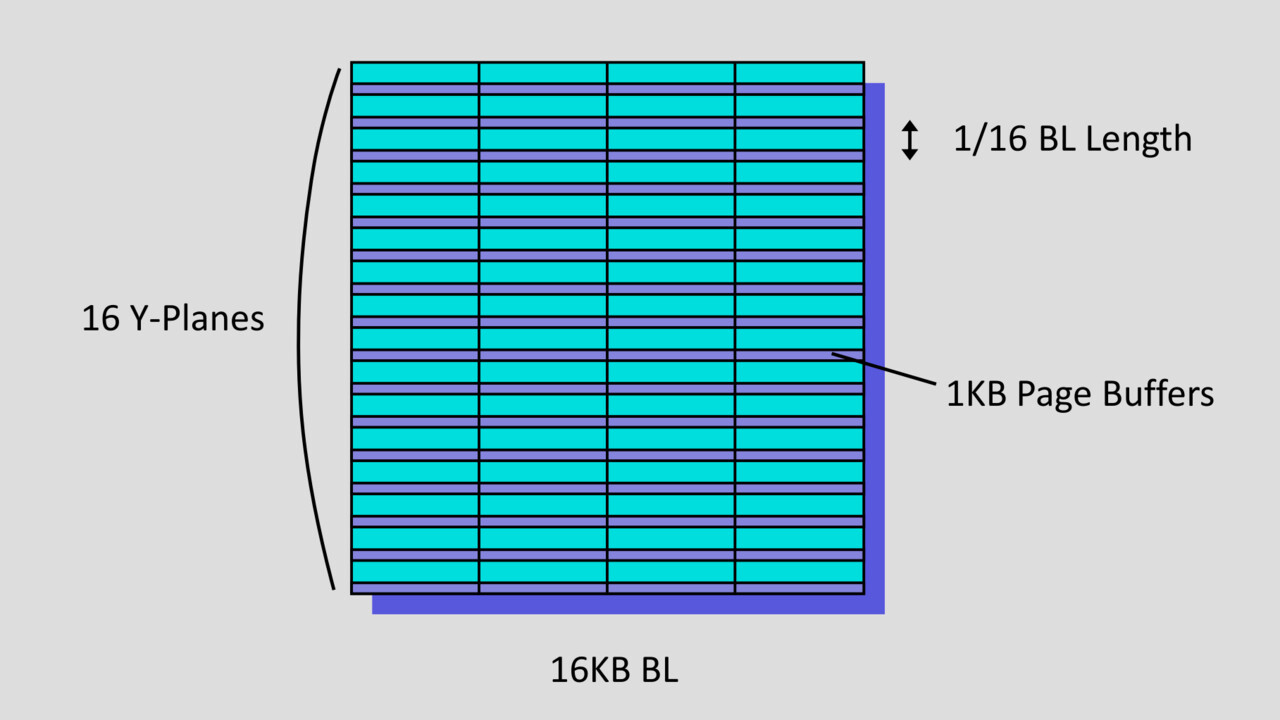

Der Schlüssel der Architektur von X-NAND liegt laut der Beschreibung in erhöhter Parallelität auf Chip-Ebene (Die). Schon jetzt wird NAND-Flash in mehrere Speicherbereiche (Planes) auf einem Die unterteilt, um durch mehr parallele Zugriffe die Leistung zu steigern. Doch bedeutet dies stets eine Erhöhung der Chipgröße, denn je mehr Planes vorhanden sind, desto mehr Verbindungen zwischen den zugehörigen Bitleitungen (Bit Line) und den Page-Buffers sind nötig. Statt jeder Bit Line einen Page-Buffer zuzuordnen, sieht die X-NAND-Architektur vor, dass ein Page Buffer gleich mehrere Bit-Lines Lesen/Schreiben kann. Die Zahl der Page-Buffer pro Plane wird somit reduziert, was Chipfläche spart.

Somit ist etwa ein 16-Plane-Design bei X-NAND sehr kompakt und besitzt kurze Bit-Lines für schnelle Datenübertragung. Ein theoretisches 16-Plane-Design mit herkömmlicher NAND-Architektur würde hingegen fast dreimal so groß ausfallen und entsprechend teuer sein, heißt es weiter. Dabei sei das X-NAND-Konzept auch mit Hinblick auf günstigere Chips mit weniger Planes denkbar, die Leistung soll dennoch immer höher liegen als bei konventioneller Architektur. Der X-NAND wird parallel im SLC- und QLC-Modus beschrieben (program), womit die Leistung dauerhaft hoch ausfalle, während bei bisherigem QLC-Flash die Leistung nach dem SLC-Cache etwa auf ein Zehntel einbricht.

Prognosen sind nichts ohne praktischen Beleg

Noch handelt es sich allerdings um reine Prognosen, denn ein funktionaler X-NAND-Chip wurde noch nicht präsentiert. NEO Semiconductor sei nun auf der Suche nach Entwicklungspartnern. Muster-Chips könnten von einem NAND-Hersteller rasch produziert werden, denn es ändere sich nur das Design, aber nicht das Herstellungsverfahren.

Zumindest für Aufmerksamkeit in der Branche wurde bereits gesorgt, denn NEO Semiconductor wurde im Rahmen der „Best of Show Awards“ des Flash Memory Summit 2020 für seinen X-NAND als innovativstes Flash-Speicher-Startup ausgezeichnet.

NEO Semiconductor

- X-NAND verwendet konventionelles NAND-Verfahren

- Keine Änderung an Zellen-/Array-Struktur

- Keine Änderung an Prozess/Technologie

- Keine zusätzlichen Herstellungskosten

- Keine langwierige Entwicklungszeit für Verfahren

NEO Semiconductor

- X-NAND ist eine reine Design-Lösung

- X-NAND kann in bestehende NAND-Verfahren implementiert werden

- Muster können rasch von NAND-Herstellern hergestellt werden

- Wir suchen nach Entwicklungspartnern

Wie jetzt bekannt wurde, hat NEO Semiconductor die beiden US-Patente 11056190 und 11049579 zum sogenannten X-NAND erteilt bekommen.

Nach wie vor ist aber nicht bekannt, ob einer der NAND-Flash-Hersteller die Technik lizenzieren und auf den Markt bringen wird.