IDF: Irwindale vs. Paxville DP vs. Paxville MP

Vor mehr als einer Woche ging das Intel Developer Forum Fall 2005 in San Francisco zu Ende und noch immer sind wir mit der Auswertung der gesammelten Informationen beschäftigt. Insbesondere über den bisher vernachlässigten Workstation- und Server-Bereich gibt es noch Einiges zu sagen.

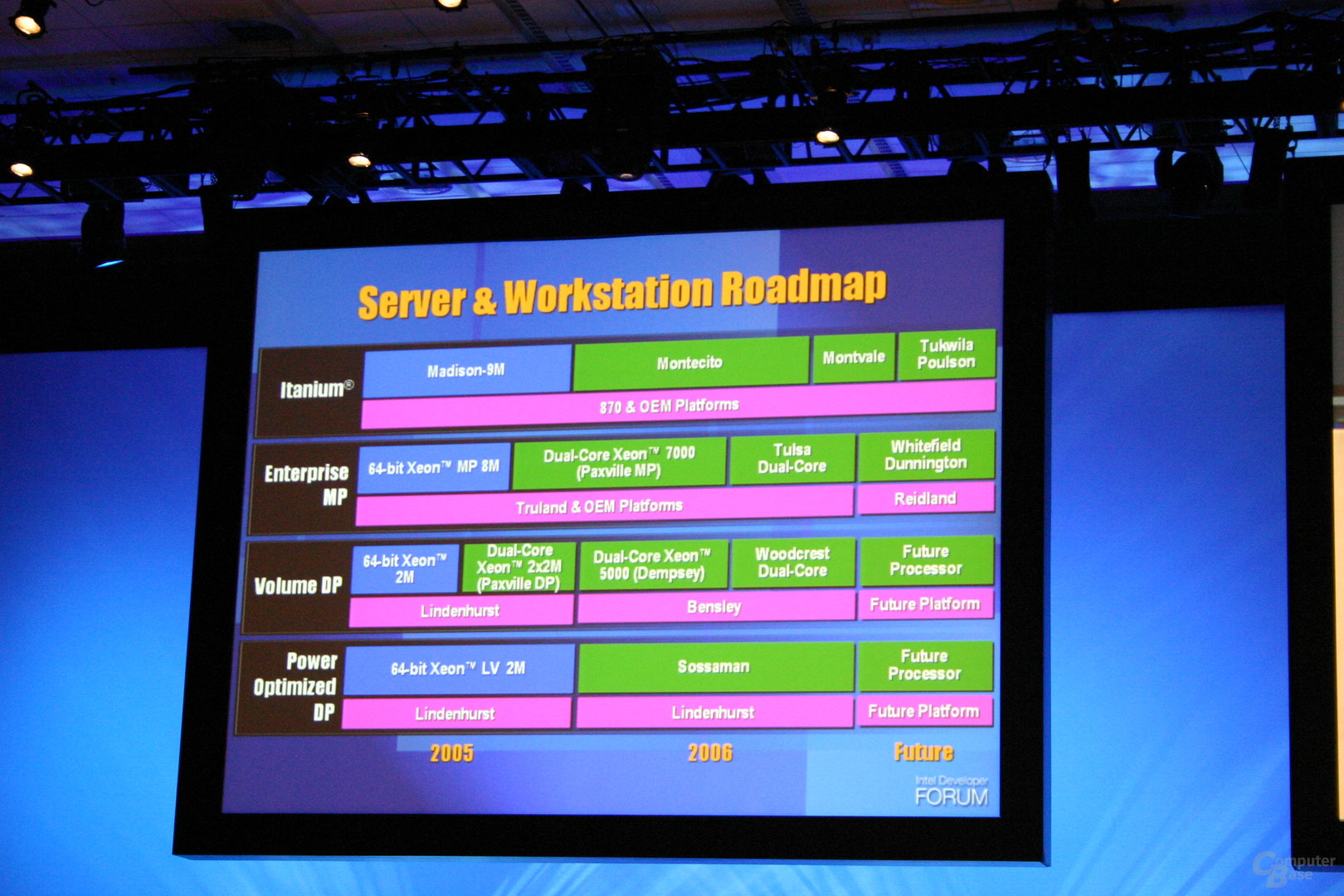

So zeigte Pat Gelsinger im Rahmen seiner Keynote eine aktualisierte Roadmap, mit der die ersten Dual-Core-Xeon-(MP)-Prozessoren nun ihre Codenamen abgelegt haben. So wird der kurzfristig in die Roadmaps aufgenommene 90 nm Paxville DP als Xeon 2x2M an den Start gehen. Die nächste Entwicklungsstufe im Xeon-Bereich für 2-Wege-Systeme, der in 65 nm gefertigte Dempsey, wird Xeon 5000 heißen.

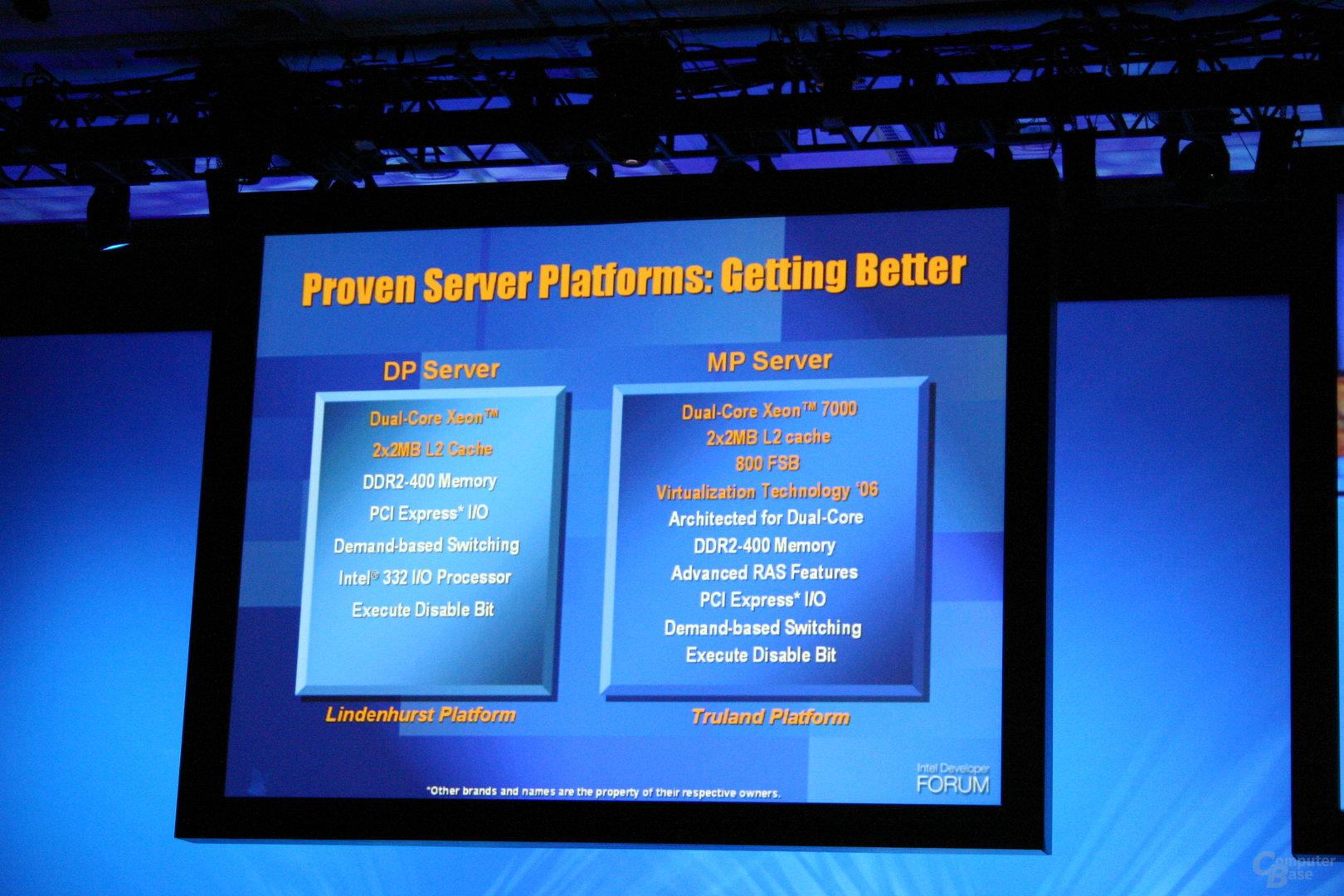

Die ersten Dual-Core-Xeon-Prozessoren werden bis auf den Xeon 5000 von den bestehenden Plattformen – Lindenhurst und Truland – mit Sockel 604 unterstützt werden. Mit Xeon 5000 wird Intel dagegen zusammen mit der Bensley-Plattform einen Wechsel auf den Sockel 771 (LGA) vollziehen. Vorher wird die Truland-Plattform mit E8500 (Twin Castle)-Chipsatz und Support für bis zu vier Prozessoren auf einen 800 MHz schnellen Frontside-Bus (der Chipsatz unterstützt dieser zwei) ausgehend von derzeitigen 667 MHz beschleunigt.

Leistungsmäßig machen die noch in diesem Jahr kommenden Dual-Core-Xeon (MP) Paxville DP und Paxville MP bereits eine gute Figur im Vergleich zu einem 2-Wege-Xeon DP-System mit 90 nm Irwindale-Kern (2 MB L2-Cache). Im ausgewählten Benchmark von SanGard benötigte das Irwindale-System (2 CPUs, HyperThreading) 51,06 Sekunden, der Paxville DP (2 CPUs, Dual-Core, HyperThreading) war nach 41,22 Sekunden fertig und das dicke Paxville-MP-System (4 CPUs, Dual-Core, HyperThreading) legte 26,14 Sekunden vor. Auch wenn Intel keine Angaben zu den Taktraten der Testsysteme machte, so fällt das Ergebnis des Paxville DP überraschend „schlecht“ aus. Hier macht sich offenbar der von beiden Prozessoren gemeinsam genutzte Frontside-Bus als Flaschenhals bemerkbar. Beim Paxville MP (Truland-Plattform) und der kommenden Xeon-DP-Plattform „Bensley“ hat man dieses Problem dank zweier unabhängiger Busse verringern können.