IDF: Geneseo für PCI-Express Co-Prozessoren

IBM und Intel sowie zahlreiche weitere Unternehmen haben das Konzept für einen verbesserten PCI-Express-Standard vorgestellt. Mit ihm reagieren die Unternehmen auf gestiegene Leistungsanforderungen durch Anwendungen wie sehr komplexe Grafikdarstellungen oder die Extensible Mark-up Language (XML).

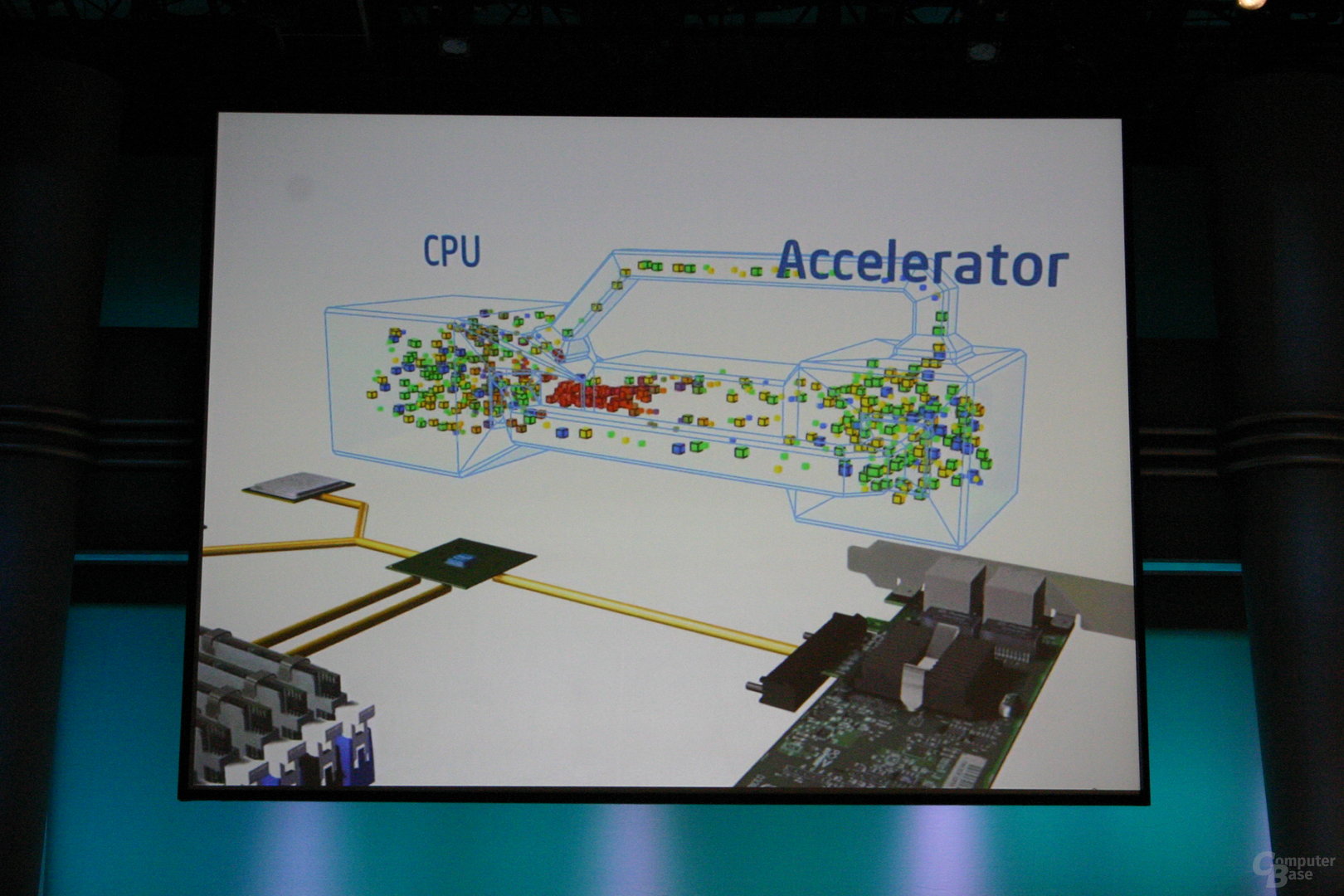

Der Entwurf mit dem Codenamen „Geneseo“ enthält einen Satz an Hardware- und Softwareerweiterungen des PCI-Express-Standards, die für eine schnellere Anbindung des Prozessors an andere Rechner-Komponenten sorgen. Außerdem bietet er Hardware-Entwicklern mehr Möglichkeiten beim Entwurf der Geräte. Zu den Verbesserungen gehören laut offizieller Ankündigung:

- New semantics for reduced signaling and synchronization overhead

- Improving speed and efficiency of access to memory through new semantics and traffic management

- Transaction ordering attributes to optimize ordering in memory hierarchy

- Dynamic frequency or voltage-imposed performance and power opterational modes

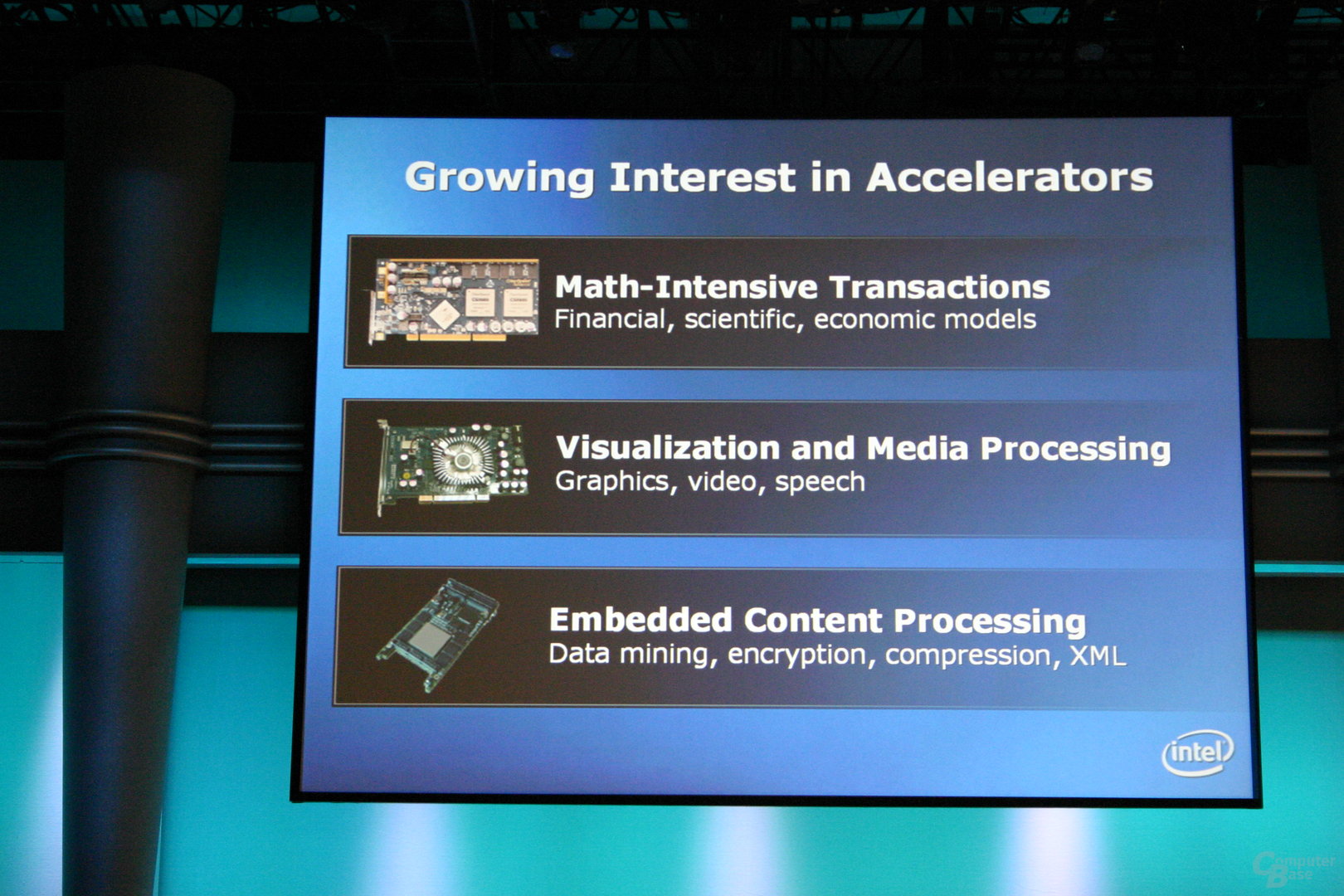

Zu den Anwendungen, die besonders von den Neuerungen profitieren, gehören komplexe Visualisierungen wie sie zum Beispiel in Wettersimulationen zum Einsatz kommen. Ebenso profitieren Applikationen, die komplizierte mathematische oder physikalische Fragestellungen lösen – wie etwa rechenintensive Finanzanwendungen. Auch die Ver- und Entschlüsselung von Kommunikationsdaten wird beschleunigt.

„IBM ist Mitbegründer eines neuen offenen Standards, mit dem Beschleuniger und Co-Prozessoren in Serverplattformen eingebunden werden können. Wie PCI-X, InfiniBand und PCI Express definiert diese Architektur einen neuen Standard, der normale Server für den Einsatz neuer oder gerade im Entstehen begriffener Anwendungen optimiert. Dazu gehören zum Beispiel Verschlüsselung, Visualisierung, XML und komplexe mathematische Modelle.“

Dr. Tom Bradicich, IBM Fellow und Chief Technology Officer für System x und BaldeCenter Server

Geneseso wird von einer Reihe von Unternehmen unterstützt. Dazu gehören Adaptec, Ageia., Altera, Broadcom, Celoxica, Cisco Systems, ClearSpeed, Dell, EMC, Emulex, HP, Integrated Device Technology., Lecroy, Linux Networx, LSI Logic, Mellanox, Myricom, NetEffect, Novell, nVidia, PLX, PMC-Sierra, QLogic, Sun Microsystems, Synopsys, Tektronix, Xambala, Xilinx sowie Xtreme Data.

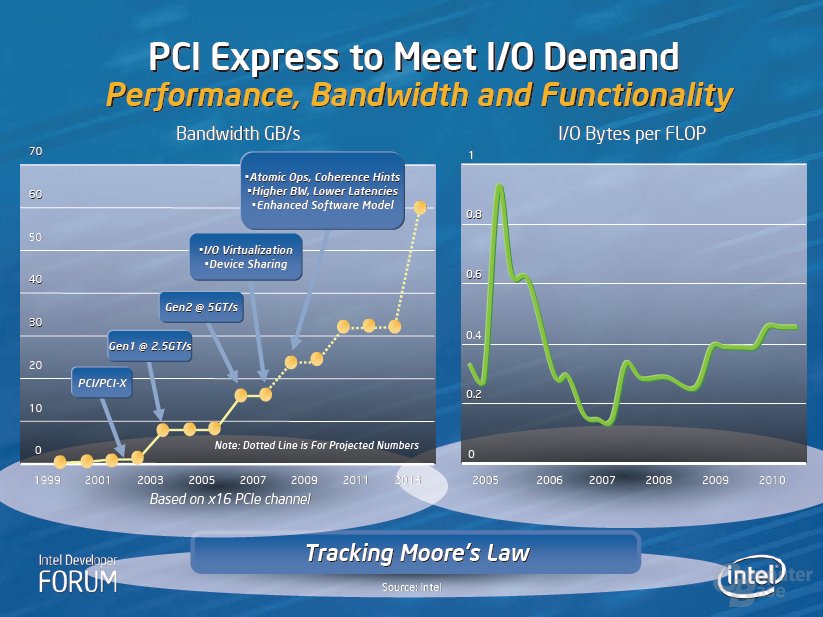

PCI Express 1.0 kam erstmals 2004 in PCs und Servern zum Einsatz. Die Einführung markierte den Wechsel von der bisher üblichen parallelen hin zu einer 2,5 GHz schnellen seriellen Datenübertragung innerhalb der Rechner – zum Beispiel zwischen Prozessor und Grafikkarte. Die Datenübertragung über den Parallel-Bus war bereits seit Beginn der PC-Ära der maßgebliche Standard. Seit 2004 wurden Millionen von Geräten mit dem PCI-Express-Bus ausgeliefert. PCI Express hat sich damit als wichtigste Technologie zur Datenübertragung zwischen den verschiedenen Bauteilen der einzelnen Rechner-Plattformen etabliert.

Intel reagiert mit Geneseo und der Freigabe seines Frontside-Bus für FPGAs (siehe getrennte Meldung) auf AMDs Torrenza-Programm. Statt auf PCI Express setzt Torrenza auf HyperTransport und ermöglicht damit das direkte Anbinden von Co-Prozessoren an den Prozessor, welcher in Form des Opterons in der aktuellen Generation über drei kohärente Links verfügt. Mit der nächsten Architektur wird sich diese Zahl auf vier Links bei voller 16-Bit-Konfiguration erhöhen. Während AMDs Ansatz mit dem 1 GHz (2 GHz DDR) schnellen HyperTransport-Bus auf Datenraten von 8 GB/s (4 GB pro Richtung) kommt und dieser Wert im kommenden Jahr mit HyperTransport 3.0 auf 20,8 GB/s bei 2,6 GHz weiter gesteigert wird, wird Geneseo basierend auf PCI Express 2.0 höchsten 16 GB/s (8 GB pro Richtung) erreichen. Die Lösung von Intel wird durch die Anbindung über den Chipsatz und den Frontside-Bus (selbst bei 1333 MHz werden hier maximal 10,4 GB erreicht) ausgebremst. Anderseits steht das PCI-Express-basierte Geneseo theoretisch einer bereiteren Zielgruppe – im Grunde auch Plattformen mit AMD-Prozessor – zur Verfügung. Torrenza-Lösungen – einzig und allein für die AMD64-Plattformen – sind dagegen für den HTX-Steckplatz, AMDs Sockel-F und später als Integration im Chipsatz oder dem Prozessorpackage selbst angedacht.

Weitere Informationen zu Geneseo sollen bald auf der Webseite des PCI Express Developer Network verfügbar sein. Einen Zeitraum für Geneseo nannte Intel nicht. Allerdings deuten einige Präsentationsfolien an, dass diese Technologie erst 2008 Einzug halten könnte. Bis dahin könnte die PCI-Express-Bandbreite gar auf 24 GB/s (mit 7,5 GHz Takt oder durch andere Techniken) gesteigert werden.