„Nehalem“-Generation mit Triple-Channel-DDR3?

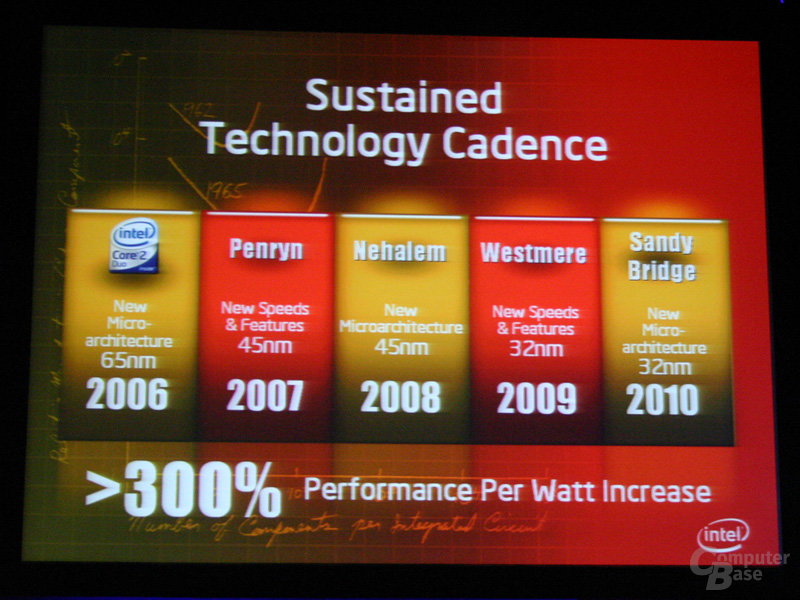

Während die Produktion bzw. Vermarktung der aktuellen Core 2 Duo/Quad/Extreme auf Basis der „Merom“-Generation auf Hochtouren läuft und der 45-nm-Refresh „Penryn“ samt Ablegern bereits Ende dieses Jahres ansteht, schreitet in den Laboren schon die Entwicklung der nächsten Prozessor-Generation mit dem Codenamen „Nehalem“ voran.

Nehalem – vor wenigen Jahren noch als Durchbrecher der magischen 10-GHz-Marke geplant – wird vermutlich Ende 2008 die Nachfolge der aktuellen Core-Mikroarchitektur antreten und verfügt erstmals, ähnlich zur Konkurrenz von AMD (K8 ff.), über einen integrierten Speichercontroller sowie ein serielles Punkt-zu-Punkt-Interface zum Chipsatz, welches aktuell unter dem Namen CSI gehandelt wird. Später soll sogar eine integrierte Grafik-Einheit auf den Prozessorsockel implementiert werden.

Neuesten Informationen zufolge wird das Topmodell (Codename „Bloomfield“) gar über einen Speicher-Controller für Triple-Channel-DDR3-SDRAM verfügen. In Verbindung mit „PC3-12800 (DDR3-1600)“-Speichermodulen liegt die maximale theoretische Bandbreite bei rund 38,4 GB/s und damit gegenüber dem heutigen Stand über 50 Prozent höher.

Des Weiteren sollen die neuen CPUs dynamisch skalierbar sein (Dynamically Scalable Architecture), um die einzelnen Prozessoren möglichst optimal an die anvisierten Marktsegmente (Mobile, Desktop, Server) anpassen zu können. Nach dem Baukasten-Prinzip könnte schließlich die Anzahl und Ausstattung an Prozessor-Kernen, Speicher-Controllern, I/O-Links oder auch die Größe der Caches variiert werden, ohne grundlegende Änderungen an der Architektur vornehmen zu müssen. Auch das von Intel aktuell „eingestampfte“ Hyper-Threading ist wieder im Gespräch, welches seiner Zeit der Netburst-Architektur durch die Erweiterung eines physikalischen Prozessor-Kerns in zwei logische Einheiten zu einer besseren Auslastung der Pipeline und der daraus resultierenden Effizienz verholfen hat.

Wir danken Simon Knappe

für das Einsenden dieser News.