Finale Spezifikationen für PCI Express 3.0

Die PCI Special Interest Group (PCI SIG) hat die finalen Spezifikationen von PCI Express 3.0 veröffentlicht. Wichtigste Neuerung ist eine im Vergleich zu PCI Express 2.0 (5 GT/s) abermals erhöhte Datenrate von 8 GT/s (Gigatransfers pro Sekunde). Durch einen neuen Leitungscode wird die Bandbreite zudem effizienter genutzt.

Während der bisher genutzte 8b10b-Code einen Overhead von 20 Prozent erzeugt, kommt bei PCI Express 3.0 ein 128b/130b-Code zum Einsatz, der dank einer knapp 25 Prozent höheren Effizienz die effektive Bandbreite im Vergleich zu PCI Express 2.0 verdoppeln soll. Pro Lane ergibt sich daraus eine Bandbreite von einem Gigabyte pro Sekunde und Richtung, einer mit 16 Lanes angebundenen Grafikkarte stünde somit eine Gesamtbandbreite von 32 GB/s zur Verfügung. Aber gerade auch über weniger Lanes angebundene Geräte wie Netzwerk-Controller oder Solid State Drives werden von der höheren Bandbreite profitieren können. Dabei bleibt der Standard jedoch abwärtskompatibel zu Geräten der ersten und zweiten PCIe-Generation.

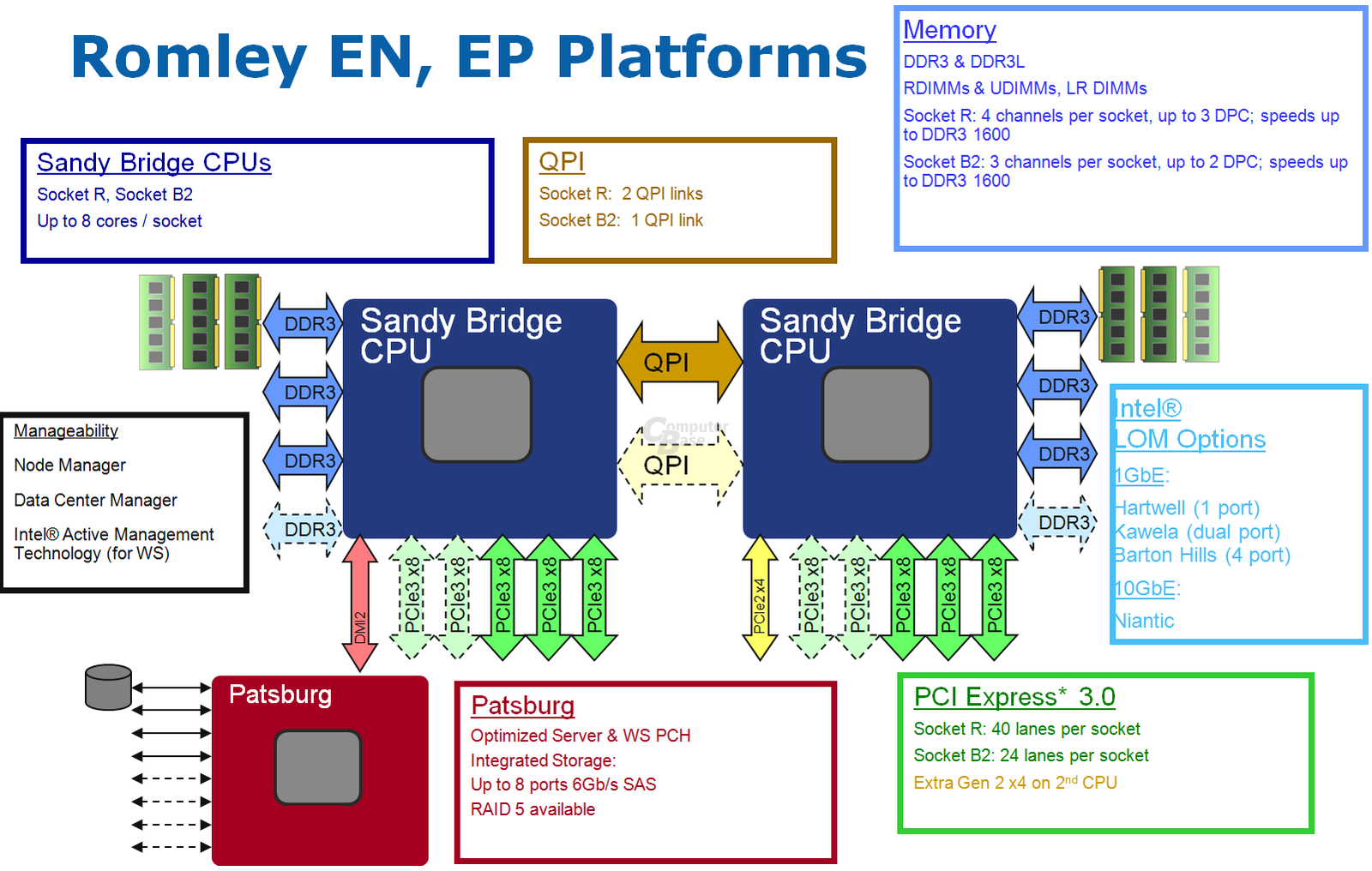

Als erstes werden vermutlich die kommenden Sandy-Bridge-E-Prozessoren mit vier bis acht Kernen für das Server-Segment den neuen Standard unterstützen. Die Romley-Plattform wird von Intel bereits in die entsprechende Richtung konzipiert, je nach Modell werden drei oder gar fünf PCI-Express-Slots mit jeweils acht Lanes verfügbar werden.